Samuel Vasconcelos Araújo

On the Perspectives of Wide-Band Gap Power Devices in Electronic-Based Power Conversion for Renewable Systems

# **Elektrische Energiesysteme**

Band 3

Herausgegeben von

Kompetenzzentrum für Dezentrale

Elektrische Energieversorgungstechnik

Fachgebiet Elektrische Energieversorgungssysteme

# On the Perspectives of Wide-Band Gap Power Devices in Electronic-Based Power Conversion for Renewable Systems

Samuel Vasconcelos Araújo

This work has been accepted by the faculty of electrical engineering / computer sciences of the University of Kassel as a thesis for acquiring the academic degree of Doktor der Ingenieur-wissenschaften (Dr.-Ing).

Supervisor: Prof. Dr.-Ing. habil. Peter Zacharias Co-Supervisor: Prof. Dr.-Ing. Andreas Lindemann

Defense day: 15th February 2013

Bibliographic information published by Deutsche Nationalbibliothek

The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie;

detailed bibliographic data is available in the Internet at http://dnb.dnb.de.

Zugl.: Kassel, Univ., Diss. 2013 ISBN 978-3-86219-486-5 (print) ISBN 978-3-86219-487-2 (e-book) URN: http://nbn-resolving.de/urn:nbn:de:000234870

© 2013, kassel university press GmbH, Kassel www.uni-kassel.de/upress

Printing Shop: Print Management Logistics Solutions, Kassel Printed in Germany

# **Foreword**

Power electronics is taking an increasingly important role in our daily lives, as it is the keystone not only to the efficient, but also cost effective and reliable use of electric energy in all possible fields of application; ranging from power supply from renewable energy sources to industry, IT and transportation. The first revolution in this field of technology came in the 1960s with the viability of switched-mode power conversion, owning to the emergence of BJTs operating at higher speeds. The development of MOSFETs and later IGBTs provided a further step in the direction towards higher frequency and power levels.

The advent of power devices based on silicon carbide (SiC) and gallium nitride (GaN) is currently pointing in the direction of a second revolution, where several paradigms concerning the design and performance of power conversion stages will be broken. Such giant leap will nevertheless require, aside from improvements in the chip technology itself, significant developments in device packaging, driving and also on the available materials and design strategies for passive filter elements. This work addresses some of these issues; presenting an overview of device structures, benchmarking and finally discussing issues at application level, with focus on converters for renewable energy sources.

This long path towards my thesis started back with my very first activities in the field of Power Electronics in 2005 in Brazil, as I was a graduation student in the Federal University of Ceará (UFC), working in the GPEC Laboratory. There I met my first mentors, Professor Sérgio Daher and Professor René Bascopé, and also other colleagues like Professor Carlos Gustavo Castelo Branco that gave me an outstanding support in my first steps. Professor Fernando Antunes not only supervised my graduation work, but also supported my scholarship for an exchange program that sent me to Kassel in 2004.

In Kassel, the great colleague Benjamin Sahan supervised my Master Thesis and also supported my application for a position in the former "Institut für Solare Energieversorgungstechnik" (ISET e.V.), now part from Fraunhofer IWES. There I had my first contact with the SiC technology in the beginning of 2008, while working with the colleagues Arno Zimpfer and Thorsten Bülo. Within two very exciting (and also exhausting) weeks, we tested samples from the manufacturer CREE in a prototype three-phase inverter under development for the company SMA Solar Technology AG. Aside from obtaining the "holy grail" (efficiency

record), I myself could still not grasp all the potentials of that new technology at that time.

With the establishment of the Centre of Competence for Distributed Electric Power Technology (KDEE) by Professor Peter Zacharias, I moved to the Department of Electric Power Supply Systems (EVS) in University of Kassel in 2009. Besides the important support not only from the department employees but also from the coworkers Benjamin Sahan and Mehmet Kazanbas, I could meet other outstanding colleagues that always helped me in the path of my work, like Christian Nöding, Lucas Menezes and Thiemo Kleeb.

On the other hand, the continuing cooperation with experienced engineers from SMA like Matthias Viktor, Henrik Wolf, Andreas Falk, Klaus Rigbers and Regine Mallwitz offered me a broad overview of trends and requirements in the field of photovoltaic power converters. In 2010 I could finally focus again on SiC devices thanks to a Joint Research Program funded by the European Center for Power Electronics e.V. (ECPE), where most of the literature research and device benchmarking could be performed.

During this project and also in the ensuing years, I could also count with the increasing support from several engineers in the companies Infineon Technologies AG (Peter Friedrichs, Gerald Deboy, Roland Rupp), CREE Inc. (John Palmour, Robert Callanan, Michael O'Neill), Semisouth Labs (Dieter Liesabeths, Nigel Springett) and Transic (Anders Lindgren).

The most important support came surely from Professor Peter Zacharias, who not only supervised my research activities throughout these years but was also an infinite source of interesting discussions and ideas. In my eyes it has been a unique privilege to interact with such a genius mind. I would also like to acknowledge my second supervisor, Professor Andreas Lindemann, for the interest and detailed revision of my work and also to Professor Axel Bangert and Professor Ludwig Brabetz for taking part in the examination board.

All these and many other persons helped me pave the way towards concluding my work. But without two "strong legs" I would not have been able to reach this goal. Such legs I owe to my parents, with their total dedication to my formation and also unconditional support towards my life goals, even it meant leaving my homeland.

Above all, I would like to thank God for giving me the aptitude, health and strength to pursue my dreams.

Kassel, April 24th 2013 Samuel Vasconcelos Araújo

# **Summary**

Although being known for more than a century, the application of wide band gap (WBG) materials have only recently gained momentum in the field of power electronics, driven by the increasing interest towards their outstanding material characteristics. The most important among then is the high breakdown field. This allows the construction of unipolar devices with very low specific chip resistance mainly characterized by very low conduction and switching losses, even at high blocking voltages.

A multitude of switch technologies based on Silicon-Carbite (SiC) and Gallium-Nitride (GaN) is currently being commercially introduced by manufactures around the globe. The concepts are ranging from traditional FET structures driven by a MOS interface or a PN-Junction, bipolar devices and even high-electron mobility transistors (HEMT). A detailed revision of the scientific literature will be performed in this work with the objective of providing a broad overview of possible approaches, along with inherent advantages and limitations. In addition to this, a benchmarking of several WBG-based devices technologies rated for 1200V and 1700V will be performed against their state-of-the-art Silicon-counterparts (Si).

Concerning the application of wide band gap devices, renewable energy systems are indeed one of the most promising fields given their high performance requirements, fast market expansion and high level of technical innovation. A significant cost reduction potential is for instance enabled by WBG devices due to smaller expenditure with magnetic filters and cooling, alongside higher efficiency levels. These aspects will be discussed in details in order to identify constraints and bottlenecks at application level with special focus on photovoltaic and wind power systems.

# Zusammenfassung

"Wide Band Gap" (WBG) Materialen sind, wie der Name bereits sagt, Halbleiterelemente mit einer höheren Energie der Bandlücke im Vergleich zum Silizium. Bereits seit mehr als einem Jahrhundert bekannt, erhält der Einsatz dieser Materialien jedoch erst seit Kurzem stärkere Beachtung. Dies liegt vor allem an zahlreichen Entwicklungen im Bereich der Materialverarbeitung, die eine deutliche Verbesserung der Materialqualität durch geringere Defektdichte ermöglicht haben.

## WBG Materialien - Eigenschaften und deren Applikation

Für die Leistungselektronik weisen Silizium Karbid (SiC) und Gallium Nitrid (GaN) hervorragenden Eigenschaften auf. Vor allem die erhöhte Durchschlagfestigkeit dieser Materialien ist zukunftsweisen, da hiermit eine Sperrfähigkeit nicht nur mit geringerem Materialeinsatz (kürzere Driftregion), sondern auch mit erhöhten Dotierungssätzen möglich ist. Somit ist der Aufbau von unipolaren und hochsperrenden Bauelementen mit stark reduzierten spezifischen Chipwiderständen möglich.

Ferner ist die Konzentration von intrinsischen Ladungsträgern bei ähnlichen Temperaturwerten um mehrere Größenordnungen geringer als Silizium. Folglich sind Betriebstemperaturen im Bereich von 600°C möglich. Eine weitere Eigenschaft stellt die Wärmeleitfähigkeit dar, welche bei SiC fast genauso gut ist wie bei Kupfer. Nicht zuletzt ist durch die erhöhte Driftgeschwindigkeit der Elektronen der Betrieb bei Funkfrequenzen möglich.

#### WBG-basierende Bauelemente

Bipolare Strukturen basierend auf Silizium dominieren derzeit die Anwendungen mit Sperrspannungen über 1000V. Ein Beispiel hiervon ist der Einsatz von IGBTs und PiN Dioden sowohl in Antriebsumrichtern der Industrie und dem Verkehr, als auch in der Photovoltaik und Windkraftanlagen.

Im Vergleich hierzu bietet Siliziumkarbit die Möglichkeit, unipolare Strukturen, **MOSFETs** Schottky-Dioden, mit nur einem Bruchteil wie und des aufzubauen. Solche Strukturen sind nicht der Chipwiderstands Rekombinationszeit und Durchflutung von Majoritätsladungsträger wie bipolare Bauelemente betroffen. Daher ist eine deutlich bessere dynamische Performance erreichbar. Bei höheren Spannungen sind zudem weitere bipolare Strukturen auf SiC-Basis, wie BJTs, Thyristor und PiN Diode, einsetzbar.

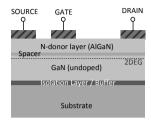

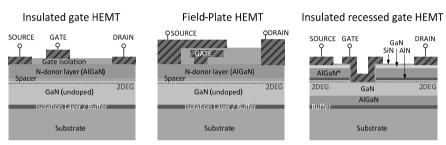

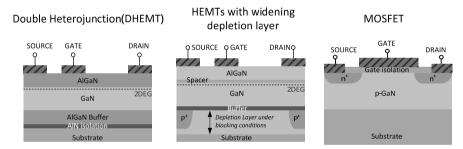

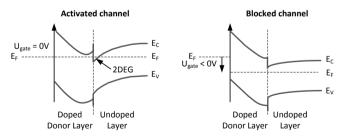

Im Gegensatz zum SiC sind für GaN weniger unterschiedliche Strukturen vorhanden. Ein erster Grund dafür ist das Fehlen eines nativen Oxids, wie SiO<sub>2</sub>. Daher können MOSFETs und IGBTs nur mit erhöhtem Aufwand hergestellt werden. Weiterhin sind P-dotierte Bereiche von geringerer Löcherbeweglichkeit betroffen und die Dotierungskonzentration von N-Bereichen ist begrenzt. Nicht zuletzt ist in der Regel ein leitender Kanal auf Basis von AlN durch die Epitaxie aufgebaut, sodass der Stromfluss in horizontaler Richtung erfolgen muss. Folglich kommen hier nur laterale Strukturen wie der "High-electron mobility"-Transistor (HEMT) in Frage. Aufgrund der oben erwähnten Einschränkungen ist der Einsatz von GaN-Bauelemente eher in geringeren Spannungsklassen geeignet.

Eine detaillierte Übersicht aus der Fachliteratur wird in dieser Arbeit zusammen mit der Identifizierung von inhärenten Vorteilen und Einschränkungen der einzelnen Ausführungsmöglichkeiten vorgestellt. Ein Benchmarking ausgewählter Bauteile wird schließlich auf Basis experimenteller Ergebnisse gegenüber dem Stand der Technik von Silizium-Bauelementen durchgeführt.

#### Applikation von WBG-basierenden Bauelementen

Mit den zuvor erwähnten Eigenschaften von WBG Bauelementen sind zukunftsweisende Bauteile für die Leistungselektronik erreichbar. Die Senkung der Verluste, Erhöhung der Schaltfrequenz und Betrieb bei höheren Junction-Temperaturen seien lediglich mögliche Beispiele. Hinsichtlich der Anwendung solcher Bauelemente sind erneuerbare Energien in der Tat die vielversprechendsten Gebiete, besonders aufgrund ihrer hohen Leistungsanforderungen, schneller Marktexpansion und des hohen technischen Innovationsgrades.

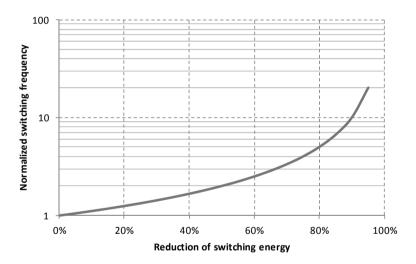

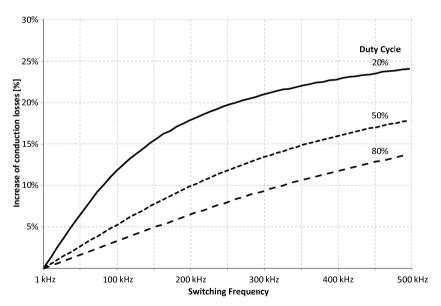

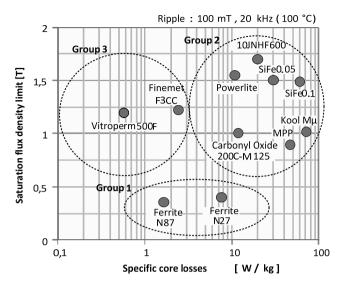

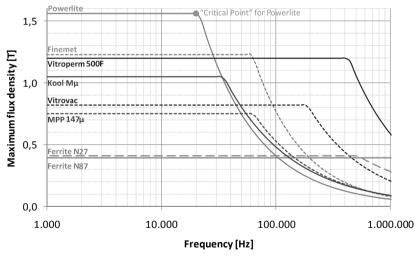

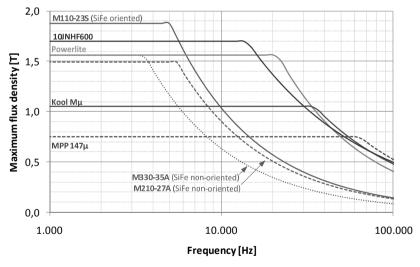

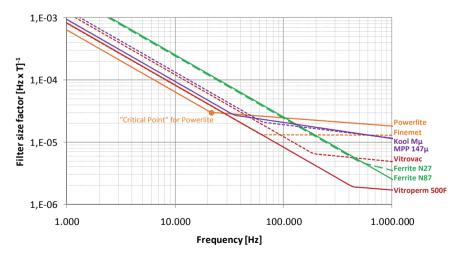

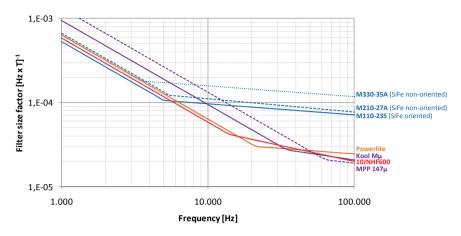

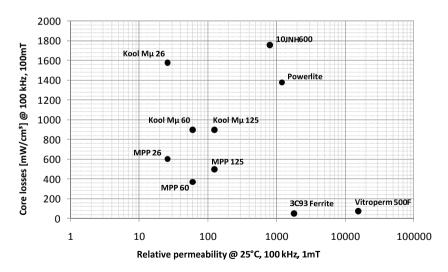

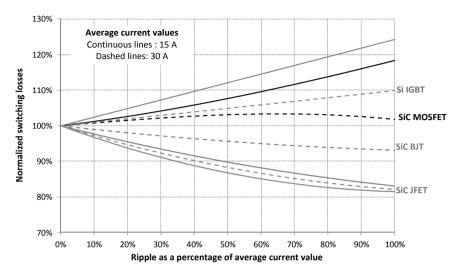

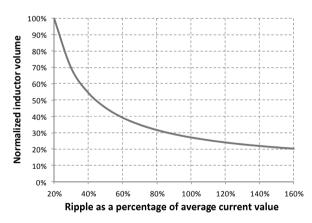

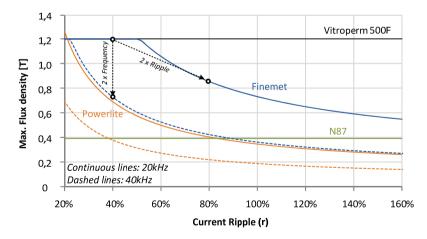

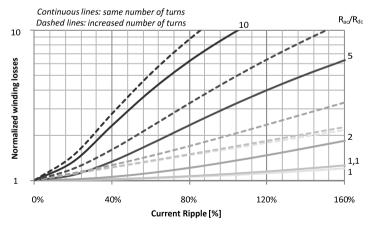

Auf Applikationsniveau hat die Erhöhung der Schaltfrequenz eine <u>Reduzierung von passiven Filterelementen</u> direkt als Folge. Mit den aktuell vorhandenen SiC Schaltern ist eine Reduzierung der Schaltenergie um bis zu 75% gegenüber der neusten Si-IGBTs möglich. Als Folge ist eine Vervierfachung der Schaltfrequenz erreichbar. Eine weitere Senkung um 50% bietet sich durch eine Erhöhung der Schaltflanken, wobei Aspekte wie die Isolationsfestigkeit, Oszillationen und EM-Störungen zunehmend kritisch werden. Die tatsächliche Senkung des Bauvolumens der Filterelemente ist dennoch stark von den Eigenschaften der Kernmaterialen beeinflusst. Heutige Materialien für den Einsatz bei 16kHz sind z.B. für den Betrieb oberhalb 50kHz nicht geeignet. Folglich sind die weitere Entwicklung und der Einsatz von hochwertigen Kernmaterialen erforderlich. Eine Übersicht über vorhandenen Materialen und deren Anwendungsbereiche werden in Rahmen dieser Arbeit analysiert und vorgestellt. Eine weitere untersuchte Alternative zur

Einsparung von Filterelemente ist der Betrieb mit höherer Stromwelligkeit, da gleichzeitig eine Senkung der gesamten Schaltverluste möglich ist. Dies lässt sich durch die Tatsache erklären, dass die Einschaltverluste eindeutig höher als die Ausschaltverluste sind.

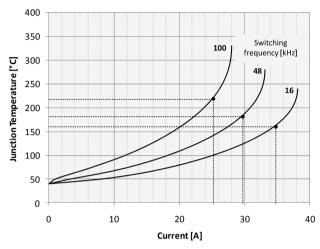

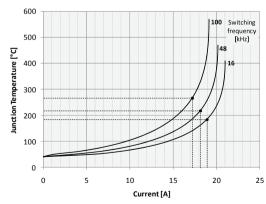

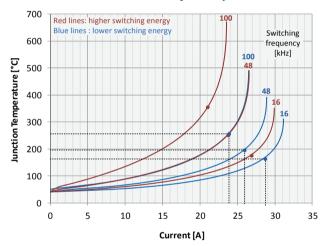

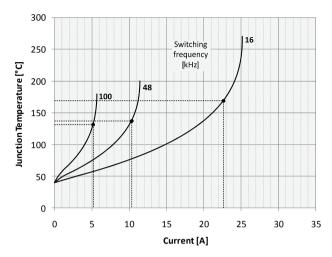

Einsparungen im Bereich der Kühlung können durch zwei unterschiedliche Strategien erreicht werden. Zunächst können die WBG Bauelemente bei deutlich höheren Junction-Temperaturen betrieben werden. Wegen der Erhöhung der Durchlassverluste mit zunehmender Temperatur ist aber zu erkennen, dass eine optimale Chipausnutzung, d.h. maximale Strombelastbarkeit, eher unter 250°C liegt. Interessanter ist daher die Senkung der Verluste, die durch die geringere Chipfläche natürlich erreichbar ist.

Wegen der noch hohen Materialkosten spielt der geringere Aufwand bei der Chipfläche eine wesentliche Rolle in der Wettbewerbsfähigkeit von WBG Bauelemente. Einsparungen von über 50% sind dank des geringeren spezifischen Chipwiderstandes möglich. Weitere Einsparung können nicht nur durch Verbesserung der Wärmespreizung im Betrieb bei höherer Verlustdichte, sondern auch mit einer weiteren Erhöhung der Flankensteilheit beim Schalten und folglich durch geringere Schaltenergie erreicht werden.

## Mögliche Einsparungen in Umrichter für erneuerbaren Energien

WBG-Bauelemente ermöglichen ein signifikantes Kostensenkungspotenzial durch geringeren Aufwand bei magnetischen Filtern und Kühlung, sowie höheren Wirkungsgraden. Es lässt sich dadurch eine klare Entwicklung in Richtung einer höheren Leistungsdichte zeigen.

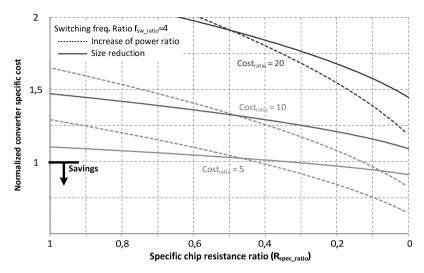

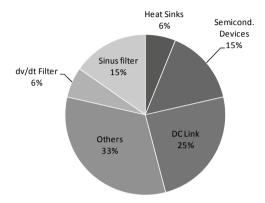

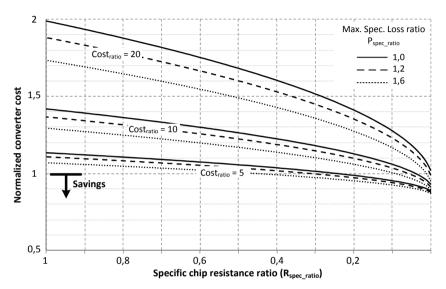

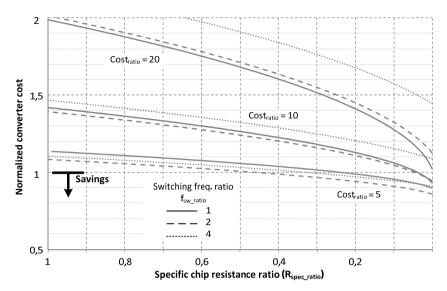

Durch die Analyse der Kostenstruktur von Umrichter für Photovoltaik und Windkraftanlagen und unter Berücksichtigung der oben erwähnten Einsparpotenziale sind zwei Szenarien untersucht worden: die Erhöhung der Nennleistung bei gleicher Baugröße, sowie die Senkung der Baugröße bei fester Nennleistung. Die erste Methode ist für modulare Systeme wie Photovoltaik besser geeignet.

Allgemein ist zu erkennen, dass die höheren spezifischen Kosten von WBG-Materialen immer noch eine überwiegende Rolle in den Einsparungspotenzialen spielen. Zum Beispiel erhöhen sich mit zunehmenden Schaltfrequenzen auch der Aufwand in Bezug auf die Chipfläche. Daher sind höhere Schaltfrequenzen unter aktuellen Bedingungen nur sehr begrenzt attraktiv. Nur wenn die Chipfläche-Kosten von WBG-Materialen um einen Faktor 5 gegenüber denen von Si größer werden können, sind Kosteneinsparungen von 5% bis 10% zu erwarten.

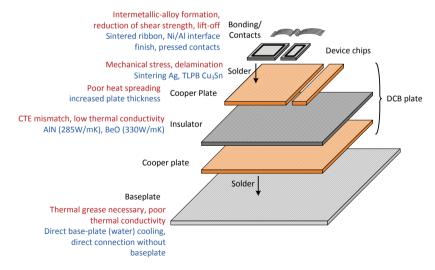

Zusätzliche Einsparungen können dann nicht nur durch geringere Halbleitermaterialkosten, sondern auch durch eine verbesserte Ausnutzung der WBG Technologie erzielt werden. Dafür sind weitere Entwicklungen im Bereich Aufbau- und Verbindungstechnik (AVT) dringend erforderlich, um z.B. eine Erhöhung der Verlustdichte und Schaltsteilheit zu verwirklichen.

## Experimenteller Einsatz von WBG Bauelemente

Alle experimentellen Untersuchungen in dieser Arbeit fokussieren lediglich auf SiC Bauelementen, da zum Zeitpunkt der Arbeit keine GaN-Halbleiter mit geeigneten Sperrspannungen vorhanden und lieferbar waren. Mit verschiedenen getesteten Schaltungen und Bauelementen war zunächst zu erkennen, dass es bereits mit der Kombination von neusten Si-Schalter und SiC-Dioden sehr hohe Wirkungsgrade erreichbar sind. Es besteht also wenig Raum zur Verbesserungen in diesem Aspekt.

Eine sehr interessante Aussicht besteht darin, die Betriebsspannungen von Hochleistungsumrichter zu erhöhen, um hierdurch Einsparungen auf Systemebene zu erreichen. Besonders große PV-Anlagen sind hiervon betroffen. Bei solchen Bedingungen bieten SiC-Hochspannungsbauelemente einen klaren Vorteil gegenüber der Si-Technologie, insbesondere in Bezug auf die Schaltperformance.

Schlussendlich ist auch zu erkennen, dass derzeit noch keine Aussage möglich ist, welche Schalterstruktur den Markt zeitnah dominieren wird. Grund dafür sind die sehr unterschiedlichen Eigenschaften der untersuchten Bauelemente, welche eine Palette von Steuerungsanforderungen (Selbstleitend, Strom- und Spannungsgesteuert) und Zuverlässigkeitsmerkmale (Gate-Oxid Lebensdauer, bipolare Degradation) aufweisen.

# **Table of Contents**

| Foreword                                                  | 5  |

|-----------------------------------------------------------|----|

| Summary                                                   | 7  |

| Zusammenfassung                                           | 8  |

| 1 Introduction                                            | 15 |

| 1.1. Motivation of the work                               |    |

| 1.2. Structure of the work                                |    |

| 2 STATE-OF-THE-ART POWER DEVICES BASED ON WBG             |    |

| 2.1. SiC-MOSFETs                                          |    |

| 2.1.1. Device structure and characteristics               |    |

| 2.2. SiC-JFETs                                            | 28 |

| 2.2.1. Device structure and characteristics               | 29 |

| 2.2.2. Operation & Driving                                |    |

| 2.3. SiC-BJTs                                             |    |

| 2.3.1. Device structure and properties                    |    |

| 2.3.2. Operation & Driving                                |    |

| 2.4. GaN devices                                          |    |

| 2.4.1. Device structure and characteristics               | 52 |

| 2.4.2. Operation & Driving                                | 57 |

| 3 EXPERIMENTAL INVESTIGATION AND BENCHMARKING             |    |

| 3.1. Experimental investigation                           | 59 |

| 3.1.1. Gate characteristics                               | 61 |

| 3.1.2. Device capacitances                                | 66 |

| 3.1.3. Forward characterization                           |    |

| 3.1.4. Switching behavior characterization                | 68 |

| 3.1.5. Operation at higher speeds                         |    |

| 3.2. Benchmarking of investigated devices                 |    |

| 3.2.1. Static behavior and temperature dependence         | 81 |

| 3.2.2. Dynamic behavior                                   |    |

| 3.2.3. Performance benchmarking                           | 84 |

| 3.2.4. Benchmarking considering maximum achievable switch |    |

| 3.2.5. Driving issues                                     |    |

| 3.2.6 Freewheeling-related issues                         | 89 |

| 4     | PPLICATION OF WBG DEVICES: SWITCHING FREQUENCY AND PASSIVE         |      |

|-------|--------------------------------------------------------------------|------|

| FILTE | ELEMENTS                                                           |      |

| 4.1   | Switching speed and related issues                                 | . 93 |

| 4.1   | Critical aspects                                                   | . 93 |

| 4.1   |                                                                    |      |

| 4.2   | Effects on magnetic components                                     |      |

| 4.2   |                                                                    |      |

| 4.2   | 1 0 0 0 0 1                                                        |      |

| 4.2   |                                                                    | 109  |

| 5     | PPLICATION OF WBG DEVICES: COOLING EFFORT AND OTHER THERMAL        |      |

| ASPE  | 'S                                                                 | 115  |

| 5.1   | Thermal related issues                                             |      |

| 5.1   | . Maximum temperature and thermal runaway                          | 115  |

| 5.1   | C. Other limitations                                               | 119  |

| 5.1   | C. Overload capability                                             | 122  |

| 5.1   | Loss density and dissipation                                       | 122  |

| 5.2   | Cooling effort                                                     | 123  |

| 5.2   | Savings with operation at high junction temperature                | 123  |

| 5.2   | Savings with reduction of losses                                   |      |

| 6     | PPLICATION OF WBG DEVICES: CHIP AREA EXPENDITURE                   |      |

| 6.1   | Analysis considering only conduction losses                        | 129  |

| 6.2   | Analysis considering conduction and switching losses at same       |      |

| SW    | ching frequency                                                    | 131  |

| 6.3   | Analysis considering conduction and switching losses for different |      |

| va    | es of switching frequency                                          | 135  |

|       | NALYSIS ON POTENTIAL SAVINGS                                       |      |

| 7.1   | Photovoltaic inverters operating at 16 kHz with IGBTs              |      |

| 7.1   |                                                                    |      |

| 7.1   | • •                                                                |      |

| 7.1   |                                                                    |      |

| 7.2   | High power back to back converter                                  |      |

| 7.3   | Additional savings                                                 |      |

| 7.3   |                                                                    |      |

| 7.3   |                                                                    |      |

|       | KPERIMENTAL INVESTIGATIONS                                         |      |

| 8.1   | Effect of different semiconductor configurations on a single stage |      |

|       | ovoltaic inverter [59]                                             | 161  |

| 8.1   |                                                                    |      |

| 8.1   | 1 0,                                                               |      |

| 8.1   | * 9                                                                |      |

| 8.2   | Circuits suitable for normally-on SiC JFETs [55], [56]             | 166  |

| U.2   |                                                                    |      |

| 8.2     | 2.1. Experimental results                                            | 167   |

|---------|----------------------------------------------------------------------|-------|

| 8.2     | 2.2. Conclusions                                                     |       |

| 8       | 3. Photovoltaic inverters for 1500V system voltage [54], [57]        | 168   |

| 8       | 3.1. Optimal input voltage range                                     |       |

| 8       | 3.2. Topology selection                                              | 171   |

| 8       | 3.3. Experimental results                                            | 172   |

| 8       | 3.4. Conclusions                                                     |       |

| 8.4     | 4. Highly compact step-up converter using SiC-BJTs [290]             | 175   |

| 8.4     | 4.1. Driving circuit: alternative configuration for lower losses     | 175   |

| 8.4     | 4.2. Input filter inductor: maximum size reduction with new mate 177 | rials |

| 8.4     | 4.3. Experimental results                                            | 178   |

| 8.4     | 4.4. Conclusions                                                     | 180   |

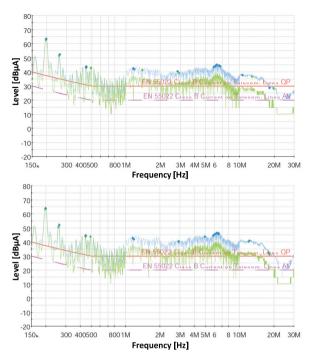

| 8       | 5. Switching speed and conducted interference [66]                   | 180   |

| 8       | 5.1. Experimental investigation                                      | 181   |

| 8       | 5.2. Conclusions                                                     | 184   |

| 9       | CONCLUSIONS                                                          | 185   |

| 9       | 1. Device level                                                      | 185   |

| 9.2     | 2. Application level                                                 | 186   |

| Referer | nces                                                                 | 190   |

| Abbrev  | riations and symbols                                                 | 220   |

| List of | the Figures                                                          | 228   |

| List of | the tables                                                           | 236   |

# 1 Introduction

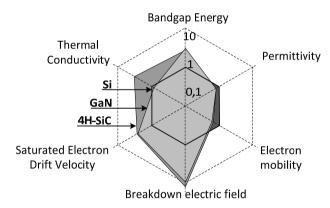

Band gap is defined as the amount of energy (normally measured in eV, corresponding to 1,6 x 10<sup>-19</sup>J) required to move one electron from the valence to the conduction band, being a key property for drawing the boundaries between conductors, semiconductors and insulators. The so-called wide band-gap (WBG) semiconductors have band gap values higher than Silicon (Si), with Silicon Carbide (SiC) and Gallium Nitride (GaN) being the most significant materials in the field of electronics. Some of the most interesting properties of these materials are normalized against Si and presented in the graph below with logarithmic scale, followed by a brief explanation in the following table.

Fig. 1: Key-features of semiconductor materials normalized to the values of Si on a logarithmic scale.

From the below listed properties, it is possible to identify two main general prospects regarding the performance of WBG-based devices, as explained in the following items.

Table 1 – Explanation and technical potential of selected material properties.

| Property [unit]                                                                                                                                                                                | Explanation                                                                                                                 | Technical importance                                                                                                                                      |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Critical electric field (E <sub>crit</sub> ) [V/m]                                                                                                                                             | Maximum electrical<br>field intensity before<br>the onset of avalanche<br>breakdown                                         | Higher critical field capability<br>allows simultaneously shorter drift<br>widths and higher doping<br>concentrations, thus reducing<br>device resistance |  |

| Relative permittivity $(\epsilon_r)$                                                                                                                                                           | Permittivity to electrical field                                                                                            | Factor necessary for determining<br>the applicable doping<br>concentration of drift regions given<br>a certain field limit and layer width                |  |

| Electron mobility (µn) [m²/Vs]                                                                                                                                                                 | Relation between the electron speed and applied electrical field. Strongly affected by temperature and doping concentration | Directly affecting the resistivity of a given semiconductor area                                                                                          |  |

| Electron saturated drift velocity (v <sub>sat</sub> ) [m/s]                                                                                                                                    | Maximum electron speed for an upper limit of electrical field                                                               | Affecting the semiconductor device maximum limit of speed of response and frequency, fundamental for RF/microwave applications                            |  |

| Thermal conductivity (λ) [W/m·K]                                                                                                                                                               | Heat conduction capability                                                                                                  | Higher power dissipation capability per chip area, reduction of chip size, increase of power density.                                                     |  |

| Intrinsic concentration of free inherent carriers, at concentration $(n_i)$ [cm <sup>-3</sup> ] Volumetric concentration of free inherent carriers, at 300K. Strongly affected by temperature. |                                                                                                                             | Directly related to high temperature operation capability due to lower leakage current.                                                                   |  |

#### Low losses at high blocking voltages

The most notable characteristic of WBG materials is the very high critical field strength ( $E_{crit}$ ); more than 10 times the value of silicon. As a consequence, the width of the drift-layer ( $w_{drift}$ ) can be reduced by a similar order of magnitude for comparable values of breakdown voltages ( $V_{br}$ ), as deduced by the equation below.

$$V_{br} = 0.5 \cdot W_{drift} \cdot E_{crit} \tag{1}$$

At the same time, the doping concentration  $(N_D)$  can be increased approximately 100 times under the above cited conditions. Such relation can be indirectly asserted with the equation below, with q being the electron charge.

$$q \cdot N_D = \varepsilon_o \cdot \varepsilon_r \cdot E_{crit} / W_{drift}$$

(2)

For unipolar devices, the impact of such characteristic on theoretical specific onstate resistance ( $R_{on\_sp}$ ) can be evaluated by division between width of the driftzone and respective conductivity. Such relation is demonstrated in the equation below, having as parameters the electron mobility ( $\mu_n$ ) and doping concentration ( $N_D$ ).

$$R_{on\_sp} = W_{drift} / (q \cdot \mu_n \cdot N_D)$$

(3)

By rearranging the equation above with relations given in the Poisson equation, the dependence on breakdown voltage and material properties like relative permittivity  $(\epsilon_r)$  is obtained below [69]. In reality, the exponent applied to the breakdown voltage is normally higher, reaching approximately 2,5 due to the doping dependence on the factors  $\mu_n$  and  $E_{crit}$  [70]. Thus independent of the employed material, the relative dependence to the breakdown voltage is practically the same; the major difference lies on the absolute value achievable with each one of them.

$$R_{on spec} = \left(4 \cdot V_{br}^{2}\right) / \left(\varepsilon_{o} \cdot \varepsilon_{r} \cdot \mu_{n} \cdot E_{crit}^{3}\right) \tag{4}$$

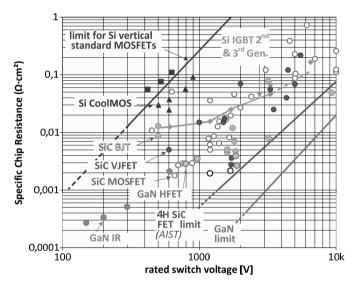

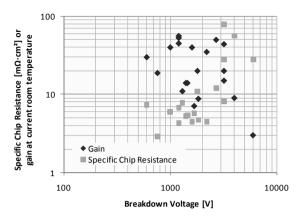

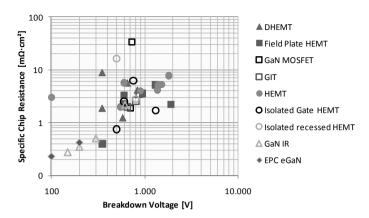

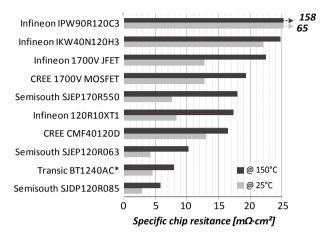

The denominator of the equation above with the exclusion of the permittivity of vacuum is normally named the "Baliga figure of merit" (BFoM). Considering the material constants given in [71] the value of BFoM and hence the specific chip resistance deduced for unipolar devices based on SiC and GaN result in theory in values respectively 488 and 2414 lower than Si. Such relations are employed to trace the theoretical technology limit curves, as presented in Fig. 2.

Such low value of specific chip resistance can from one side be translated in a significant reduction of the required chip area for a given current rating, what would be extremely favorable for the economic viability of the devices with the

referred new materials. In addition to this it is possible to assert that on-state losses (conduction losses) under the consideration of similar values of specific loss limits will also be accordingly reduced, enabling higher levels of efficiency.

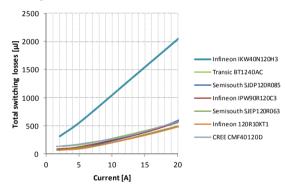

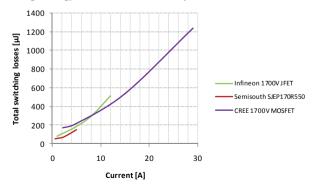

At least but not last, the possibility of building high voltage blocking devices without conductivity modulation offers the attractive possibility of increasing the switching speed and thus reducing the switching losses.

Fig. 2: Specific chip resistance as a function of the blocking voltage for different semiconductor materials and switch technologies.

# • High temperature operation

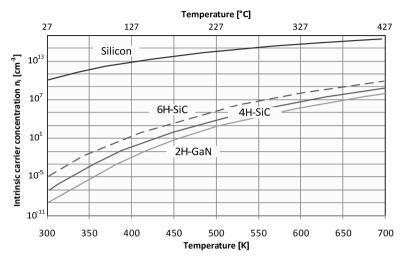

The concentration of intrinsic carriers (n<sub>i</sub>) and its exponential dependence on the temperature is a limiting factor for high junction temperature operation mainly due to two reasons. Firstly, in case the concentration of intrinsic carriers becomes larger than the one from the dopant carriers, incorrect operation of the device may occur. Secondly, the leakage current of a blocked junctions is practically exponentially dependant on the intrinsic carrier concentration, so that losses under blocking conditions become significant.

Given their superior bandgap energy, the concentration of intrinsic carriers in WBG materials is several orders of magnitude lower than Si, as can be observed in the graphic below. Hence, operational temperatures as high as 600°C are

achievable for WBG devices, while 200°C is often regarded as the limit for Si devices[72].

Fig. 3: Intrinsic carrier concentration depending on the temperature.

A higher limit for the maximum junction temperature has several technical advantages. Not only can the devices be applied under extreme harsh ambient conditions (military and space applications) but also the cooling expenditure can be significantly reduced. The overload capability along with loss density per chip is correspondently increased, leading to a possible reduction of the chip size. Exclusive to SiC is the superior thermal conductivity, which is almost as high as the one from cooper and more two times the value from Si and GaN.

# 1.1. Motivation of the work

Following several years of intensive research, 1200V-rated SiC switches have been newly introduced in the market, with some 1700V devices already available as engineering samples. Meanwhile, GaN devices are for the time being mostly limited to voltage levels below 600V. A multitude of publications have so far identified several outstanding properties of these devices, like the small chip area value with low equivalent resistance and very fast switching behavior.

In face of such diversity of possible alternatives, it is possible to observe in general the lack of a broad and unified overview of existing device technologies alongside a parametric experimental investigation of electrical properties. Without such result results, it is practically impossible to perform a comparison and benchmarking of technologies in respect of their performance.

On the other hand, investigations at application level have so far relied on a simple exchange of existing devices and demonstration of possible increase of efficiency levels. Important aspects at application level like operation at higher switching speeds and related side-effects along with benchmarking of possible gains besides efficiency have also not been widely addressed.

In the path towards their extensive application, it is therefore necessary to fully understand not only the performance potentials but also limitations at both device and system levels. Due to their inherently higher specific costs, it also becomes mandatory to break some existing paradigms in the design and construction of power electronics systems, especially considering the possibility of operating with low losses even under high blocking voltages.

One of the most promising fields of application of these devices includes power conversion systems for renewable energy sources due to their fast growing rate and high level of technical innovations. They will offer a possible basis for the expansion of production capacity and technology maturation, before their introduction on broader market segments.

## 1.2. Structure of the work

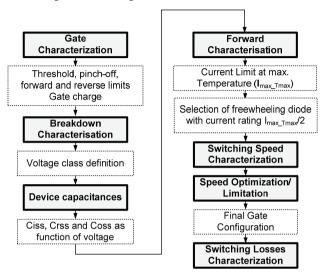

In a first step, the key properties of existing switch technologies based on SiC and GaN will be presented. A new benchmarking methodology based on experimental results with SiC devices will afterwards be proposed and performed in Chapter 3 in order to identify the most attractive technologies.

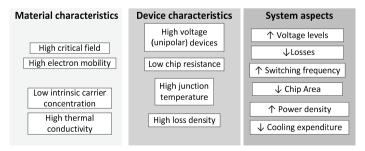

The obtained results enable performing a link between the advantages of using WBG materials at device and application levels, as summarized in the picture below.

Fig. 4: System aspects abstraction from material and device characteristics.

In the Chapter 4, the drawbacks and limitations of high switching speed will be explored, along with considerations regarding the impact of higher switching frequencies in the design of magnetic filters. Chapter 5 will deal with thermal-related aspects like operation at high temperature and possible savings with cooling. In Chapter 6, the influence of the specific chip resistance value along with low switching energy on expected chip expenditure and losses will be analytically evaluated

Later in chapter 7, a methodology for the assertion of gains due to the application of WBG devices will be proposed, with benchmarking of power converter specific costs assuming diverse device properties and cost scenarios. Different aspects of the system like cost distribution and original loss profile will also be taken in account in this analysis.

Finally, the chapter 8 will provide an overview of experimental results obtained with the application of SiC devices. Tests results with a multitude of power converters along with efficiency measurements and possible size reductions in the magnetics systems will be discussed, followed by some conclusions.

# 2 State-of-the-art power devices based on WBG

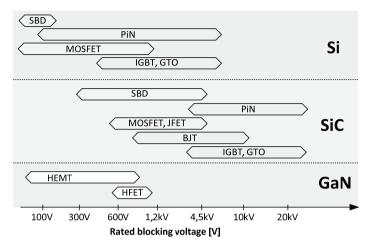

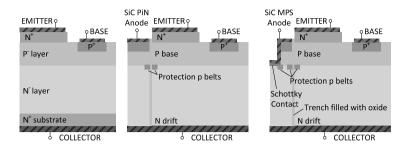

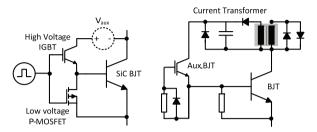

Below is presented an overview of possible constructive approaches regarding switches and diodes, giving an outline of some of the technologies that will be discussed in the details in the following chapters. As an important remark, focus will be given here only to devices for power conversion, excluding all approaches oriented to RF applications. Diodes are also out of the scope of the current investigation.

|          | Diodes   | Switches  Junction Controlled MOS controlled |            |  |

|----------|----------|----------------------------------------------|------------|--|

| Unipolar | Schottky | JFET, HEMT                                   | MOSFET     |  |

| Bipolar  | pin      | BJT,Bipolar<br>JFET,<br>Thyristor            | BT<br>IGBT |  |

Fig. 5: Roadmap of main existing power devices depending on function and structure.

From the picture above it is possible to identify the two basic structures of semiconductor devices depending on carriers used during conduction. In the unipolar devices only majority carriers are available and hence their resistance is basically dependent on the drift region characteristics. Meanwhile in bipolar devices, minority carriers are injected during conduction, modulating the conductivity of the drift region and enabling low voltage drop under conduction even for high blocking voltages. In the case of switches, the control can be exerted either through a junction or through metal-oxide channel interfaces.

A possible distribution of the voltage classes and device structures is depicted below. Due to the referred reduction of the chip resistance, unipolar devices (in orange color) based on SiC may be employed up to 4kV (with examples in the literature up to 10kV).

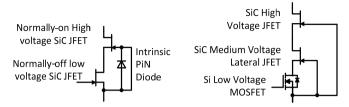

Fig. 6: Possible rated voltage classes for device structures from different semiconductor materials.

Details regarding the structure and operation of the most important SiC and GaN based switches will be presented in the following items. Of interest here is to identify not only specific issues but also requirements for reliable operation.

# 2.1.SiC-MOSFETs

MOS-driven switches are present nowadays in the majority of power conversion applications. Such popularity against other devices has been mainly justified by the simple and low-loss driving requirements along with robust and reliable operation. Regarding the Si-based technologies, MOSFETs are normally applied below 600V due to the very large chip resistance at higher voltage levels.

The use of SiC material allows a significant extension of the blocking voltage range, due to the massive reduction of the specific chip resistance. For instance, devices rated at 10kV attain similar values of specific chip resistance as their 600V Si-based counterparts. Several MOSFETs structures have been focus of investigations and will be presented in the next items, with a brief discussion of inherent characteristics and potentials.

Issues related to reliability and higher specific resistance against other SiC-designs remain the most significant drawbacks of this approach, as an overview of the latest related research results will be shortly presented.

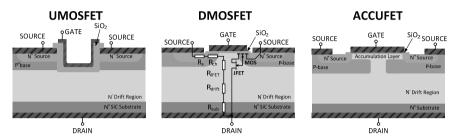

## 2.1.1. Device structure and characteristics

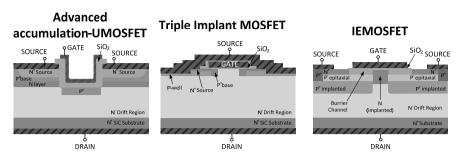

A multitude of possible approaches can be found for MOSFET structures, as briefly explained in the following items. Below are depicted the most common structures [73].

Fig. 7: Basic structures of SiC-MOSFETs.

- <u>UMOSFET</u>: Due to its relatively simple production steps without ionimplantation and high-temperature annealing steps, the UMOSFET was

the first power MOSFET structure demonstrated with SiC in 1992 [74].

The UMOSFET allows a higher channel periphery density and also avoids

the JFET resistance component, enabling lower resistance in devices rated

below 3kV. A higher channel resistance is nevertheless obtained because

the current flow takes place parallel to the vertical sidewall of the trench

structure. This results in low inversion channel mobility because the

current flows parallel to the c-axis of crystals and carriers and across

alternate planes of Si and C through interface traps and charges. Another

drawback is the high electrical field in the gate oxide near the edges of the

trench corners; which has been one of the main reasons for the limitation

of the blocking voltage in such structure. Possible structures dealing with

such limitation added P-implants below the gate region with buffer layers

to eliminate the JFET Effect.

- **DMOSFET**: This structure was employed as an alternative to deal with the electric-field crowding in the trench edges of the UMOSFET and is by far the most frequently found in the literature. The total chip resistance has in this case an additional component representing the region between the implanted P-wells, also called JFET component. Though increasing the distance between the wells reduces the referred resistance, it also increases the area of the device and reduces the effect of reducing the electrical field near the gate oxide under blocking conditions. Adding a highly-doped N-layer below the base implant leads to a better distribution

- of the electron flow, reducing the current crowding in the top of the drift region and hence reducing the resistance component of this region [75].

- ACCUFET: Another possible structure is based on the ACCUFEET principle, where an additional counter-doped layer is placed along the MOS interface, restoring the channel mobility and serving as a shield against high electrical-fields from the bulk SiC in the gate oxide. Hence, under blocking conditions this region is completely depleted by the potential of the nearby P-N junction, while all the blocking voltage is now supported only by the drift region. When activated, an accumulation channel is formed near the SiO<sub>2</sub>-SiC interface, reducing the resistance and moving the channel away from the interface, avoiding interface traps and hence increasing the mobility.

- Other vertical devices: Several variants of the above referred basic structures can be found in the literature. One first example is the so-called advanced accumulation-channel UMOSFET [76], [77], [78] with a Plaver below the trench structure that shields the gate oxide against high field levels and an N-epilayer between the P-base and N-drift regions that lead to higher current spreading avoiding current crowding in the trench corners. A similar device was presented in [79] and employs a second buffer layer up to the level of the P-implant below the gate trench. Another variant is the so-called triple-implanted MOSFET where a double P-implantation along with a buried source contacts decouple the problematic relation between the doping concentration of the P-base region with the channel mobility and threshold voltage. The IEMOSFET as presented in [80], [81] relies on an approach similar to the ACCUFET, but with the difference that half of the P-layer underneath the source contact is created by epitaxy, resulting in a smoother surface with higher channel mobility. In [82], the channel region in the DMOS structure was built with an epilayer, significantly reducing its inherent resistance and obtaining one of the lowest values of specific chip resistance in the voltage class of 1200V.

Fig. 8: Other SiC MOSFET structures.

In general, the total resistance of a MOSFET is the sum of the individual values from the channel, JFET region and drift region, though the existence of some of those depends on the employed structure, as already discussed. While in silicon designs, the drift region becomes dominant at higher voltage levels, the same is not valid for SiC devices due to the thinner width and higher doping concentrations. While JFET resistance is affected by the gap between the source cell implantations, the drift layer resistance is affected by the doping and thickness of the layer. Meanwhile the channel resistance is affected by the channel mobility and threshold voltage. These both parameters can be controlled by the nitridation process and are inversely proportional to each other. Hence obtaining a higher threshold voltage requires sacrificing the channel mobility what represents perhaps the major challenge behind the design of the MOSFET structure.

The resistance in practical devices is nevertheless normally higher than theoretical values due to the lower MOS channel inversion layer mobility [83]. A direct reason for this is the production process of the SiO<sub>2</sub> region that relies on thermal oxidation, resulting in a disordered interface containing several silicon oxycarbides along with high density of interface states. These can in turn either trap electron/hole carriers or act as recombination centers/scattering sites thus reducing the overall carrier mobility [84]. The oxidation process was hence a major focus of research and enhancements in the last years. Alternative for dealing with such problematic is reducing the length of the channel to obtain a high value of transconductance. Additionally, the channel density needs to be kept high.

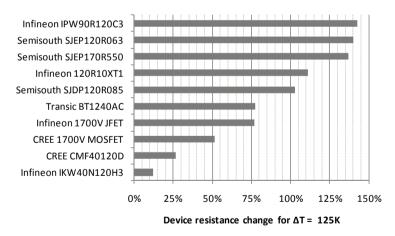

Regarding the temperature dependence, the channel resistance displays a negative coefficient, while the other two components have a positive coefficient. Hence, in the SiC-MOSFET a lower temperature dependence of the total device resistance can be observed

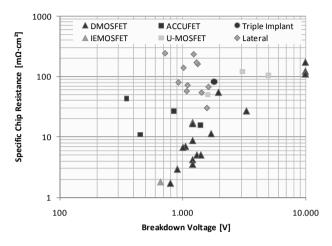

In the graphic below are presented the values of specific chip resistance for different MOSFET designs found in the literature. The lowest values were so far

obtained with the DMOSFET structure, while the lateral devices present values almost an order of magnitude higher.

Fig. 9: Specific chip resistance as a function of the device breakdown voltage at room temperature [85],[86],[87],[88],[89],[90]-[95], [96]-[98],[99],[100],[101]-[113].

In contrast with their Si-based counterparts, SiC-MOSFETs display a significantly less clear threshold limit and saturation regions. This is mainly explained by the interface quality in the channel region [114]. As a consequence, not only can the device resistance be strongly affected by the gate voltage, but also the implementation of short-circuit detection becomes more complex. SiC-MOSFETs are also characterized by an output capacitance density approximately 10X higher than Si devices, mainly due to the very thin drift region and higher doping concentrations (100x higher). Such characteristic affects the turn-on under hard-switching conditions, as the output capacitance needs to be discharged through the MOSFET channel. In case of high values of dv/dt, the channel current density may reach very high values [115]. The input capacitance is also larger due to the tight cell geometry for achieving higher channel density [116].

Most SiC MOSFET structures have an intrinsic PiN Diode with an on-state voltage drop around 2,5-2,7V. Due to such high voltage drop, an antiparallel Schottky can be employed in order to attain optimal switching performance. Caution needs nevertheless to be taken at higher temperatures and higher current values, when the intrinsic diode may enter in conduction before the external Schottky. The reverse recovery of the intrinsic diode is nevertheless much lower given the very small minority carrier lifetime and also the thin drift layer [117]. Reverse conduction is

also possible, as the current will go through the same path, given the drain-source voltage with a negative polarity and the gate voltage above the threshold limit. Such possibility becomes interesting when considering applications where synchronous rectifying is possible. The current will then be shared between the MOSFET structure and through the intrinsic diode, reducing the total losses [117].

Concerning reliability, the long-term stability of the gate oxide is normally considered one of the most critical issues in SiC MOSFETs. One first reason for this is that the gate oxide is under increased stress due to the higher values of electrical field. While the device is activated, the electric field remains concentrated on the interface with the N<sup>+</sup> source given the application of a positive gate bias. For off-state, the highest field moves then to the region near the JFET interface and near the edge terminators [118], [119], [120], [121]. Such higher values of stress becomes especially critical here because of the lower barrier height between the interface with the SiO<sub>2</sub> (2,7eV for SiC in comparison to 3,1eV for Si), increasing the probability of electron injection, especially at higher temperatures. As a preventive measure in order to deal with such problematic and avoid tunneling currents, the electrical field is normally kept in the design below 3MV/cm [116]. One possibility to decrease the stress in the oxide interface is reducing the cell pitch. Another effect reported in the literature [122], [123], [124], [125] is the threshold voltage shift, mainly caused when charges are captured in traps found either in the bulk SiO2 or in the interface with SiC that can be later removed by a gate voltage bias in the opposite direction.

# 2.1.1.1. Operation & Driving

Control of the SiC-MOSFET is basically the same as the one valid for Si-MOSFETs. On first difference is that plateau on the gate voltage cannot be completely observed in some SiC-MOSFETs designs, because of the unclear limit to the saturation region given the higher channel-length modulation coefficient. An important consequence concerning the low transconductance and threshold voltage of SiC-MOSFETs is that these devices may be more susceptible to gate ringing effect, i.e. the direct reflection of oscillations in the device voltage to the gate signal and vice-versa.

# 2.2.SiC-JFETs

In face of the referred challenges from the SiC-MOSFET, JFETs have regained significant attention due to their simple and robust structure. In contrast with the MOSFET, the JFET is not controlled by an insulated gate structure but rather by a reverse biased p-n junction. Hence the structure presents no interface problems related to gate oxide, increasing the reliability and ruggedness since no aging or

parameter drift may be observed, making the device attractive for operation at high temperatures. In addition to this, punch-through of the gate junction happens only at higher voltages in comparison with Si devices due to the wider band-gap of SiC [127] giving a broader gate voltage range capability.

A final feature here is that most devices have a symmetric channel structure, enabling operation as a synchronous rectifier in the reverse direction. This enables an additional reduction on the conduction losses during freewheeling [128].

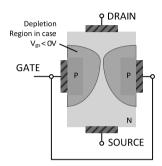

Fig. 10: Basic structure of a JFET.

#### 2.2.1. Device structure and characteristics

Two main constructive approaches can be identified for JFETs, namely the ones with <u>vertical and lateral structures</u>. For the last one all contacts are placed on the upper side, being mainly intended for the so-called power integrated circuits (PICs) [129] where the control, sensors and conversion stage are integrated within the same structure. In order to extend the blocking voltage, such devices require a larger chip area, representing a significant disadvantage against their vertical counterparts, where mainly the drift region height needs to be increased. Hence vertical-JFETs represent the vast majority of designs for high voltage and power applications nowadays. A further division can be identified for such group regarding the orientation of the channel: vertical and lateral. All the referred categories will be briefly discussed in the following items.

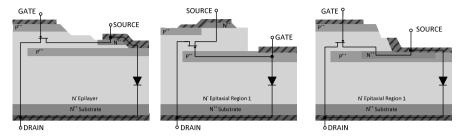

#### 2.2.1.1. Lateral-channel vertical-JFETs

Three first approaches, mainly investigated by the company SiCED, can be identified as depicted below [130] [131]. In all designs, one of the gate terminals is connected to the source terminal and hence normally grounded. Due to the high band gap value of SiC, the structure can rely on applying a bias for pinch-off only

in one gate, with a significant safety margin before entering in punch-through due to the material wider bandgap.

Fig. 11: Half-cells of lateral channel configurations with depiction of intrinsic diodes.

- Surface-gate variant 1 (S1-gate): An upper p-layer assumes the gate function and allows reduced gate resistance due to the distributed ohmic contact. Meanwhile the source contact is smaller. The reduction of the gate-to-drain overlapping area in such design leads to a smaller Miller Capacitance that enables a fast switching behavior [132]. The specific chip resistance is nevertheless increased by almost 50% in comparison with other approaches because part of the region before the channel needs to block the gate-to-source pinch-off voltage. An advantage here is that the blocking performance depends only on the drift region and not on the channel region; hence the same gate structure can be employed for difference voltage ratings. The intrinsic PiN diode in this structure can be used for freewheeling.

- Burried-Gate (B-gate): The controlling gate is composed of a buried p-layer within the structure, what leads to a low specific resistance. Reason for this is that the current flows directly from the source through the channel and then to the drift region. On the other hand, the dynamic behavior is negatively affected by such structure. A high C<sub>GD</sub> (Miller) capacitance can be observed due to the large area of the gate above the drain, while a high internal gate resistance exists due to the low conductivity of the SiC-based p-type layer that needs to be extended into the device. In this design, the intrinsic diode cannot be used for freewheeling, as it is connected between the gate and drain terminals.

- <u>Surface-gate variant 2 (S2-gate)</u>: In this variant of the surface-gate design, the source region was totally shifted to the buried P-gate region. An advantage here is that the gate length can be adjusted with superior precision [131].

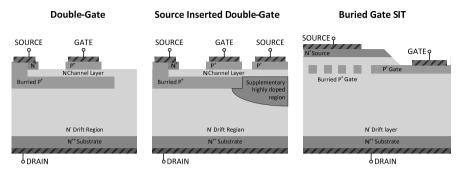

Other possible configurations found in the literature are depicted below.

Fig. 12: Half-cells of additional lateral channel configurations.

- <u>Double-gate (D-gate)</u>: It is a variant from the surface-gate approach, where the gate is involved only in the lateral JFET, mainly with the objective of normally-off operation. Due to the reduced gate length and gate capacitances, it is possible to attain superior dynamic characteristic. The extension of the buried P-layer plays in this design an important role in order to avoid field crowding in the corner of the shallow PN junction but with the simultaneous drawback of increasing the device resistance. Another variant [133] named source-inserted double-gate limits the extension of the buried P-layer to the edge of the gate P+ axis, but with the addition of an extra source contact with high doping concentration in the channel region.

- **Buried-Gate SiC-SIT**: In this variant of the buried-gate structure, the other P-gate layers is not connected to the source/ground, but rather distributed in a fine trench structure, achieving normally-off behavior with a very low value of specific chip resistance [134].

#### 2.2.1.2. Vertical-channel Vertical-JFETs

The vertical channel is most commonly obtained with trench implanted channel structure. In comparison with the lateral channel devices, the current approach can have simple fabrication steps and also attains lower chip resistance due to the fact that the lateral gate structures are now eliminated [135]. Higher channel mobility is observed with such devices because the electron flow takes place in the vertical direction in parallel with the c-axis. In contrast with the lateral channel devices, the gate region here needs nevertheless to be especially designed for each value of blocking voltage. Furthermore the available pinch-off limit is higher with such design because both regions lie on the same contact.

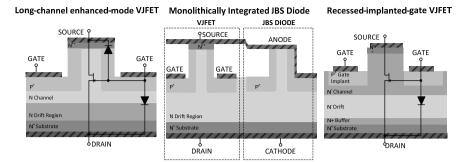

- Long-channel enhanced-mode VJFETs: In this structure, which is mainly employed by the manufacturer Semisouth, the channel is formed between the two p-layers from the buried Gate structures by means of masked plasma etching in a fabrication process based on the Si-trench-MOSFETs. The intrinsic pn-diode in such structure is connected from the gate to drain and source terminals. Given the large gate region overlapping the drain contact, the Miller capacitance is considerably high in such structure. By means of special doping profile and tight cell pitch design it is possible to obtain depletion of the channel at  $V_{GS}$  equal to 0V, leading to a normally-off operation. A certain temperature dependence of the threshold voltage is possible to be observed in the presented structure. with a factor around 2,5mV/K [135]. Meanwhile a high value of transconductance is necessary in order to attain the nominal current capability before reaching the built-in voltage of the gate-source diode [136]. Though a higher channel density can be achieved with such design. it is possible to observe a larger contribution of the channel structure to the device resistance due to the thin design and low doping concentration. Other possible optimizations in the structure may consider especial doping profiles leading to higher saturation current densities along with lower specific chip resistances, but simultaneously higher device capacitances and also higher electric field because of higher doping concentrations [136].

- Trenched-implanted VJFETs: The most significant difference on this design in comparison with the previous one is that the p-layer is processed with two different doping concentrations. Both normally-on and -off devices with low resistances have been demonstrated, although these values were commonly measured under bipolar operation [135], [138]. Though these devices do not have a body diode, a JBS SiC-diode can be integrated in the same chip structure with minor effort [139].

- Recessed-implanted-gate VJFETs: In contrast with the previous approaches, the gate structure is materialized by a single implant. In addition, a buffer layer is placed above the substrate and the sidewalls of the channel mesa regions do not get implanted [140]. Because of this last constructive characteristic, no intrinsic diode between the gate and source exists.

Fig. 13: Vertical Channel VJFET structures.

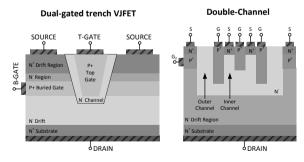

- <u>Dual-gated trench VJFET</u>: In this structure, trenches formed by dry etching process were later filled epitaxially with N and P layers forming the channel and gate regions [141]. Depending on the channel doping concentration, normally-on or –off devices can be obtained. Such structure presents no body-diode between source and drain. These devices suffer nevertheless from the so called DIBL effect (drain induced barrier lowering), when under high values of blocking voltage the depletion region is distorted in the direction of the drain, allowing the flow of the electrons and hence resulting in critical values of leakage current [136].

- **Double-channel**: Optimized for normally-off operation, enables lower resistance with higher channel density. The channels are separated by epitaxially growth p-stripes. The gate drain capacitance is nevertheless higher with such design, what may affect the dynamic behavior of the device [142], [143].

Fig. 14: Vertical Channel VJFET structures.

#### 2.2.1.3. Lateral JFETs

Several lateral designs can be found in the literature, with both lateral [144], [145] and vertical channel structures [146], [147], [148]. The last ones are likewise the vertical-JFETs also commonly designed for normally-off behavior. Practically all the referred devices make use of the RESURF technique to further reduce the chip resistance.

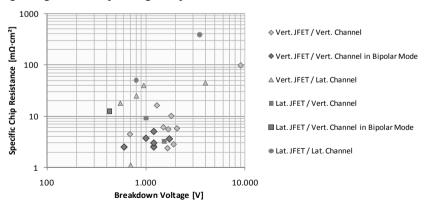

#### 2.2.1.4. Overview of specific chip resistance values

At this point it is necessary to differentiate between the unipolar and bipolar modes of operation of the JFET [149]. When the applied gate voltage rises beyond the built-in potential of the gate-source junction (approximately 2.7V), the injection of minority carriers starts to take place, indicating possible operation under bipolar mode. Such mode was in fact identified in early 80's [150], where it was demonstrated the possibility of reducing the device on-resistance by more than one order of magnitude. The observed reduction was proportional to the square root of the gate current, which in turn was proportional to the n-base concentration. Though the device resistivity can be reduced, this is accompanied by a significant drop in the structure gain with higher driving losses along with low switching speed because of the recombination time of the injected carriers [151]. An issue related to the operation under bipolar mode is the possible degradation of the onstate drain current characteristic due stacking faults promoted by the electron-hole recombination [152]. Below are presented the values of specific chip resistance as a function of the blocking voltage for the investigated structures, with distinction regarding the ones operating in bipolar mode.

Fig. 15: Specific chip resistance of investigated JFET devices [132], [134]-[141], [143]-[148], [151], [153]-[161].

## 2.2.2. Operation & Driving

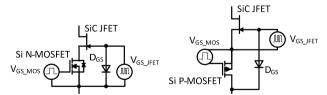

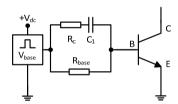

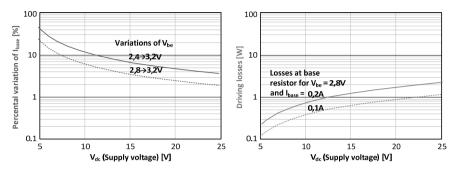

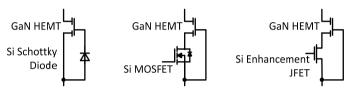

Considering the basic JFET structure, the most significant drawback is the normally-on behavior, as the channel will block only with a continuous negative gate voltage leading to the formation of the depletion region. Given the fact that the normally-on behavior represents an inherent reliability problem for most circuits, especial gate driving circuits and supply strategies were proposed in the literature but still end up increasing the costs and complexity. Another possibility is the use of cascode structures that are nowadays seen as the most promising alternative for the referred problematic. Such driving approaches will be discussed in the following items.

On the other hand, <u>normally-off</u> devices can be obtained by relying on the potential barrier formed by the grounded gate junction (V<sub>GS</sub>=0V). In order to attain such capability, the channel region needs nevertheless to be very narrow with low doping concentration what results in a higher channel resistance. Another critical issue related to these devices is the reduction of the threshold voltage with increasing temperature values, what leads to the requirement of bipolar gate voltage driving to attain certain immunity against EMI [142].

#### 2.2.2.1. Normally-on devices in stand-alone operation

As already stated before, the basic JFET structure is a normally-on device, i.e., if no voltage is applied between the gate and source terminals ( $V_{GS}$ ), the device remains active. Under such conditions, the n-channel behaves like a resistor up to a certain drain-source voltage value ( $V_{DS}$ ). Beyond such level, the current reaches saturation since the increasing voltage drop leads to a reduction of the channel width and increase of the depletion region.

On the other hand, when the negative values of voltage are applied across the gate-source ( $V_{GS}$ ), the depletion layer of the PN-junction between gate and n-channel is increased, reducing the conductivity of the last one and leading to a total blocking state of the device, if the <u>pinch-off limit</u> is reached. Such level shows practically no temperature dependence and is mainly affected by the channel doping concentration and geometry.

The negative gate voltage for safe turn-off shall nevertheless be significantly lower than the pinch-off value. Reasons for this are the parameter variance between devices, temperature drift and requirement of improved ruggedness against high dv/dt transients. The voltage may nevertheless not surpass the <u>reverse breakdown</u> gate voltage in order to avoid the gate junction breakdown.

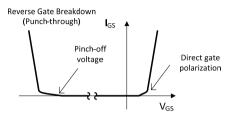

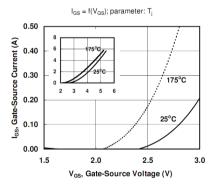

During conduction, operation with a slightly positive gate voltage leads to a wider channel and hence a small reduction of the device resistance (in range of 5%, according to [162]). Caution shall be taken with the <u>direct polarization</u> of the Gatesource junction, what would lead to an increase in the gate current and possible operation in bipolar mode, as already previously explained. All the above referred limits regarding the gate voltage are depicted in the graphic below.

Fig. 16: JFET gate characteristic with limits regarding breakdown and direct polarization.

Considering the above conditions, it is possible to identify two main driving approaches.

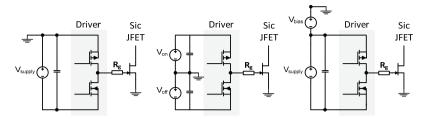

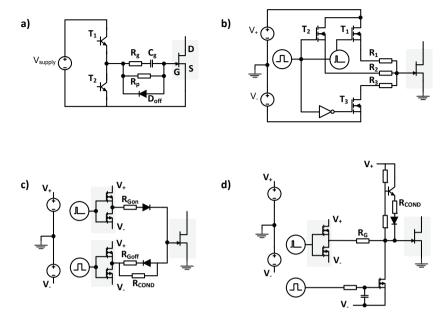

In the first group, the gate is driven with fixed voltage levels between the reverse-breakdown and direct polarization limits since no gate current limitation is provided. Selecting the correct levels is nevertheless a difficult task, given the parameter variance due to the maturing technology and also the temperature dependence. Possible configurations are depicted below, mainly relying on a totem pole configuration. In the standard configuration, the upper transistor is connected to the reference ground and source, enabling blocking with  $V_{\text{supply}}$  and activating with approximately 0V. In the configuration presented in [163] the middle point of the configuration is connected to the JFET-source, enabling the selection of a positive voltage value. Another alternative [164] shifts the whole gate potential by a certain level dictated by the additional source  $V_{\text{bias}}$ , activating the JFET now with a non-positive voltage. Such solution was proposed with the objective of limiting the maximum voltage class of the driving circuit in order to enable the use of standard products in the market. Other similar solutions were presented in [165], [166] and [167].

Fig. 17: Driving solutions with traditional totem-pole configurations [163], [164].

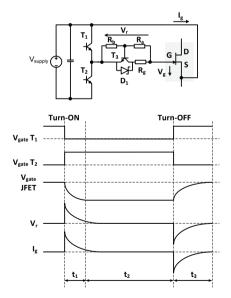

The second group of circuits provides a certain limitation to the gate current and hence enables operation with more flexible voltage levels, even over the referred limits, i.e. driving the JFET in avalanche for a brief interval of time. Such possibility allows a significant increase in the switching speed. One first circuit directly controlling the gate current was proposed in [168] and is depicted below. The voltage transients imposed by the totem-pole transistor association  $T_1/T_2$  are translated into peaks of gate current directly controlled by the added transistor  $T_3$ . Hence, the gate current is limited while the JFET is deactivated and a gate voltage higher than the pinch-off limit can be employed to increase the switching speed.

Fig. 18: JFET driving circuit as proposed in [168].

In a simpler variant of the circuit above [170], the extra branch is substituted by a simple parallel association of  $C_G/R_s/D_{on}$  with the function of avoiding the

avalanche condition, given the higher level of selected  $V_{\text{supply}}$ . The referred parallel association also allows high gate current peaks that significantly increase the switching speed of the JFET. The resistor with high value  $R_p$  only serves to limit the current while the JFET is deactivated. The size of the capacitor  $C_g$  is chosen considering the required peak current transients and also to avoid a longer duration of voltage levels above the breakdown limit. Finally, the diode  $D_{on}$  clamps  $V_{gs}$  close to zero while the device is activated avoiding oscillations. With such configuration it was possible to achieve (according to the reference) a reduction of almost 50% in the switching losses.

A very similar circuit was presented in [162], with the difference that now the driving branch is directly connected to the gate terminal, while the source is connected to the positive voltage terminal of the supply. In addition, a resistor  $R_{\rm s}$  was added in series with the parallel association  $C_{\rm g}/R_{\rm p}/D_{\rm on}$ , enabling a finer control of the duration of the peak current transients by means of the time constant  $R_{\rm S} \cdot C_{\rm g}$ .

Another class of drivers still belonging to the second group relies on controlled current sources to directly limit the applicable gate current, avoiding the occurrence of avalanche. Advantages of such approach is the free selection of the voltage supplying circuit along with independence from JFET operating conditions like blocking voltage. The use of two separated sources for transient and continuous driving of the JFETs along with a logic inverter to provide the appropriate voltage reference to the gate potential was patented in [171]. In [172] a single current source is employed, while for deactivation the gate-source contacts are simply short-circuited. In the same publication, a virtual gate charge enhancement is applied by means of an additional switch and capacitor.

Fig. 19: JFET driving circuits as proposed in [170], [162], [171].

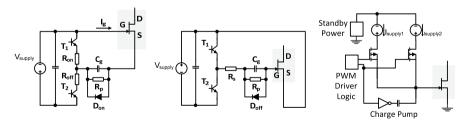

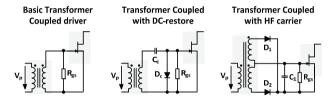

Regarding galvanically-isolated drivers for normally-on devices, several approaches were analyzed in [173]. Using a simple pulse-transformer driven with bipolar voltage cannot be considered as a valid solution due to the fact that depending on the duty cycle value, the negative voltage required to block the JFET will not be maintained for enough time, possibly resulting in a reactivation of the

device. In addition to this, driving the device with similar values of positive and negative gate bias is for normally-on devices not possible because of possible direct polarization. By adding a capacitor and diode to the previous configuration, the so-called DC-restorer is obtained, though the presence of a positive voltage on the secondary side may lead to saturation of the transformer. In order to avoid such limitation, a high frequency carrier signal based on the original PWM can be modulated in the circuit presented in the right-side of the picture below. By applying positive pulses to the primary side, these are rectified and charge the capacitor  $C_1$ , providing a negative bias to turn-off the JFET. By interrupting the carrier signals,  $C_1$  is discharged by  $R_{\rm gs}$  and the JFET is activated with 0V. Drawback of such configuration is the dynamic of the capacitor discharge, what significantly limits the attainable duty-cycle and frequency values.

Fig. 20: Transformer-coupled JFET passive driving circuits [173].

Other configurations with inherent galvanic isolation were presented in [174], [175]. For the first one, an additional winding is placed in a buck inductor with a low output voltage ( $\pm$ 12V), allowing the use of a normal buck controller (like the UCC3809D-1). Meanwhile the second solution employs a flyback transformer with an especially designed controller to drive the JFET, with the gate-source intrinsic diode operating as the freewheeling output diode. By means of selecting a proper size for  $C_{gg}$ , even under failure of the main supply the JFET can remain blocked for a certain interval of time long enough to allow safety switches in the circuit to disconnect the source/load and hence avoid critical failure of the circuit in case normally-on devices are employed.

Fig. 21: Isolated gate driver configuration as proposed in [175].

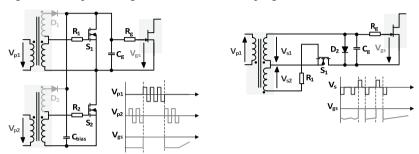

The limitations of the above passive driver circuits can be overcome by using active switches as in the configuration depicted in the left-side of Fig. 22. When

the carrier signals are applied to the primary winding 1, the half-bridge output across  $C_g$  is changing between the 0V and high impedance ( $S_2$  off) and hence activating the JFET. In the other way around, the half-bridge output is switched between the voltage of the capacitor  $C_{\text{bias}}$  and the high impedance ( $S_1$  off). Due to the JFET Gate-source capacitance and also the extra capacitor  $C_g$ , the gate-source voltage can be kept at a negative value, hence keeping the JFET deactivated.

Fig. 22: Transformer-coupled JFET active driving employing phase-difference and edge-triggered circuits with respective control signals [173].

The capacitor C<sub>bias</sub> is charged by the additional branches of the each transformer through the diodes  $D_1/D_2$ . In case no signals are present in both primaries, the gatesource voltage drop to zero with a time constant depending on the time constant C<sub>g</sub>/R<sub>g</sub>. A simpler configuration with similar functionality is depicted in the rightside of Fig. 22, being called edge-triggered circuit. The number of turns in the first and second secondary windings is chosen in order to obtain respectively the JFET and MOSFET threshold voltages. By means of a negative voltage pulse in  $V_{S1}$ ,  $S_1$ is deactivated, reversely biasing D2, and charging Cg through the intrinsic diode of S<sub>1</sub>, hence resulting in the a negatively built voltage across the capacitor that blocks the JFET. In case no pulse is applied, the capacitor C<sub>g</sub> is connected to a high impedance value (through the parasitic capacitance of S<sub>1</sub>) and is slowly discharged. On the other hand, when a positive voltage is applied to  $V_{S1}$ ,  $S_1$  is activated and the C<sub>g</sub> is discharged, while the gate-source voltage remains clamped by means of the direct polarization of D2. A major advantage for the operation with short pulses in both circuits referred above is the possibility of reducing the size of the transformer due to the low volt-second product and also avoidance of transformer saturation along with frequency/duty cycle limitation.

Employing stand-alone normally-on devices contradicts nevertheless the common paradigm of only using normally-off switches; as in the case of failure of the control system or power supply and also during start-up, the switches may remain activated. In case the devices are placed in a hard short-circuit path like when

connected to a large DC-link capacitance or to the grid, a critical failure of the system may happen. Examples of such critical applications are the voltage source inverter (VSI) and most DC/DC converters. One approach to deal with such problematic is to employ a charge-pump system that provides a self-protection during power start-up [176], keeping the duration of possible short-circuit-currents below 200µs. The galvanically isolated circuit proposed in [175] may also be used with normally-on devices and by properly designing the capacitor  $C_{\sigma\sigma}$  (Fig. 21), a certain time interval can be guaranteed for disconnecting the source/load under failure conditions. In [177], the reliability against failure is provided in a step-down converter by means of a magnetically coupling the driver supply with the main inductor. In [178] is presented an interchangeable system of switches that during start-up immediately provides negative voltage to the drivers avoiding shootthrough. A rather complex solution presented in [179] makes use of the in-rush current from the DC-link to the supply the JFET drivers. A current limiting resistor in parallel with a bypass switch [180] is applied in the middle point of the DC-link and used to limit the DC-link current either at start-up or to avoid shootthrough, protecting the JFETs.

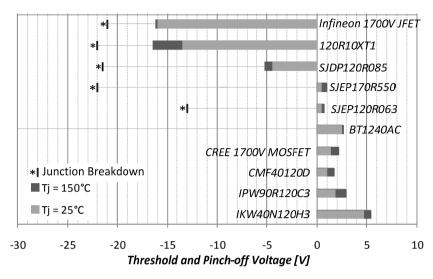

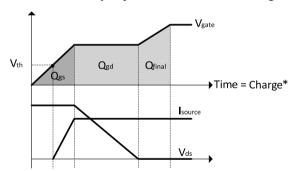

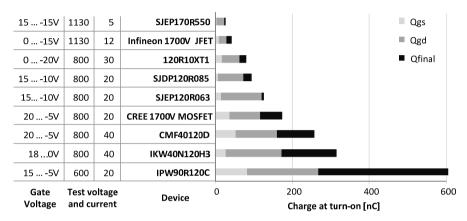

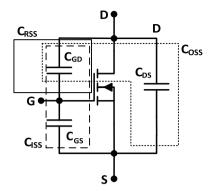

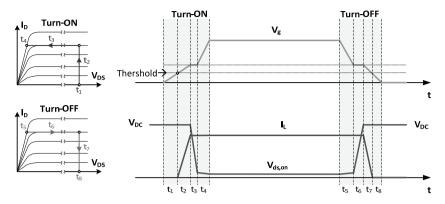

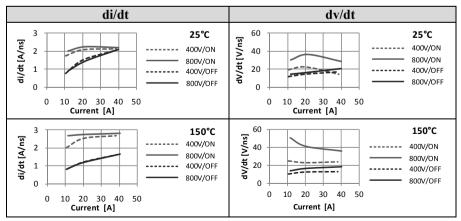

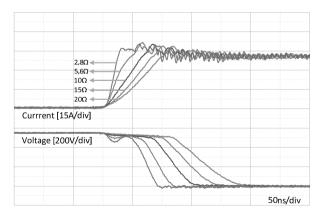

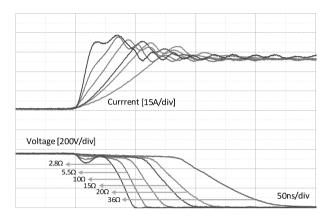

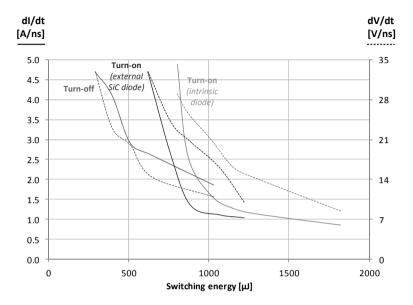

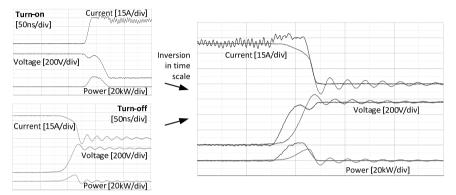

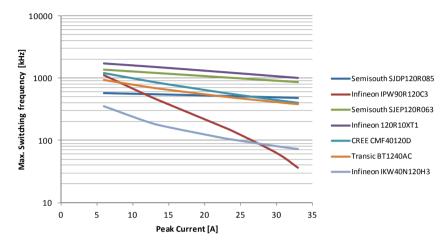

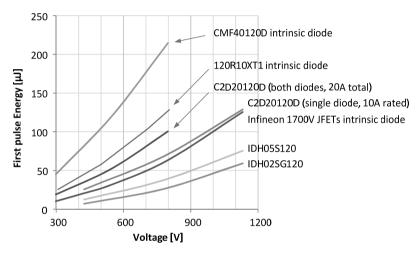

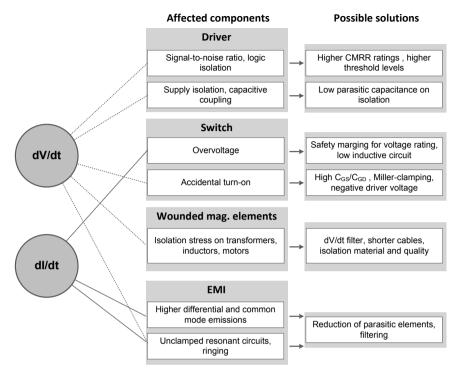

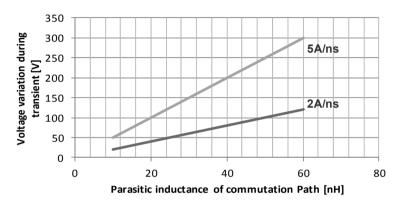

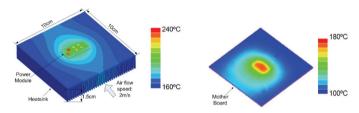

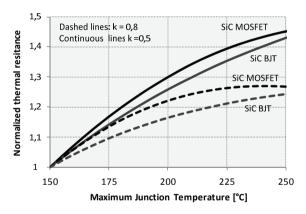

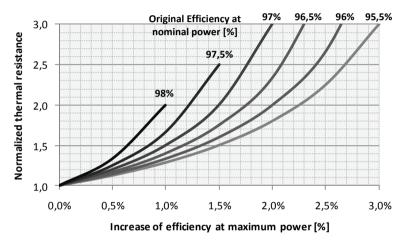

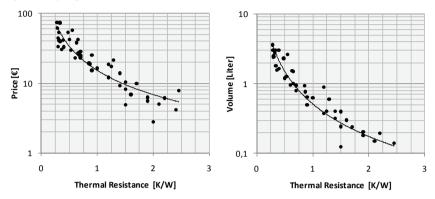

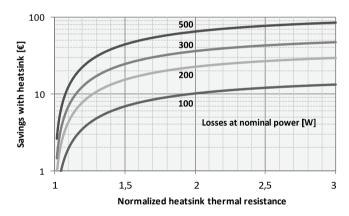

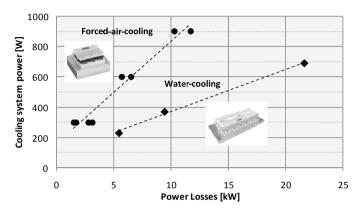

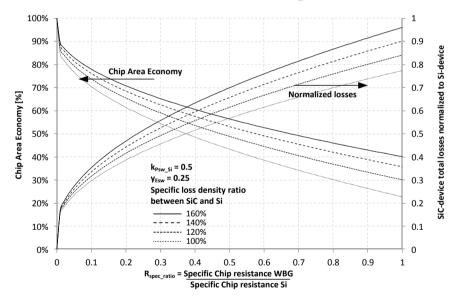

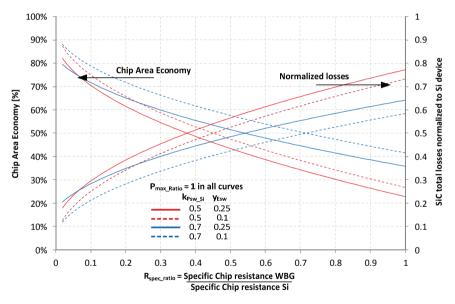

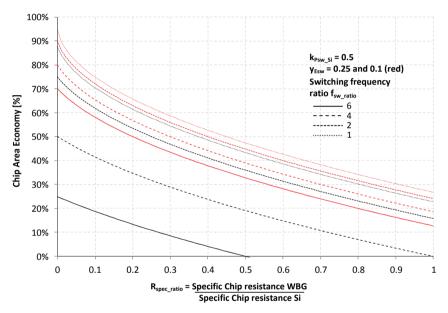

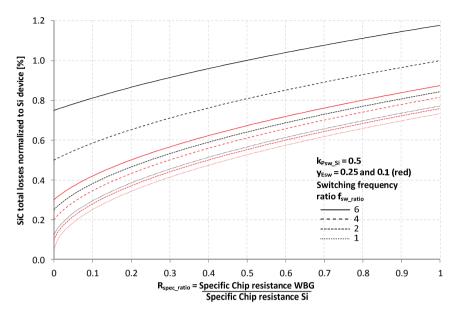

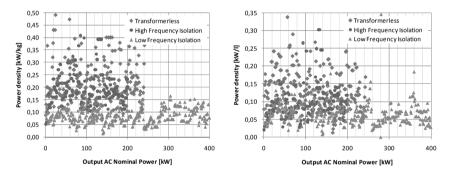

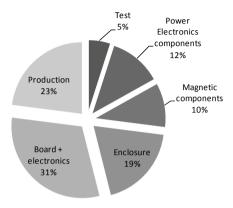

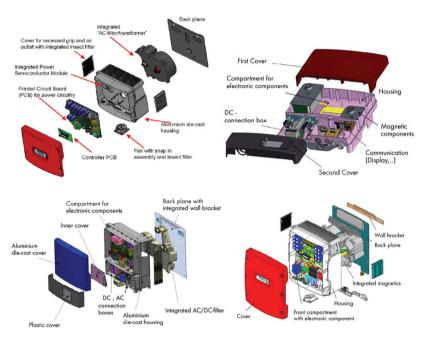

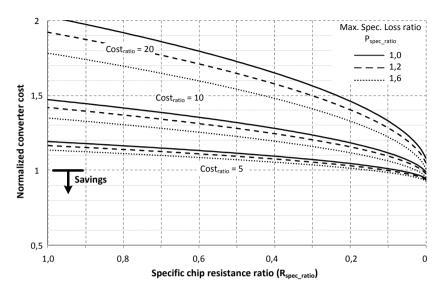

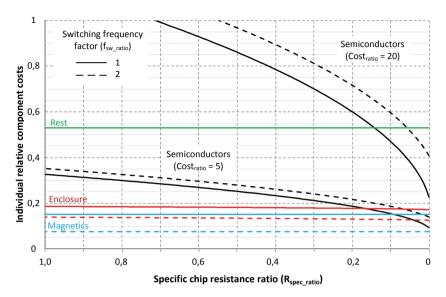

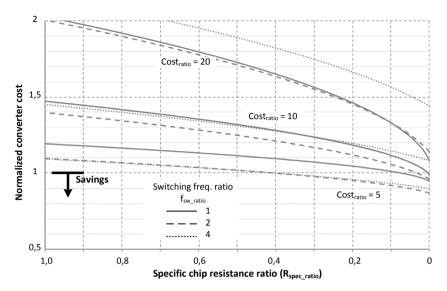

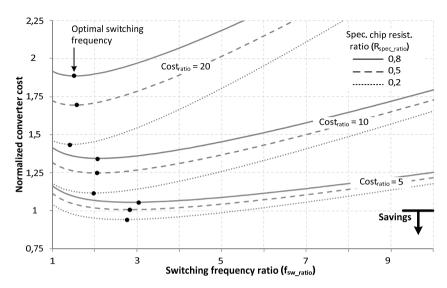

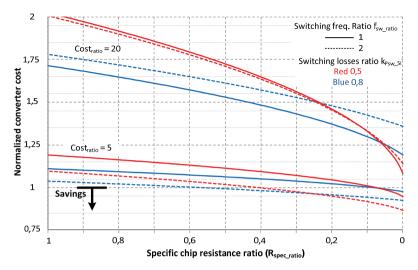

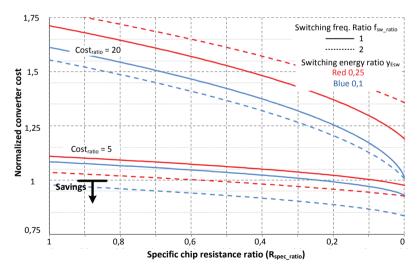

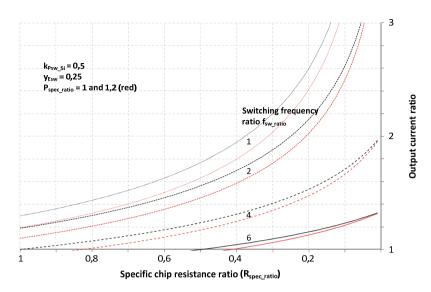

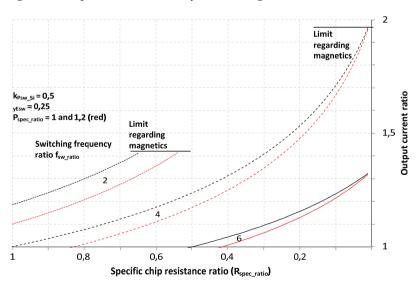

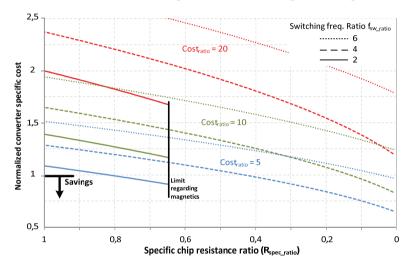

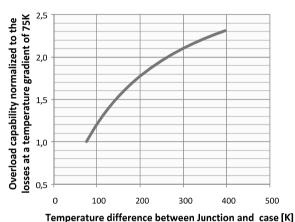

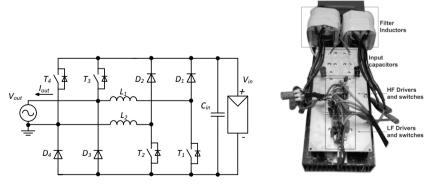

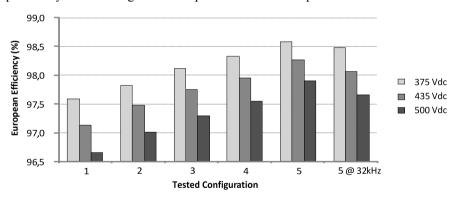

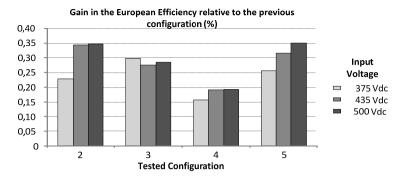

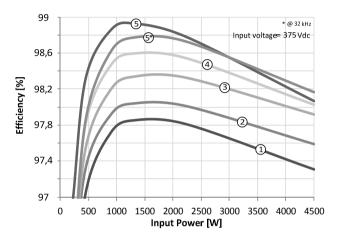

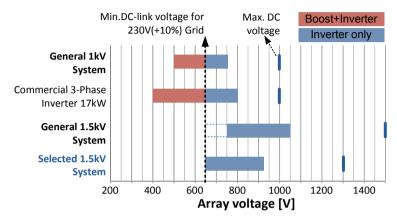

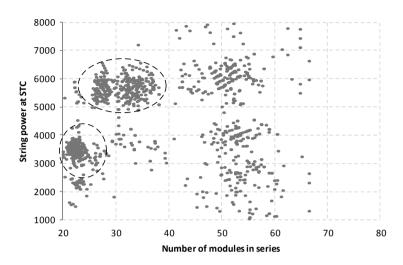

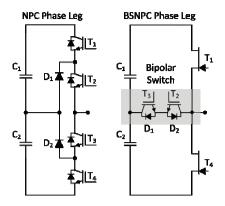

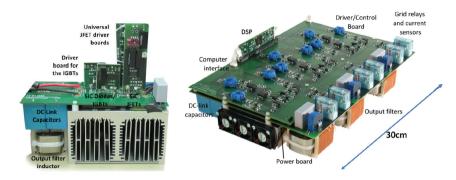

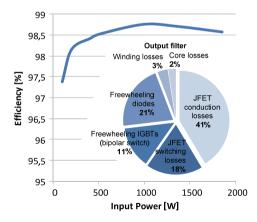

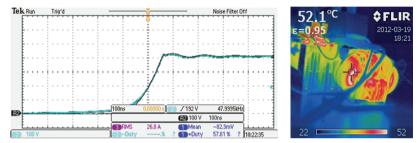

On the other hand, there are several circuits where the application of normally-on devices has no reliability issues. This holds true especially for photovoltaic system applications, where the source, i.e. photovoltaic array, is current-limited. In addition, topologies with series association of switching devices may indirectly provide the required turn-off capability. Additional details about such possibilities will be given in a later chapter.