Ashot Melkonyan

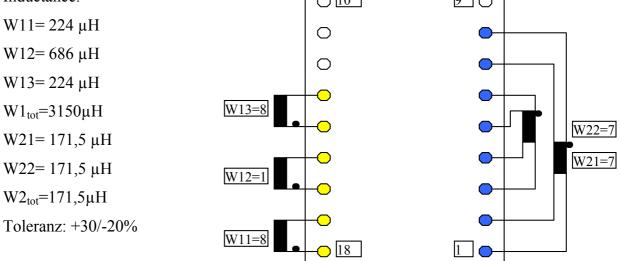

High Efficiency Power Supply using new SiC devices

This work has been accepted by the faculty of electrical engineering / computer science of the University of Kassel as a thesis for acquiring the academic degree of Doktor der Ingenieurwissenschaften (Dr.-Ing.).

Supervisor: Prof. Dr.-Ing Jürgen Schmid Co-Supervisor: Prof. Dr.-Ing. Eckhard Wolfgang

Defense day: 9<sup>th</sup> February 2007

Bibliographic information published by Deutsche Nationalbibliothek Die Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data is available in the Internet at http://dnb.ddb.de

Zugl.: Kassel, Univ., Diss. 2006 ISBN: 978-3-89958-302-1 URN: urn:nbn:de:0002-3027

© 2007, kassel university press GmbH, Kassel www.upress.uni-kassel.de

Printed by: Unidruckerei, University of Kassel Printed in Germany

# Zusammenfassung

Neuartige Siliziumkarbid (SiC) Bauelemente und dessen Nutzung in Schaltnetzteilen ist der Gegenstand dieser Arbeit. Wie sind die Eigenschaften des SiC Leistungsbauteils optimal auszunutzen um die Topologien der Schaltnetzteile zu vereinfachen und die Leistungsdichte zu steigern.

Die SiC Schottky Dioden sind am Markt, aber auch die SiC Transistoren sind seit kurzem verfügbar als FuE Muster. Dennoch, die Verbreitung und der Einsatz in den herkömmlichen Topologien findet sehr langsam statt. Einerseits die hohen Produktionskosten des Halbleiters und dementsprechend hohe Preisverhältnis gegenüber Si Bauteilen, anderseits unbekannte Eigenschaften des SiC Transistors (SiC JFET) verzögern die breite Marktakzeptanz. Offensichtlich ist, dass ein einfacher Umtausch der Si Leistungsschaltern mit den entsprechenden SiC Bauteilen in den herkömmlichen Schaltnetzteilen würde nicht die erwartete Effizienz - und Leistungserhöhung ermöglichen.

Ausgezeichnete Eigenschaften von SiC Halbleiter sind seit Jahren gut bekannt. Was nicht eindeutig ist, und das ist die Zielsetzung dieser Arbeit, in welcher Weise sind diese Eigenschaften auszunutzen um die maximalen Vorteile für die Endanwendung zu einzubringen.

Anhand der Beispielanwendung der Telekomstromversorgung wurde vorgeschlagen das Vorgehen in der Topologieauswahl zu ändern und für einen Leistungsbereich von 1kW-1.5 kW anstatt Mehrschaltertopologien eine Einschaltertopologie mit SiC Transistor zu verwenden. In der entstandenen Anwendung ist der Einsatz des SiC Junction Field Effect Transistors (JFET) notwendig und dessen Potenzial ist voll ausgenutzt, wobei die Probleme bezüglich der Mehrschaltertopologien beseitigt sind.

Um die Schaltfrequenz zu erhöhen und die Leistungsdichte weiter zu verbessern, wurde ein weiches Schalten von Resonant Reset Converter verwendet, die die parasitäre Elemente der Schaltung nutzt. Gleichzeitig ermöglicht die höhere Sperrspannungsfähigkeit des SiC Schalters eine schnellere Entmagnetisierung des Leistungstransformators.

Die SiC JFET Transistoren sind detailliert analysiert und die spezifischen Eigenschaften sind festgestellt, welche eine neuartige und einfache Gateansteuerung ermöglichen.

Die bekannte Lösung für Normally-ON Problematik – "Baliga Pair" wurde erweitert, um zusätzliche Stabilität zu erhalten, was sich besonders bei Schaltfrequenzen über 200kHz bemerkbar macht.

To my family, with much love and gratitude for loving care and support during all these years

January, 2007

# **Summary**

New Silicon Carbide (SiC) power devices and their usage in the switch mode power supply (SMPS) circuits is the subject of this thesis, - how to fully exploit the potential of SiC devices in switch mode converters while simplifying their topologies and increasing power density and efficiency.

Although the excellent properties of the SiC semiconductor and its superior features compared with silicon (Si) are recognized for many years and long-awaited SiC power devices are now available, their practical application in power supplies is still seems to take time. Obviously, simple replacement of the Si power transistors in commonly used topologies, which are not originally designed to exploit all futures of SiC devices, will not give the expected efficiency increase and cost advantages. The SiC power devices set another dimension in designing process of the switch mode power converters. It becomes necessary to develop a new, system relevant approach in the power supply design.

Currently in the 1.0kW -1.5kW power supplies (e.g. for telecom applications) multi-switch Half-Bridge or Full-Bridge topologies are used. Having the advantage of limited voltage stress on the switches, (app. 600V-800V), these topologies incorporate external isolated high-side gate drive circuits, have to maintain appropriate dead times to prevent shoot trough conditions and have to deal with inherent magnetic flux imbalance in the transformer core.

It is suggested to change the settled hierarchy in the converter topologies used in the mentioned power range and replace the Si-based multi-switch converters by a SiC single-switch converter. In the proposed single-switch resonant reset forward converter, the specific properties of SiC Junction Field Effect Transistor (JFET) are necessarily used and its potential is fully utilized, while the challenges associated with multi-switch topologies are basically eliminated. The comparative analysis also shows minimal differences between passive components of the single-switch, single-ended and double-switch, double-ended converters.

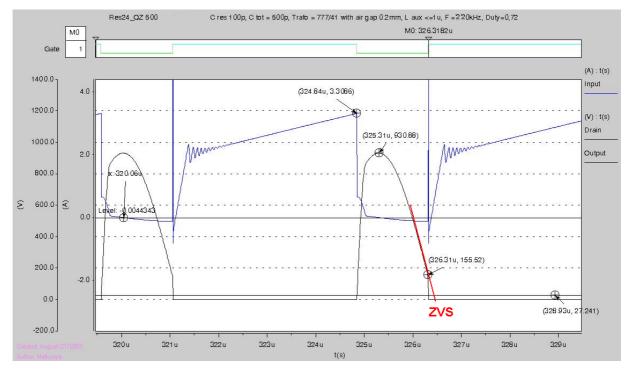

Proposed zero voltage switching (ZVS) approach in the adopted converter enables further increase of the switching frequency while utilizing the circuit parasitics and increasing the power density. The circuit is analyzed over the complete power and voltage

range. Special attention is paid for parasitics, possible overvoltages, ZVS operation and switching losses.

However, the SiC JFET is a normally ON transistor and requires relatively high negative voltage for switching OFF, which makes its utilization in many applications difficult. The new and simple driving circuit, based on DC voltage bias is suggested as a gate driver for SiC JFET.

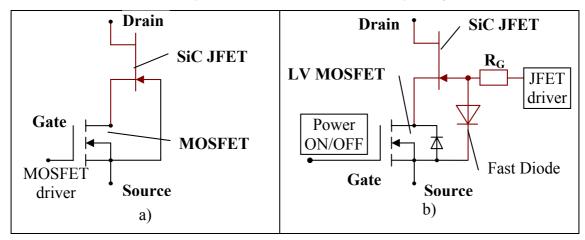

Another known way out from normally ON behavior is the "Baliga Pair" or combined "Cascode" circuit, where the JFET-MOSFET pair can operate in normally OFF mode. However, in such circuitry, because of limited reverse recovery capability of the body diode, a parasitic oscillation could occur if very fast switching is performed. Also the direct switching speed adjustment by means of gate resistors is not possible. For eliminating these limitations a modification of the "Cascode" is proposed, where the SiC device can be driven with its own gate, yet remaining normally OFF in case of failure or power down.

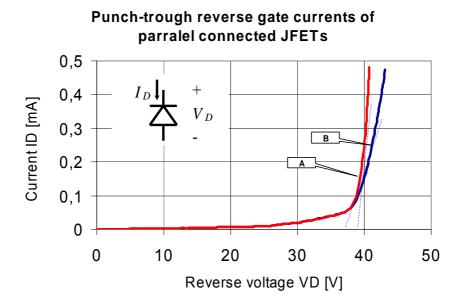

Although the SiC wafer quality is increasing gradually, large chip areas are not feasible in near future. Logical solution for increasing device current capability is the parallel connection of the small chips. Investigations on the SiC JFET samples have shown different punch-trough gate currents. This fact should be taken into account, for the gate drive circuit designs if parallel driving of the SiC JFETs is necessary, especially for circuits with avalanche or current source driving methods.

Mentioned proposals are investigated and implemented in practical hardware design.

#### **Preface**

This thesis project has been jointly supported by Infineon Technologies and Siemens AG.

The steering group consists of:

Prof. Dr. Jürgen Schmid

Prof. Dr. Eckhard Wolfgang

Prof. Dr. Peter Zacharias

Prof. Dr. Leo Lorenz

The following parts of the thesis are original work:

✓ SiC devices are implemented in the Resonant Reset Forward converter, its output power range has been extended up to 1kW and zero voltage switching (ZVS) operation is realized.

✓ SiC JFET transistors are analyzed and tested under high temperature conditions (250°C) and investigations are carried out for possible parallel connection of the chips.

- ✓ Alternative gate driver circuit for SiC JFET transistors is proposed.

- ✓ SiC JFET Cascode (Baliga Pair) circuit is investigated at higher switching voltage slew rates and modification is proposed for minimizing the influence of packaging parasitics

- ✓ A practical 1 kW prototype of single switch resonant reset converter is realized, where the active switch operates at 200-300 kHz frequency. High temperature operation capability (app. 250°C) is tested under light load operation.

The research project is partially published in the following publications:

- 1. European Power Electronics Conference EPE'03, September 2003, Toulouse, France

- 2. Power Control and Intelligent Motion PCIM-Europe'04, May 2004, Nürnberg, Germany

- 3. IEEE Power Electronics Specialist Conference PESC'04, June 2004, Aachen, Germany

- 4. Power Electronics and Motion Control EPE-PEMC'04, September 2004, Riga, Latvia

- 5. IEEE Industrial Applications Society IAS'04, October 2004, Seattle, Washington, USA

- 6.VDE-ETG Schlüsseltechnologie für nachhaltiger Energietechnik, 2004, Berlin, Germany

- 7. European Power Electronics Conference EPE'05, September 2005, Dresden, Germany

# **Acknowledgments**

First, I am grateful to my supervisor Prof. Jürgen Schmid for his guidance and inspiration during whole time of the work. He has encouraged me into the project at the beginning, when I was a Master student at the Kassel University and supported me up to the end, when I was an external PhD student and worked in industry.

I am grateful to my co-advisors Prof Eckhard Wolfgang and Prof. Leo Lorenz for leading me to the industrial world of power electronics and giving me an opportunity to accomplish this PhD work in industry. Especially I want to thank Prof. Wolfgang for technical supervision and enabling me to accomplish this thesis despite of many other projects and limited time.

I would like to thank also Prof. Zacharias for his valuable advices and practical recommendations. Without his help and critical notes I would not be able to bring this thesis to its final form.

I would like to thank Prof. I. Hofsajer for his help in experimental analysis, for his friendship and willingness to discuss technical problems.

I would like to express my gratitude to the staffs and all my colleagues of IEE-RE, Infineon department AI AP ADC and to my current department CT PS2 at Siemens AG for their friendship and support to complete my PhD study. Especially I would like to thank Mr. M. Herfurth for his constructive discussions and aid in hardware implementations. Also Dr. I. Zverev is much appreciated for supporting me at the beginning of the project.

# Contents

| H  | ligh Eff  | aciency Power Supply using SiC Devices                       | l    |

|----|-----------|--------------------------------------------------------------|------|

|    | •         | enfassung                                                    |      |

| S  | ummar     | y                                                            | vi   |

| P. | reface.   |                                                              | viii |

| A  | cknow     | ledgments                                                    | ix   |

| C  | ontents   |                                                              | X    |

| U  | sed abl   | previations                                                  | xiii |

| L  | ist of ta | ıbles                                                        | XV   |

| L  | ist of fi | gures                                                        | xvi  |

| 1  | Int       | roduction                                                    | 1    |

|    | 1.1       | Background and Motivation                                    | 1    |

|    | 1.2       | Application requirements & trends                            | 4    |

|    | 1.2.      | 1 Telecom application requirements                           | 4    |

|    | 1.2.      | 2 Automotive application requirements                        | 6    |

|    | 1.2.      | Requirements in energy and in harsh environment applications | 8    |

|    | 1.3       | Thesis objective                                             | 10   |

|    | 1.4       | Outline of the thesis                                        | 11   |

| 2  | Sta       | te of the Art                                                | 12   |

|    | 2.1       | Roadmap of power semiconductor devices                       | 12   |

|    | 2.1.      | 1 Wide band gap semiconductors                               | 12   |

|    | 2.1.      | 2 SiC technology and properties of the SiC                   | 13   |

|    | 2.1.      | Power switching devices based on SiC semiconductor           | 15   |

|    | 2.2       | Roadmap of power converters                                  | 19   |

|    | 2.2.      | 1 Classification of main topologies                          | 19   |

|    | 2.2.      | 2 State of the art topologies                                | 23   |

|    | 2.3       | Power losses in SMPS                                         | 27   |

|    | 2.3.      | 1 Losses in active devices                                   | 27   |

|    | 2.3.      | 2 Losses in magnetic devices                                 | 31   |

| 3 | Mi  | niaturization and integration in power electronics                    | 33       |

|---|-----|-----------------------------------------------------------------------|----------|

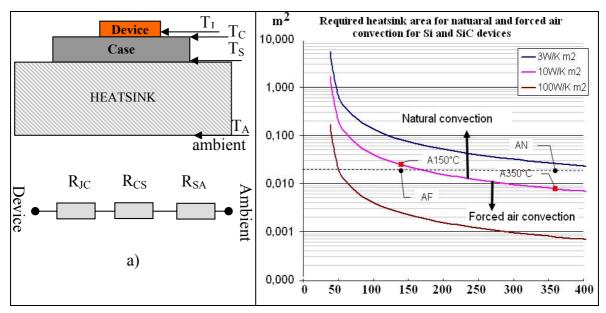

|   | 3.1 | Enhanced thermal management in SiC power converters                   | 35       |

|   | 3.2 | Passive components & packaging issues in high temperature power elect | ronics37 |

| 4 | Sat | e of the art SiC JFET power transistor                                | 39       |

|   | 4.1 | Overview                                                              | 39       |

|   | 4.1 | .1 Principle of operation                                             | 39       |

|   | 4.1 | .2 Spice modeling of SiC JFETs                                        | 39       |

|   | 4.1 | .3 High temperature operation                                         | 40       |

|   | 4.2 | The SiC VJFET transistor                                              | 41       |

|   | 4.2 | .1 Static characteristics                                             | 43       |

|   | 4.2 | .2 Dynamic characteristics                                            | 45       |

|   | 4.2 | .3 Normally ON problem and JFET-MOSFET Cascode circuit                | 46       |

|   | 4.3 | SiC VJFET model                                                       | 48       |

|   | 4.4 | Paralleling of the VJFET transistors                                  | 50       |

| 5 | Ap  | plication and impact of the SiC devices on the power converters       | 51       |

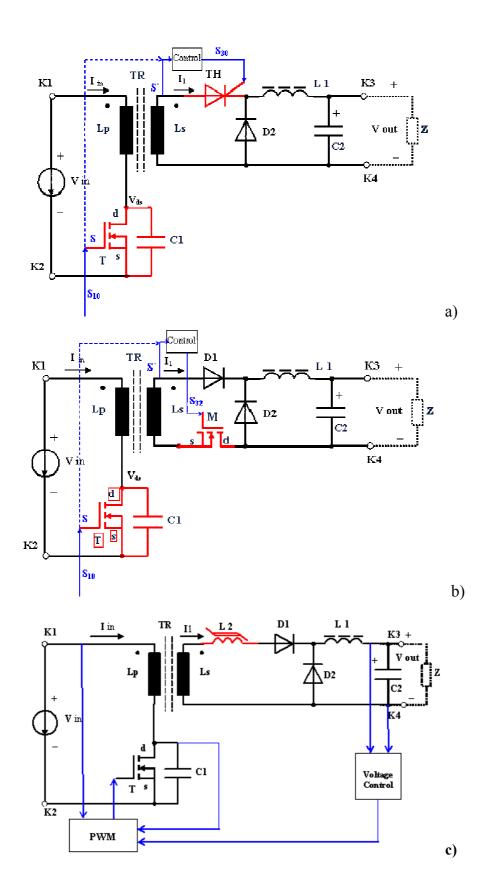

|   | 5.1 | Simplification of the topologies using SiC devices                    | 51       |

|   | 5.1 | .1 Choosing resonant reset forward converter                          | 53       |

|   | 5.2 | Analysis of the resonant reset forward converter                      | 59       |

|   | 5.2 | .1 Introduction                                                       | 59       |

|   | 5.2 | 2 Analysis                                                            | 60       |

|   | 5.2 | Operation at light-load and short-circuit condition                   | 65       |

|   | 5.2 | .4 Simulations for higher power and higher voltage levels             | 66       |

|   | 5.2 | .5 Obtaining Zero Voltage switching operation                         | 67       |

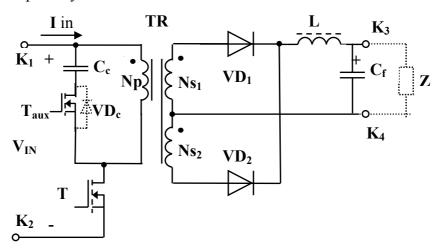

|   | 5.3 | Application of the SiC devices in alternative topology                | 72       |

|   | 5.3 | .1 Single switch double-ended Forward-Flyback converter               | 72       |

|   | 5.4 | Comparative study of the single switch and multi-switch topologies    | 74       |

|   | 5.5 | Summary                                                               | 79       |

| 6 | Ga  | te driver for the SiC VJFET                                           | 80       |

|   | 6.1 | Introduction                                                          | 80       |

|   | 6.2 | Current and voltage requirements                                      | 80       |

|   | (   | Gate voltage                                                          | 80       |

|   | (   | Sate power                                                            | 81       |

|   | 5   | Signal isolation and transmission                                     | 81       |

|   | 1   | Negative and positive voltage overshoot protection                    | 81       |

|   | S     | hort circuit and overcurrent protection                                        | 81           |

|---|-------|--------------------------------------------------------------------------------|--------------|

|   | 6.3   | Driving with negative voltage bias                                             | 82           |

|   | 6.4   | Driving JFETs in Cascode circuit                                               | 87           |

| 7 | Pro   | totype of 1kW resonant reset converter                                         | 89           |

|   | 7.1   | Design and dimensioning of the converter                                       | 89           |

|   | 7.1.  | 1 Power stage                                                                  | 89           |

|   | 7.1.  | 2 JFET gate driver for high temperature operation                              | 94           |

|   | 7.1.  | Saturable reactor and magnetic amplifier post-regulator                        | 95           |

|   | 7.2   | Efficiency                                                                     | 99           |

| 8 | Cor   | nclusion and future work                                                       | 101          |

|   | 8.1   | Summary                                                                        | 101          |

|   | 8.2   | Suggestions for future work                                                    | 103          |

| 9 | Ref   | erences                                                                        | 104          |

| A | ppend | X                                                                              | 113          |

|   | A     | 1 Derivation of the main characteristics for single switch Forward a           | ınd Flyback  |

|   | c     | onverters                                                                      | 113          |

|   | A     | 2 Detailed operation analysis of the resonant reset forward converter          | 119          |

|   | N     | MathCAD Program listing with comments                                          | 120          |

|   | C     | Derivation of the VI characteristics of the $L_{leak}$ , $C_{DS, VD}$ resonant | ance circuit |

|   | d     | uring switching ON time                                                        | 132          |

|   | Γ     | 1 Derivation of the transfer function                                          | 134          |

|   | E     | 1 Power switching device voltage and current stresses                          | 135          |

|   | F     | 1 Power Transformer Calculation                                                | 136          |

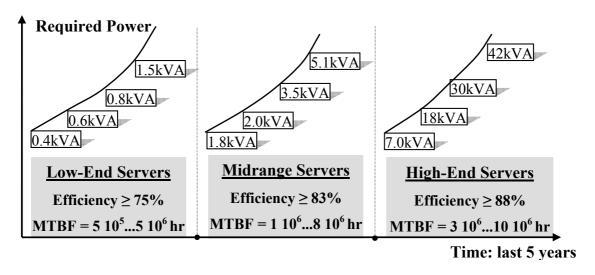

|   |       | 31 Schematics of the demo board                                                | 139          |

#### **Used abbreviations**

AC Alternative Current

AC/DC AC to DC Converter

A/D Analogue to Digital

AlGaN Aluminum Gallium Nitride

APS Auxiliary Power Supply

APS Autonomous Power Station

BIFET Bipolar Injection Field Effect Transistor

CCM Continues Current Mode

CMOS Complementary Metal Oxide Semiconductor technology

DC Direct Current

DC/DC DC to DC converter

DCM Discontinues Current Mode

DPS Distributed Power System

DoE Department of Energy

DSP Digital Signal Processor

ESR Equivalent Series Resistance

ESL Equivalent Series Inductance

FET Field Effect Transistor

FB Full Bridge also H-Bridge

GaN Gallium Nitride

GTO Gate Turn Off switch

H-Bridge Full Bridge converter topology consisting of 4 switches

HB Half Bridge converter topology consisting of 2 switches

HF High Frequency

HV High Voltage

ICE Internal Combustion Engine

IEEE Institute of Electrical and Electronics Engineering

IGBT Insulated Gate Bipolar Transistor

IPM Integrated power modules

IPEM Integrated power electronics modules (future integrated systems)

JFET Junction Field Effect Transistor

LF Low Frequency

LV Low voltage

MCT MOS Controlled Thyristors

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MTBF Mean Time between Failures

P-N PN Junction

PE Power Electronics

PFC Power Factor Corrector circuit

PiN P intrinsic zone N diode

PSPICE PC Simulation Program with Integrated Circuit Emphasis

PWM Pulse Width Modulation

RMS Root Mean Square

Si Silicon

SiC Silicon Carbide

SIT Static Induction Transistor

SMPS Switch Mode Power Supply

SOI Silicon On Isolator

UPS Uninterruptible Power Supply

VLSI Very Large Scale Integration circuit

WBG Wide-Band-Gap

WWW World Wide Web

ZVS Zero Voltage Switching

ZCS Zero Current Switching

# List of tables

| Table 1.1 Automotive maximum ambient temperatures                                    | , |

|--------------------------------------------------------------------------------------|---|

| Table 2.1 Comparison of the silicon (Si) and wide bandgap power semiconductors14     | ŀ |

| Table 2.2 Summary of the known high temperature transistor technologies17            | 7 |

| Table 2.3 Fundamental topologies: Buck, Boost and Inverting converters20             | į |

| Table 2.4 The main characteristics of the Forward and Flyback topologies22           | 2 |

| Table 2.5 Main advantages and limitations of the common used SMPS topologies26       | 5 |

| Table 3.1 Capability of high temperature semiconductor technologies                  | 7 |

| Table 3.2 Maximum temperatures - bondpad-wire metallurgical combinations38           | 3 |

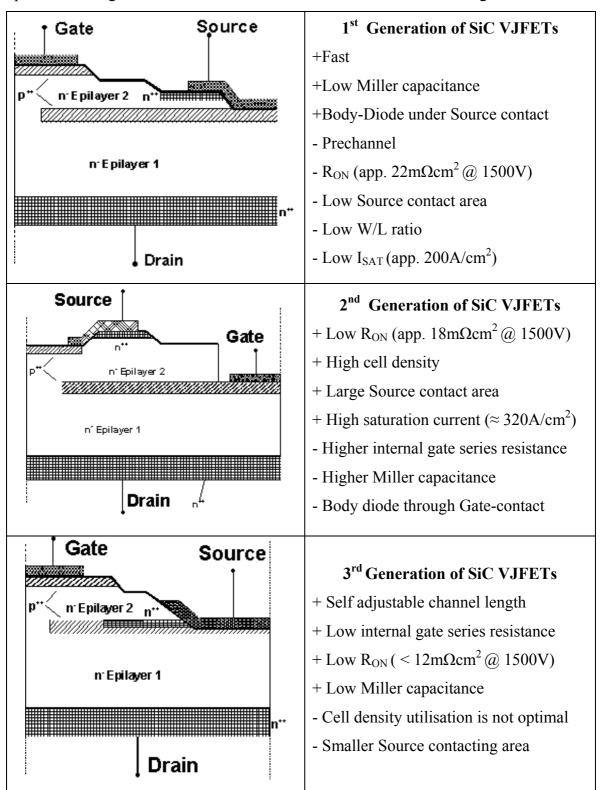

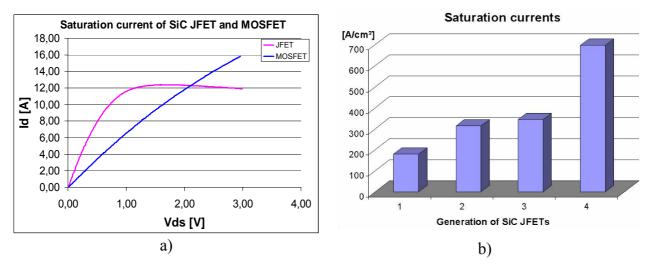

| Table 4.1 The 3 generations of the SiC VJFET transistors and their main properties42 | 2 |

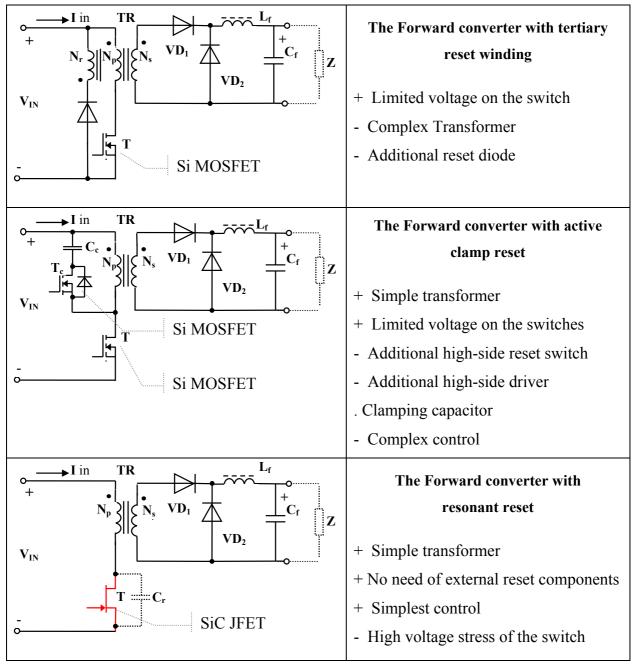

| Table 5.1 Different possibilities for transformer reset in Forward converter5        | 4 |

| Table 5.2 Properties of different forward topologies included parasitics             | 5 |

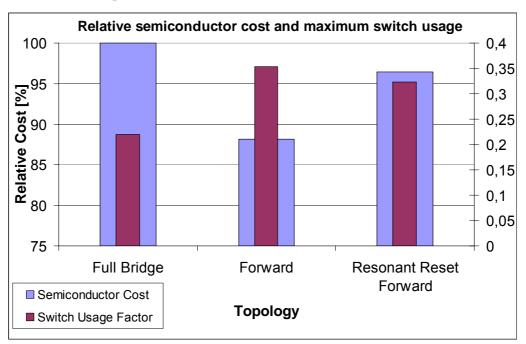

| Table 5.3 Active switch utilization of some common DC/DC converter5                  | 7 |

| Table 5.4 Comparative parameters of the double and single-ended converters           | 8 |

# **List of figures**

| Figure 1 1 Electrical properties of the SiC compared to the Si                             | 2  |

|--------------------------------------------------------------------------------------------|----|

| Figure 1 2 Distributed power system architecture                                           | 4  |

| Figure 1 3 Trends for AC/DC rectifiers:                                                    | 5  |

| Figure 1 4 GM EV1 - The Power Electronics in Hybrid Vehicles [GM]                          | 6  |

| Figure 1 5 Diagram of high voltage power bus and installed DC-DC converters                | 7  |

| Figure 1 6 Oil and natural gas demand, cost reduction of PV converters                     | 8  |

| Figure 1 7 Solar energy applications                                                       | 9  |

| Figure 2 1 Area specific ON resistance of SiC unipolar device, as figure of merit          | 12 |

| Figure 2 2 Schematic cross section of the SiC polytype and its 3D image                    | 13 |

| Figure 2 3 Progress in SiC Devices related to SiC material progress                        | 15 |

| Figure 2 4 Shorter drift layer in the SiC devices and area specific resistance             | 16 |

| Figure 2 5 Related voltage, current and frequency ranges for different power devices       | 18 |

| Figure 2 6 The secondary power supply converter tree                                       | 19 |

| Figure 2 7 Two stage architecture of front end rectifier                                   | 23 |

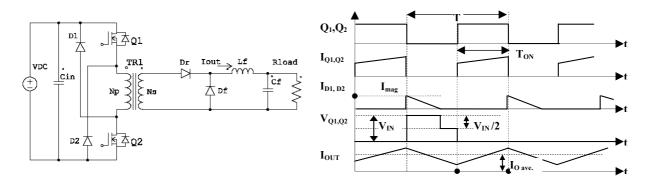

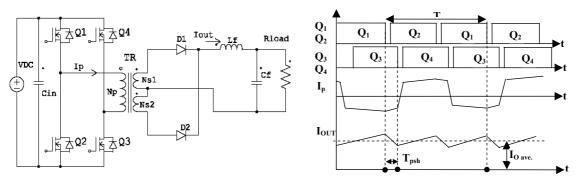

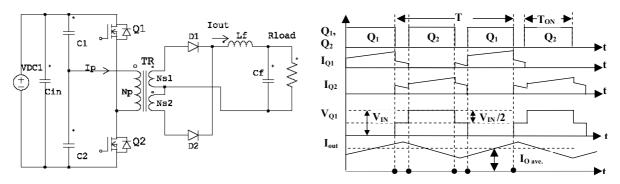

| Figure 2 8 Double switch forward converter and its switching waveforms                     | 24 |

| Figure 2 9 Full bridge phase shift converter and operating waveforms                       | 24 |

| Figure 2 10 The half bridge converter and its switching waveforms                          | 25 |

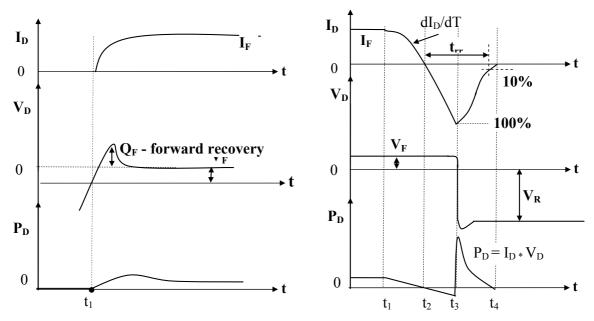

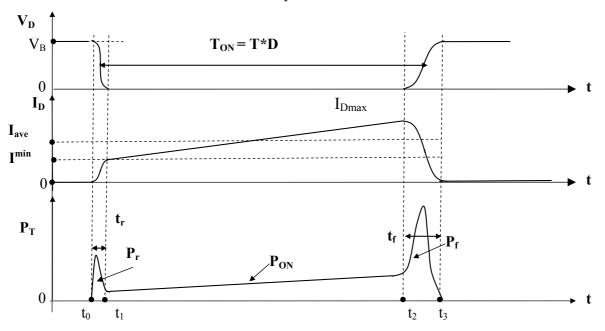

| Figure 2 11 Switching waveform of power diode                                              | 28 |

| Figure 2 12 Power transistor losses due to finite switching times and R <sub>DS</sub> (ON) | 29 |

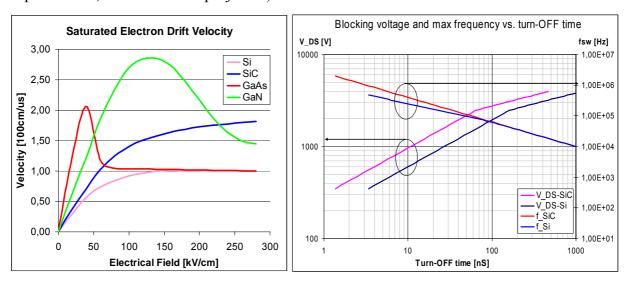

| Figure 2 13 Saturated electron drift velocity drastically decreased switching times        | 30 |

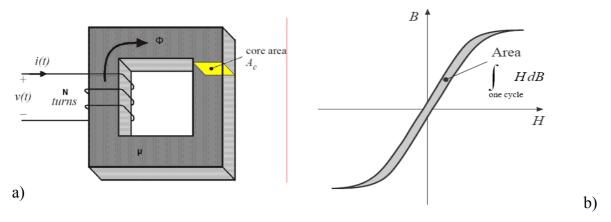

| Figure 2 14 Magnetic core model with flux Φ flowing trough area A <sub>C</sub>             | 31 |

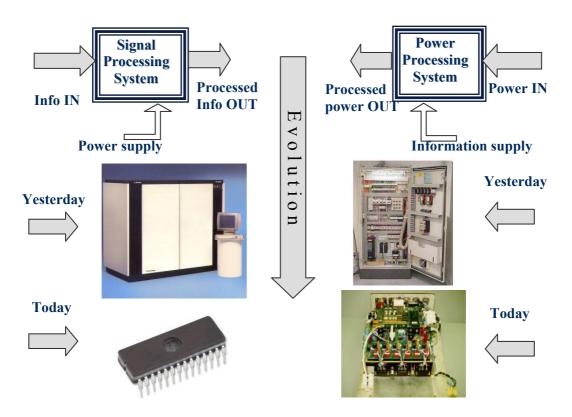

| Figure 3 1 A signal processing system contrasted with a power processing system            | 33 |

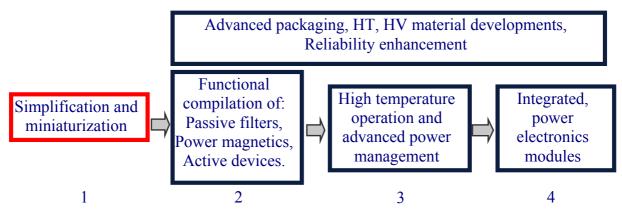

| Figure 3 2 A vision for integrated power electronics                                       | 34 |

| Figure 3 3 The simplified thermal model of the power chip                                               | 35 |

|---------------------------------------------------------------------------------------------------------|----|

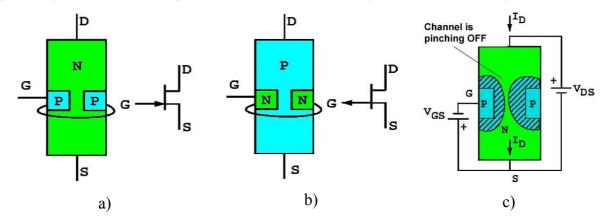

| Figure 4 1 The N and P channel JFET transistors and their operation principle                           | 39 |

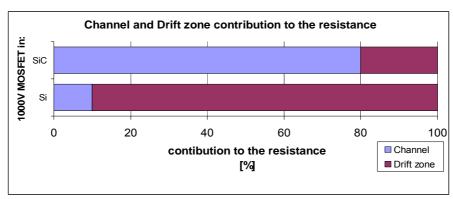

| Figure 4 2 The contribution to the ON-state resistance of MOS devices in Si and SiC                     | 41 |

| Figure 4 3 The Basic structure of the SiC JFET                                                          | 41 |

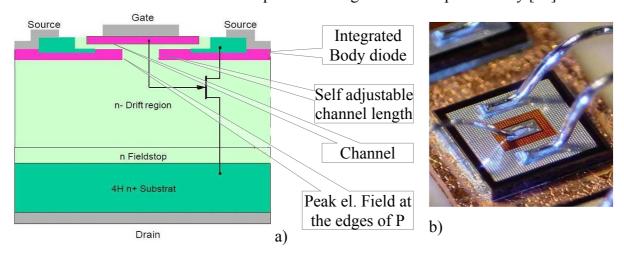

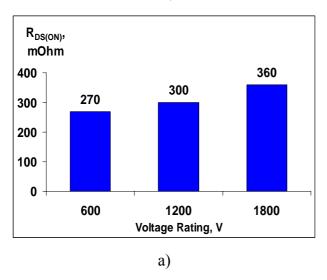

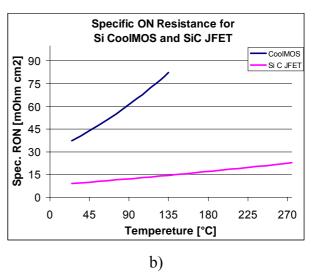

| Figure 4 4a) The ON state resistance of SiC VJFET for different blocking voltages                       | 43 |

| Figure 4 4b) Specific ON resistance of the SiC JFET and Si CoolMOS vs. Temp                             | 43 |

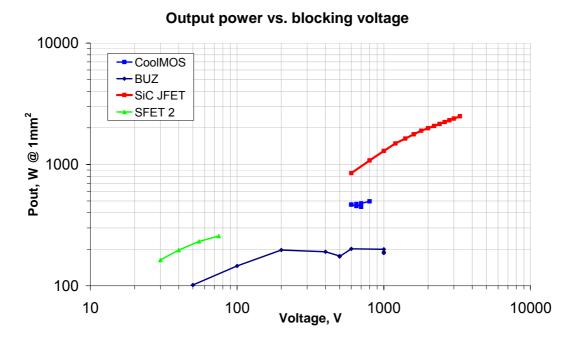

| Figure 4 5 Output power vs. blocking voltage for different power FET technologies                       | 44 |

| Figure 4 6 The output characteristics of the Si MOSFET and SiC JFET                                     | 44 |

| Figure 4 7 Phase leg setup with SiC JFETs and with external SiC reverse diode                           | 45 |

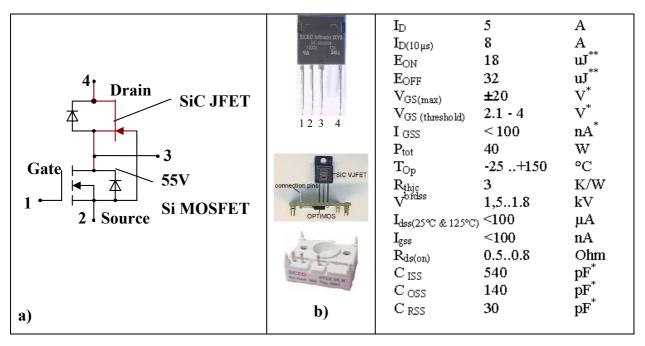

| Figure 4 8 SiC JFET in Cascode circuit and main characteristics.                                        | 47 |

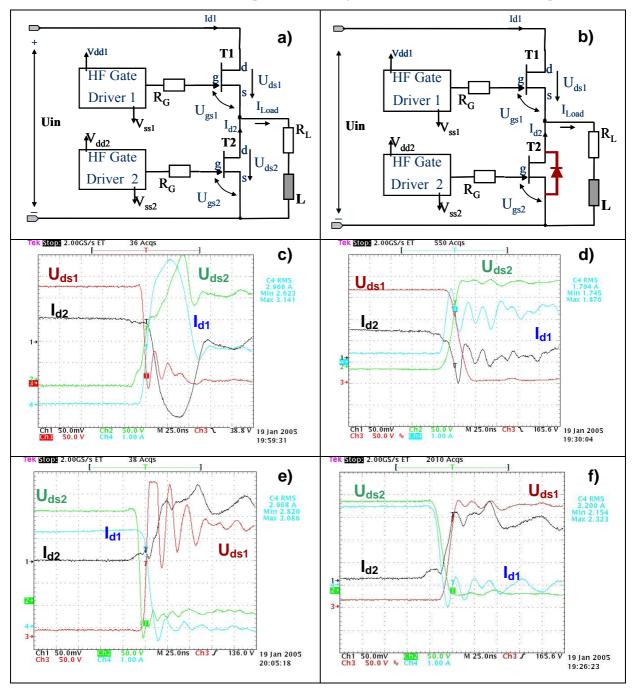

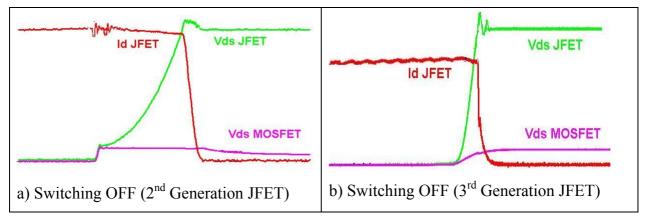

| Figure 4 9 Switching waveforms of the SiC JFET in Cascode configuration                                 | 48 |

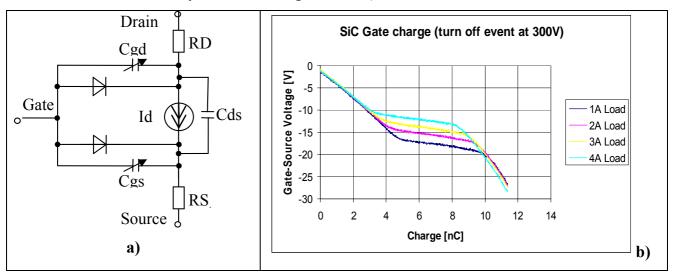

| Figure 4 10 The SiC VJFET equivalent circuit and its Gate charge                                        | 48 |

| Figure 4 11 Reverse biased gate leakage and PT currents of two JFET samples                             | 50 |

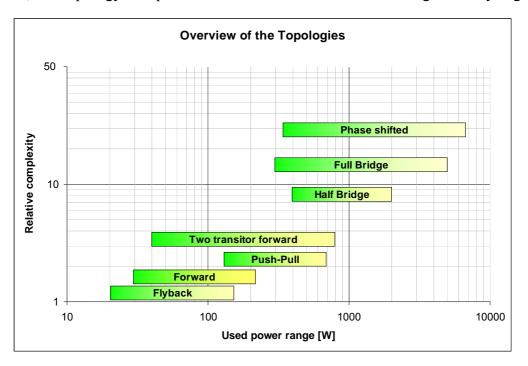

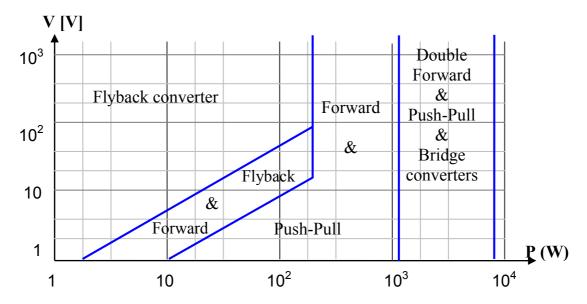

| Figure 5 1 Commonly used topologies for different power levels & their complexity                       | 51 |

| Figure 5 2 Output power and voltage ranges for different converter topologies                           | 52 |

| Figure 5 3 Relative semiconductor cost and maximum switch utilization                                   | 58 |

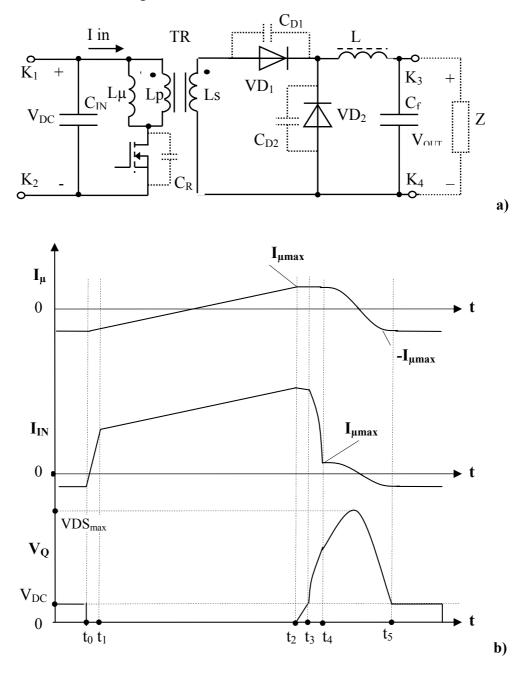

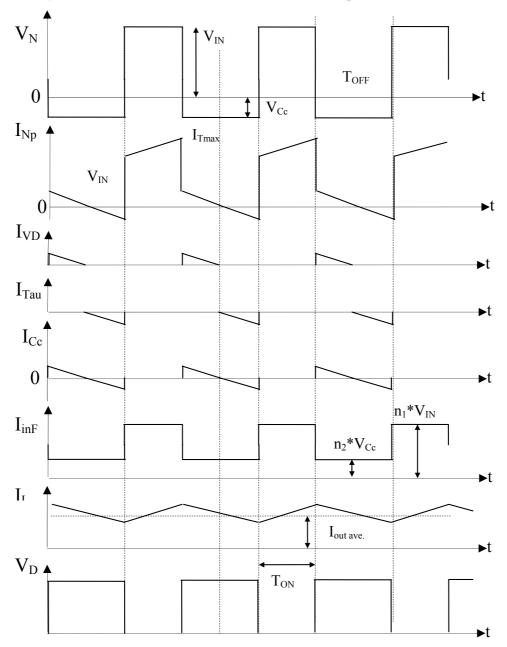

| Figure 5 4 Single-ended resonant reset forward converter and switching waveforms                        | 60 |

| Figure 5 5 Equivalent circuits of resonant reset forward converter in different states                  | 64 |

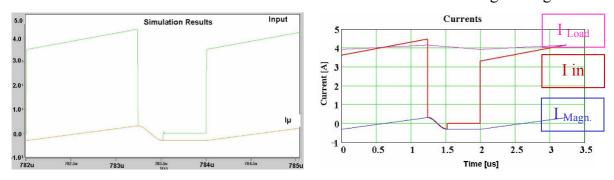

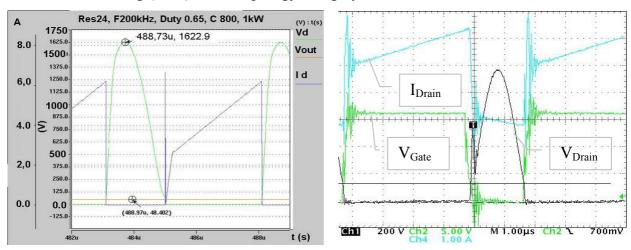

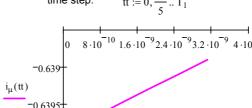

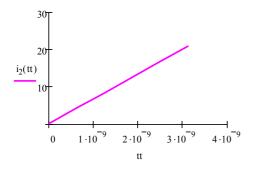

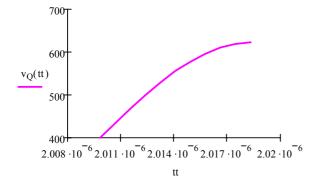

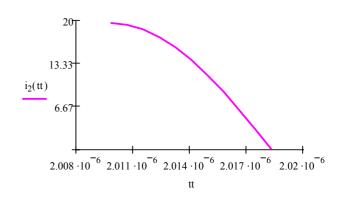

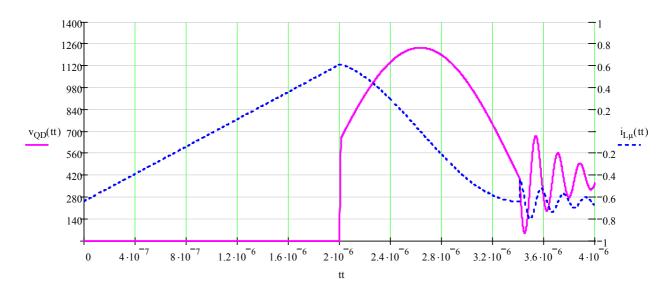

| Figure 5 6 Verification Results of calculations with Mathcad <sup>TM</sup> and with Saber <sup>TM</sup> | 66 |

| Figure 5 7 Simulation for higher drain voltages, switching losses and oscillations                      | 66 |

| Figure 5 8 Switching drain voltage and current under influence of parasitic elements.                   | 67 |

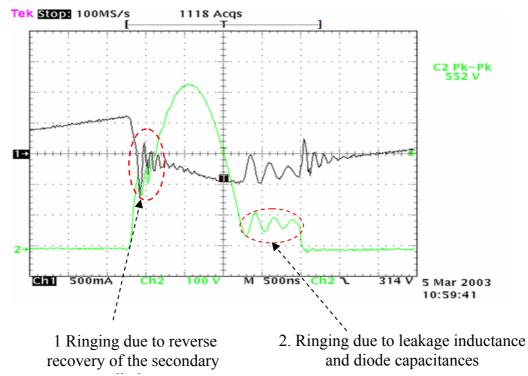

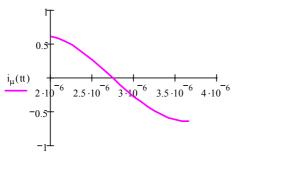

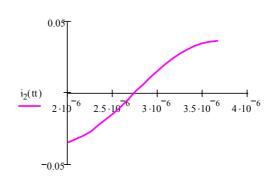

| Figure 5 9 Switching waveforms of the converter with SiC secondary side diodes                          | 68 |

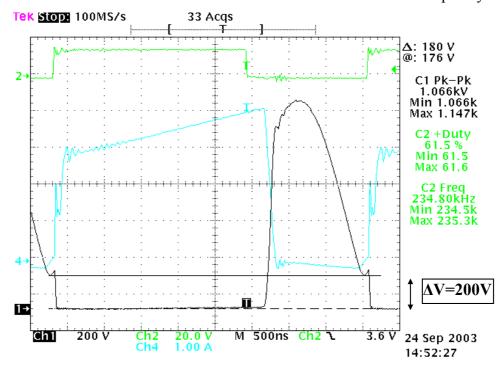

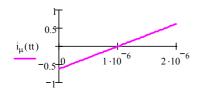

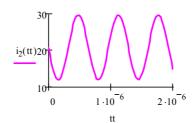

| Figure 5 10 The simulation results at higher duty cycle and low output power                            | 69 |

| Figure 5 11 Realization of the ZVS in resonant reset forward converter                                  | 71 |

| Figure 5 12 The composite double ended forward converter                                                | 72 |

| Figure 5 13 Switching waveforms of the single switch double-ended forward converter | 73   |

|-------------------------------------------------------------------------------------|------|

| Figure 5 14 Double-ended Forward – Flyback converter clamped through auxiliary      | 74   |

| Figure 5 15 Single-ended (resonant reset forward) and double-ended (push-pull) conv | 75   |

| Figure 6 1 Test setup with JFET gate junction diode.                                | 82   |

| Figure 6 2 On state voltage of the JFET vs. VGS @ constant drain current 4.8A       | 83   |

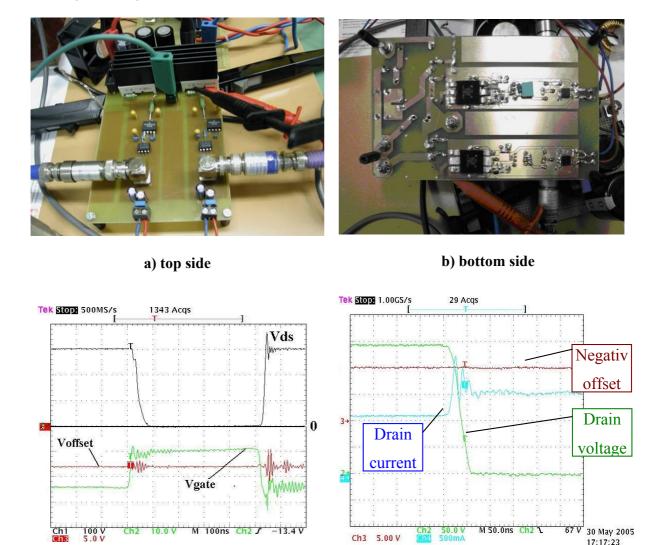

| Figure 6 3 The test board switching waveforms with offset voltage on the gate       | 85   |

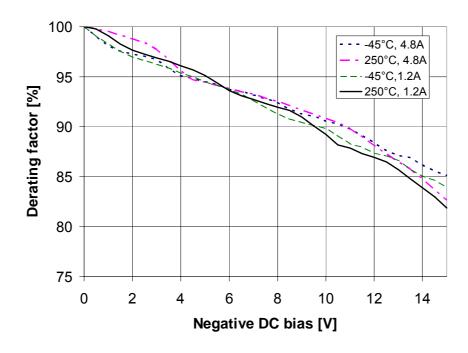

| Figure 6 4 Derating factor of the proposed driving scheme                           | 86   |

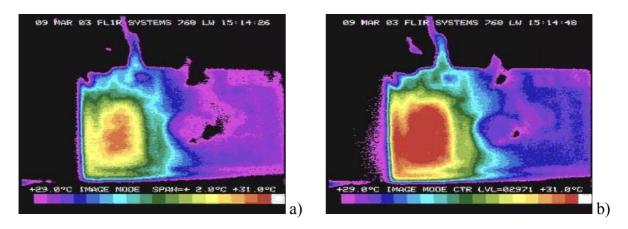

| Figure 6 5 Thermal image of the JFET die under switching conditions                 | 86   |

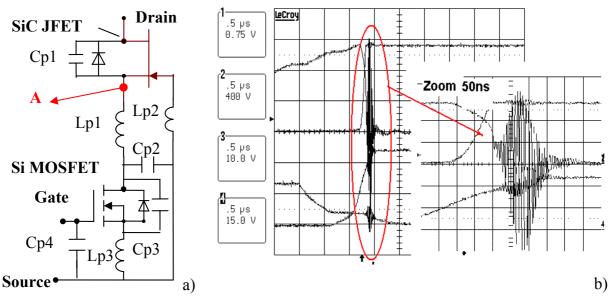

| Figure 6 6 The SiC JFET in Cascode configuration with LV Si MOSFET                  | 87   |

| Figure 6 7 The classical Cascode circuit a) and modified Cascode b)                 | 88   |

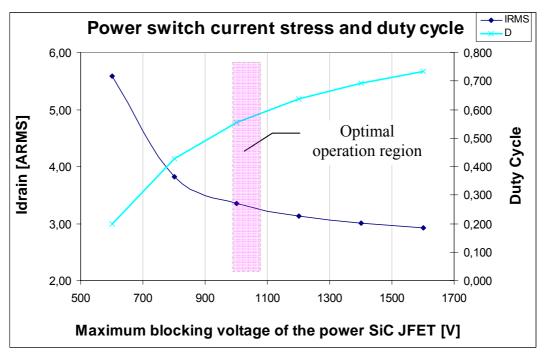

| Figure 7 1 The optimal operating area according with RMS current and duty c         | ycle |

| dependencies from the maximum demagnetizing voltage applied to the transformer      | 90   |

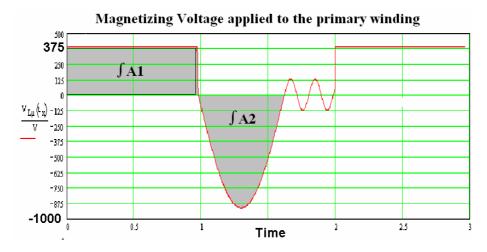

| Figure 7 2 The volt-second balance of the transformer.                              | 91   |

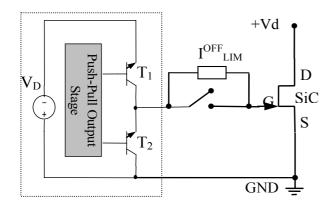

| Figure 7 3 Principal diagram of the avalanche gate driver.                          | 94   |

| Figure 7 4 Gate driver pulsed currents and switching waveforms.                     | 95   |

| Figure 7 5 The schematic the resonant reset forward converter with magamp           | 96   |

| Figure 7 6 The prototype board of the 1kW Resonant Reset Forward Converter          | 97   |

| Figure 7 7. Operation of the prototype converter under 260°C ambient temperature    | 98   |

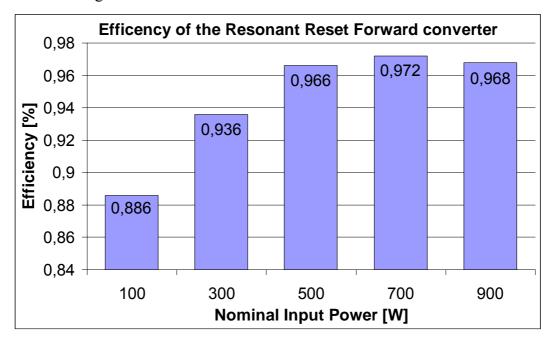

| Figure 7 8 Measured efficiency at 400V input and 48V output voltages                | 99   |

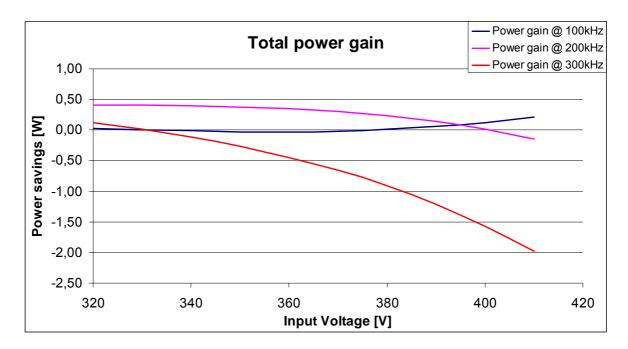

| Figure 7 9 Power loss savings vs. input voltage by using saturable reactor          | .100 |

#### 1 Introduction

## 1.1 Background and Motivation

The most important tasks in any power supply design procedure are:

- ✓ reduction of the power losses efficiency improvement and

- ✓ reduction of the size and weight together with increasing of the output power hence increase of power density.

However, there is no single solution for both tasks. The trade off between size, cost, weight and efficiency can not be exactly determined and is usually driven by market requirements. Finding a solution for one parameter is usually accompanied by shifting the problem to other parameters. For instance an improvement in secondary switch mode power supplies (SMPS) towards higher power density can be achieved mainly by reducing their passive components (transformers, inductances, capacitors, filters etc.), which is possible by increasing the switching frequency. Increase of the frequency is basically restricted by the limited high frequency capabilities of the switching devices leading to increased switching losses and, eventually, to decreasing of the efficiency. Although some known techniques allow further increase of frequencies in the common circuits (e.g. resonant converters), the resulting converter topologies become in many cases more complicated and for large input / load variations sometimes difficult to control and stabilize. In such cases increase of power density becomes less evident, because during comparisons all the peripheral components, like control circuitry, snubbers, input and output filters, heatsinks etc. should be taken into account. Complex, sometimes with DSP controlled power converter systems are becoming increasingly costly.

Control and topology simplicity are the product differentiators of today's power converters and for mission critical, high temperature and harsh environment applications these properties are mandatory.

In contrast, reduction of the switching losses can be achieved also with lower switching frequencies and utilizing novel multilevel topological solutions, which can additionally increase the system reliability [62], [95]. Nevertheless, extremely reduced switching frequency could impact the overall power density, making such converters suitable for specific applications only

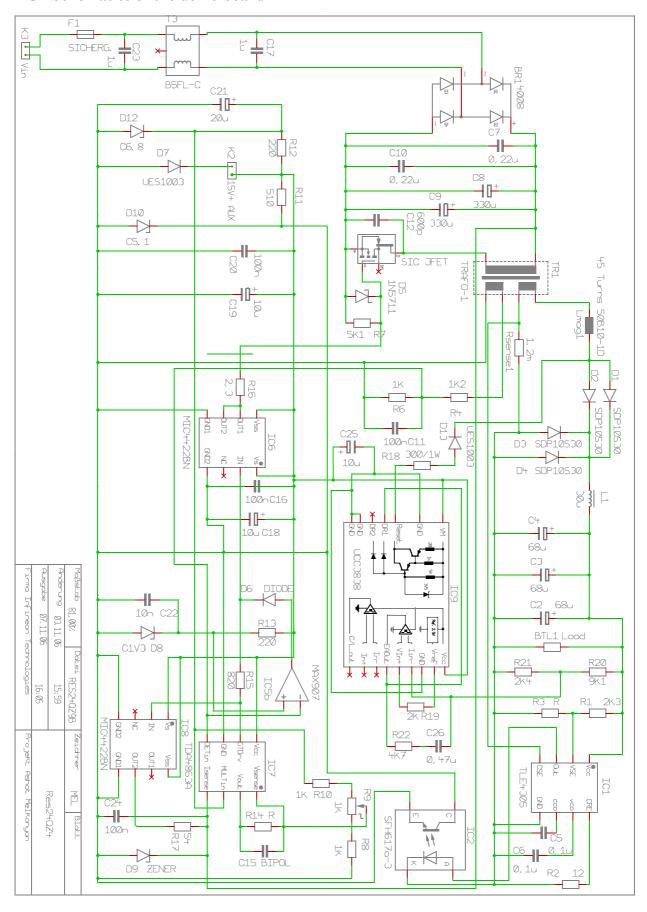

On the other hand, the power semiconductor development has recently shown big achievements in wide band-gap (WBG) technology and in related power devices [11]. Silicon carbide, being the most feasible semiconductor for power devices, has received a lot of attention during the last decade. The very high eclectic breakdown field makes it most suitable semiconductor for using in high power devices (Figure 1-1). Because of

Figure 1-1 Electrical properties of the SiC compared to the Si; values are normalized

much higher allowable electrical field, active devices like rectifiers and switches can be designed with more then ten times thinner and shorter semiconductor structures (drift layers) resulting in very much lower specific on-state resistance. In principle, SiC offers not only higher breakdown voltage, but also higher thermal conductivity, higher saturated electron drift velocity and inherent ability to operate at much higher junction temperatures because of the low intrinsic carrier concentration associated with the wide band-gap (WBG) [65], [77], [98]. All of these is well known and widely documented in the recent literature. What is less documented, is how these properties to transform into device or system benefits that silicon power electronics can not realize, – this is the main subject of this thesis. Among already commercially available SiC Schottky barrier diodes (SBD) from Infineon [107] and Cree [107], within past two years also SiC power transistors - SiC

JFETs from SiCED [14]<sup>1</sup> became available as samples for research and development. However, due to technological constrains the price and production cost of SiC devices will remain always higher then the production costs of Si counterparts [6]. Additionally the unknown properties of the SiC transistors slow down the expected large and fast market acceptance. After replacing the Si power transistors and diodes in the commonly used SMPS topologies by high speed, high voltage, high temperature but also rather expensive SiC counterparts, designers were not able to see "the big" efficiency or power density improvements. Moreover, the higher cost and complexity of the resulting converters were dominant.

A question rises – how and in which power converter topologies the SiC power devices can be effectively utilized? Which properties of SiC devices allow increasing the power supply performance?

It becomes necessary to find out another approach in the design procedure of the well adopted converter topologies: - settled hierarchies of the applicable power ranges in the different topologies and design selection decisive factors are less suitable for the implementation of the new power devices like SiC JFETs. Many simple, single-switch topological solutions had been considered in former time as "not applicable" for higher power ranges because of lack in fast, high frequency and high voltage power transistors. In order to overcome the maximum allowable drain voltage limitations of existing MOSFETs, so called multi-switch topologies are utilized, where the applied voltage is blocked by either series connected lower voltage transistors or by clamping the drain voltage to the input voltage level. Today, when the SiC devices are available, it should be verified, whether the single switch topologies can be revived and favorably used. With putting them in practice, the overall power system will become simpler and, despite of used expensive SiC device, can be more economical. By using system relevant approach for the power supply design the system efficiency as well as reliability could be drastically increased.

<sup>-</sup>

<sup>&</sup>lt;sup>1</sup> As of February 2002 to December 2003 the SiC JFETs from SiCED GmbH, were only available silicon carbide transistors for R&D in Europe

<sup>&</sup>lt;sup>2</sup> "high" is considered as over 500W. The separation of switch mode power supplies in "low" power and "high" power in this thesis is given informally.

#### 1.2 Application requirements & trends

Among the main requirements, such as high efficiency and power density, every electrical or electronic application has its own, specific requirements to the power supply. Targeting to general switch mode power supplies, in the following we will shortly review some challenging application areas like telecom, automotive, energy applications and point out whether and how SiC devices can be used for their performance increase.

#### 1.2.1 Telecom application requirements

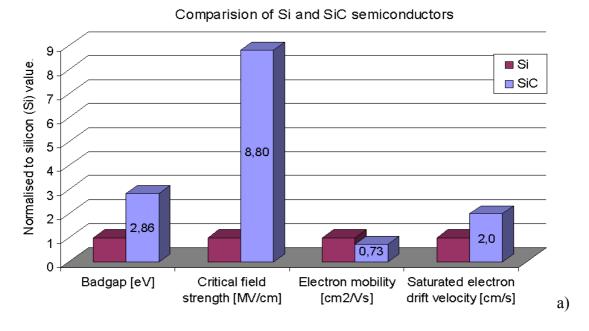

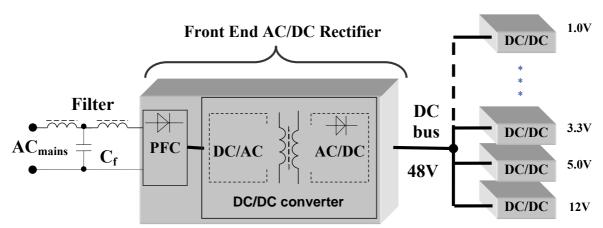

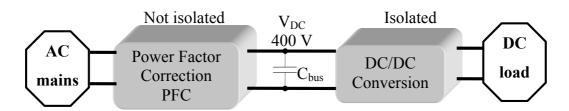

In the vast variety of server or telecom power supplies, the so called Distribute Power System (DPS) are widely adopted. In such systems, power is processed by two stages. Firstly the mains AC input is rectified, boosted up to 400V DC level then converted back and regulated to 48V intermediate DC bus by front end converter. In the second stage this DC voltage is distributed to the loads by the DC/DC non-isolated converters. The simplified block diagram of the commonly used DPS is illustrated in Figure 1-2

Figure 1-2 Distributed power system architecture with isolated AC/DC rectifier providing 48V DC bus, which is loaded with DC/DC non-isolated point of load (POL) converters

The main challenges in this application are following:

Firstly, by increasing of integration degree in digital electronic, more and more transistors are integrated to the system with faster switching frequency (VLSI). The power demand of digital system is increasing dramatically. The power supply, as a supporting subsystem, also expected to be less expensive and provide more power with smaller volume – increase of power density becomes essential part of any new development of power converter for telecom applications.

With integration of digital electronics, the profiles of the systems which are to be installed in racks are becoming another driving tendency in industry. More and more digital systems becoming highly integrated and, therefore, can be built with very low profiles. Consequently it is intended to have the system power supplies in low profile too in order to be mechanically compatible with digital components and systems. Nowadays the systems normally have a profile of 1.5U (1U ~ 4cm), and the tendency is moving towards 1U power systems [85]. In Figure 1-3, the trends for output power density,

Figure 1-3 Trends for AC/DC rectifiers: During the last 5 years the power demands in each server category are increased 4-6 times accompanied with 5% efficiency increase.

efficiency and lifetime (MTBF) are shown over the past 5 years. For each server category the power demand has increased almost 4 times, for high-end servers even 6 times. The efficiency needs to be increased by more than 5%. To achieve this improvement 30% to 50% reduction of system power loss is required [85]. From above discussions can be concluded, that the trend for power supplies depends from digital system evolutions. During last few years, the digital systems shrunk more then tenfold. However miniaturization and integration of the power supplies for server/telecom applications with currently available technologies is hardly possible. Shrinking the volume and space will cause an increase of environmental and operating temperatures of the components. There is an obvious need of new semiconductor technology, which is inherently suited for elevated temperature operation. Correspondingly, new cooling or temperature management systems together with high temperature packaging are becoming mandatory. Important to note, that an integration and tight packaging of today's complex converters is hardly possible. The simplification of the topologies should be the first step towards integrated power electronics modules - IPEM [59]. This aspect will be discussed in Chapter 5.1. The

issues with high temperature passive components and packaging will be briefly reviewed in Chapter 3.

#### 1.2.2 Automotive application requirements

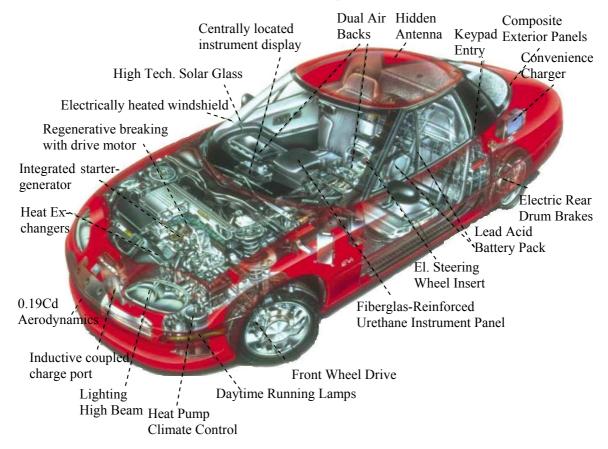

During the last few years the requirements for transportation electronics have been drastically changed, attracting the automotive industry towards mechatronics (integration of electronics and mechanical systems, e.g. electronics in transmission). Figure 1-4 [General Motors] illustrates the emergence of electronics in automotive branch, where the DC/DC and DC/AC power converters are becoming inevitable part of present and future vehicles. On the other hand, they are also considered as one of the critical parts, which contribute to the mass and volume of the vehicle, and correspondingly have the direct influence on the acceleration and overall efficiency of the vehicle.

Figure 1-4 GM EV<sub>1</sub> - The Power Electronics in Hybrid Vehicles [GM]

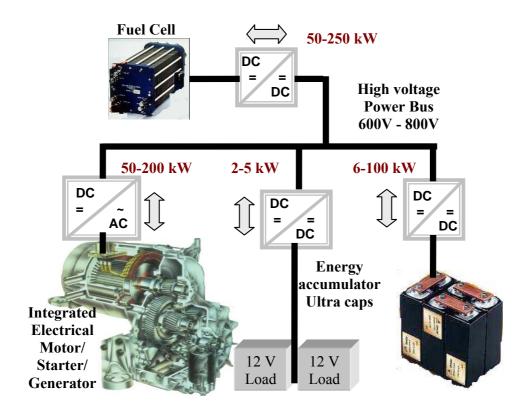

The schematic diagram illustrated in Figure 1-5 shows where in vehicle the electrical power conversion takes place, as well as installed type and power levels of the converters. High temperature power electronics rated at temperatures well above 125 °C would eliminate present-day box placement design constraints.

Figure 1-5 Schematic diagram of high voltage power bus and installed DC-DC and DC-AC converters for different power levels in hybrid electrical vehicle

This will reduce the number of wires and connectors in the engine, which can improve long-term reliability. X-by-wire systems (X- throttle, steer, shift, brake etc.) are under development, and will dominate in future vehicles [74]. Also elevating the operating temperature of power devices up to 150°C will simplify the temperature management by using common cooling systems both for power electronic (PE) and internal combustion engine (ICE). Table 1-1 shows some ambient temperature ranges in automotive applications [25], [83]. The major source of heat affecting the vehicular electronics is the heat generated by the active devices, especially by the power semiconductors themselves.

| Under -hood     | 100-125 °C | On Wheel | 150-250°C          |

|-----------------|------------|----------|--------------------|

| On-Engine (ICE) | 150-200°C  | Cylinder | 200-300°C          |

| In-Transmission | 150-175°C  | Exhaust  | 850°C, ambi. 300°C |

**Table 1-1 Automotive maximum ambient temperatures**

Because of high currents and high frequencies both the conducting and the switching losses are contributing to the overall temperature increase. The amount of losses dependents mostly on the type of power devices used. Due to limited power capability, the unipolar MOSFETs are not used in today's traction drives, but IGBT and PiN diodes.

However, bipolar devices have limited switching frequency range and generally higher switching losses compared to the MOSFETs and Schottky diodes. Having high breakdown voltages (over 1200V) and high switching frequencies yet keeping ON-state resistance very low in Si MOSFET is hardly possible, - a material with a higher electric breakdown field is required. The SiC could be the best suited semiconductor, where its inherently high operating temperature capability together with high breakdown voltage and switching frequency can be advantageously utilized.

#### 1.2.3 Requirements in energy and in harsh environment applications

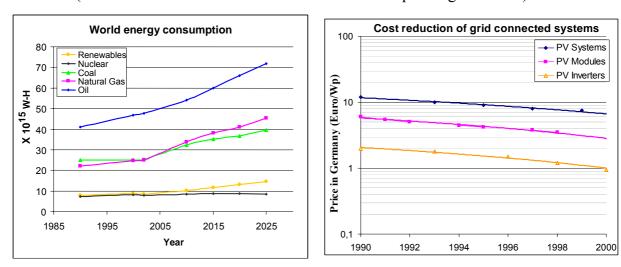

Energy is the most important aspect for economic and national security. The world-wide energy demand will continue to rise. According to Department of Energy projections (DoE) [38], next twenty years the natural gas and oil will be still the dominant source of energy, despite of alternate energy sources: Figure 1-6. However, the easy recoverable oil and gas will be diminishing in supply, and their recovery will be from deep wells. In the well with hundreds of kilometers depth, the temperature is varying from 180 °C to 450 °C and more (180° C is considered minimal for direct electric power generation.).

Figure 1-6 a) Next years the oil and natural gas will remain as dominant source of energy [38]. b) The cost reduction of PV converters shows the same tendencies as for PV modules, making power converter developers to find out simple and cost competitive solutions [96].

Presently, there is no any electronic hardware system or module that can survive in such a harsh, high temperature and high pressure environment and the drillers have to explore these depths without an appropriate instrumentation. Drilling in this manner is very costly, slow and inaccurate. Currently geothermal industry uses a Dewar-flask a (double-walled evacuated housing) that protects the internal electronic power supplies and sensors for

approximately 10 hrs within a 300° C. Taking in account that the voltage references are limited today up to 150 °C and most passive devices up to 180 °C, the power supply with less components and simplest topology together with high temperature active devices can gradually improve the situation.

Power electronics converters are already an integrated part of the whole renewable energy system. The accelerated growth of energy development from renewable sources sets increased demand on the high efficiency, reliable and high power density converters. The learning curve of the converter cost reduction Figure 1-6 b) [96], shows the same tendencies as for PV modules, which stimulate designers to find out innovative, simple and cost effective power supply solutions. In rural and hard accessible regions the solution for 1kW power supply is the autonomous photovoltaic station [80]. In these regions, such systems are mostly installed for public live supply and medical care net, therefore only reliable and maintenance free uninterruptible electrical power systems (UPS) can be used.

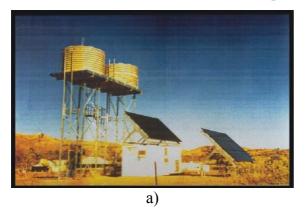

Figure 1-7 Solar energy applications, where the maintenance cost of any component can be unacceptable high. A) Alpine cot Ponti in Italy and b) Water supply station in Australia [80]

Figure 1-7a) shows the water supply station (part of a 4kWp hybrid system) for a small commune in central Australia located some hundred kilometers far from the next town Alice Springs. Some places are so hard to access, that every visit for maintenance is extreme cost-intensive Figure 1-7 b) shows the PV supplied Alpine cot Ponti in Italy, which is possible to reach only with helicopter. In such systems additional investment in compact, highly integrated autonomous power supplies, which are free from the regular upholding, is beneficial. The power converters realized with SiC, which can be integrated in future high temperature robust modules, will allow eliminating the mechanical moving parts such as fan cooling. Resulting converter will be maintenance—free, with increased reliability, and better suited for mentioned renewable energy applications.

## 1.3 Thesis objective

The objective of this thesis is to investigate the new SiC devices and find out a suitable topology, where the specific properties of the SiC devices are fully utilized.

After building a prototype converter with implemented SiC devices, the topology simplification, higher efficiency and higher power density should be obtained, which will provide a solution for future integration of the converters into high temperature integrated power electronics modules.

The following aspects should be studied:

- 1. Evaluation and characterization of the SiC JFET transistors to find out the properties which allow increasing power converter performance.

- 2. Determination of the SiC converter design technique how to fully utilize the potential of SiC semiconductor in power converters while simplifying their topology

- 3. Investigate possible driving approaches of the SiC JFET in suitable topologies

- 4. Build up a prototype converter with silicon carbide power devices for performance evaluation and verification.

#### 1.4 Outline of the thesis

The dissertation is organized as following:

**Chapter 1** has reviewed 3 challenging applications backgrounds:- Telecom, automotive and harsh environment energy applications. Their issues and specific requirements are identified.

Chapter 2 will review the development roadmaps both for the semiconductor technology and for power converters. Classification of converter topologies and power losses which can be reduced by means of SiC devices will be studied.

In **Chapter 3** the vision towards miniaturization, integration and high temperature operation in power electronics and main obstacles to achieve this target will be presented.

**Chapter 4** will introduce the new SiC vertical junction field effect power transistor (SiC VJFET) and will investigate its specific properties.

In **Chapter 5**, the implementation of the SiC transistor in the power converters will be investigated, and possible simplification of the existing topologies will be proposed. This chapter examines some suitable topologies in order to fully exploit the possibilities of SiC transistors and diodes, especially towards operation with higher voltages and higher frequencies.

Chapter 6 describes the realization of two new gate drive circuits for driving SiC JFETs

**Chapter 7** concentrates on the practical design, dimensioning and experimental results of the prototype converter

**Chapter 8** summarizes the most important findings in this thesis and concludes the work with suggestions for future investigations.

#### 2 State of the Art

#### 2.1 Roadmap of power semiconductor devices

#### 2.1.1 Wide band-gap semiconductors

Silicon power devices are reaching their fundamental limits of performance J. Baliga, 1992.

Imposed by the low breakdown field of silicon, power switching devices have reached their fundamental limits: Figure 2-1. Significant improvements can only be achieved by going to semiconductors with higher breakdown fields – wide band-gap semiconductors. Recent progress in a manufacturability of WBG power device technology shows that within the next 2 years two families can be available: SiC and GaN, whereas the SiC is the most mature and the closest to market. GaN and AlGaN also have high breakdown field and high carrier mobility, and could be ideally suited for power device implementation. However, the II-V nitride compounds do not possess a native oxide similar to SiO<sub>2</sub>,

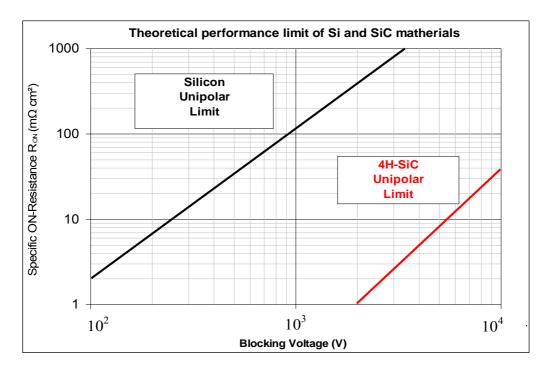

Figure 2-1 Area specific ON resistance of SiC unipolar device, as figure of merit, shows theoretically 400 times better voltage breakdown capability then Si counterpart [11]

therefore true MOS devices will not be feasible in near future [9]<sup>3</sup>. A good overview of the wide-band-gap (WBG) materials and the latest devices based on them including SiC transistors can be found in [11]. Numerous studies are carried out by NASA Glenn SiC Research Group and reported in e.g. [8], [109].

#### 2.1.2 SiC technology and properties of the SiC

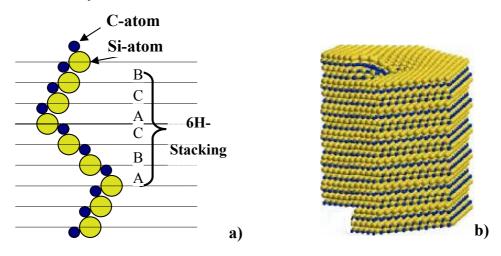

The SiC crystals chemically consist of 50% carbon atoms covalently bonded with 50% silicon atoms. There are over 100 different crystal structures (polytypes), each SiC polytype has its own distinct set of electrical semiconductor properties. However, only few polytypes are used for semiconductor production, - the cubic 3C-SiC, hexagonal 4H-SiC and 6H-SiC. The letter indicates the geometrical form of the crystal structure and the number shows the stacking sequence (see Figure 2-2a).

For example the 15R-SiC is the most common of many possible SiC types with a rhombohedral crystal structure.

Figure 2-2 a) Schematic cross section of the SiC polytype and b) its 3D image [8]

The most important electrical and thermal properties of SiC together with other common semiconductor materials, summarized from [9], [19] and [36] are given in the comparison Table 2-1. The SiC's superior properties have been known for decades; however, only reproducible wafers of reasonable size, quality and price are important for mass-production of semiconductor electronics. Si can be easily melted and again recrystallized, e.g. by Czochralski method, whereas the SiC sublimes instead of melting. This was the

<sup>&</sup>lt;sup>3</sup> The literature survey of WBG semiconductor technology was carried out during 2002-2004. Recent publications have shown devices having quasi MOSFET behavior and normally off condition in certain operating ranges.

major obstacle for mass production. The first breakthrough technology for reproducible 6H-SiC crystal growth was established by Tairov and Tzvetkov in 1970's, called modified seeded sublimination growth [15]. Though the first 1-inch 6H-SiC wafer became commercially available already in 1989, the 4H-SiC with its substantially higher carrier mobility is the favourable choice for today's devices. Furthermore, 6H-SiC shows an inherent electron mobility anisotropy, which degrades the conduction parallel to the crystallographic c-axis, consequently for vertical power devices the 4H-SiC is the best choice. In 1993 the Cree Research LTD (D. J. Larkin, and J. A. Powell under NASA funding) first provided to market 2.5cm diameter 4H-SiC wafers. Same time T. Urushidani et. al. have presented in [52] a high voltage Schottky barrier diode blocking 1100V. This was the first milestone which increased the pace of industrial utilisation of SiC.

| Electrical Property                                | Si   | GaAs | SiC<br>(4H) | SiC<br>(6H) | GaN<br>(2H) | Diamond |

|----------------------------------------------------|------|------|-------------|-------------|-------------|---------|

| Band-gap Eg [eV]                                   | 1.12 | 1.42 | 3.28        | 2.96        | 3.4         | 5.5     |

| Critical electrical field E <sub>Cr</sub> [MV/cm]  | 0.29 | 0.3  | 2.5         | 3.2         | 3.3         | 20      |

| Relative dielectric constant [E]                   | 11.9 | 13.1 | 9.7         | 9.7         | 8.9         | 5.7     |

| Electron mobility $\mu_n$ [cm <sup>2</sup> /Vs]    | 1200 | 8500 | 800         | 370         | 1000        | 2200    |

| Hole mobility μ <sub>p</sub> [cm <sup>2</sup> /Vs] | 490  | 320  | 115         | 90          | 30          | 1800    |

| Thermal conductivity λ [W/cmK]                     | 1.5  | 0.5  | 3.8         | 3.8         | 1.3         | 20      |

| T <sub>max</sub> [K]                               | 400  | 460  | 873         | 873         | 900         | 2200    |

| Commercial wafer diameter [cm]                     | 30   | 15.4 | 7.62        | X           | 5.0         | 1.2     |

Table 2-1 Comparison of the silicon (Si) and wide band-gap power semiconductors: Gallium Arsenide (GaAs), Silicon Carbide (SiC), Gallium Nitride (GaN) and Diamond.

Unfortunately, being a very "hard" semiconductor material, SiC often contains several crystal defects, whereas the most harming is the "micropipe" defect. It prevents the increase of defect-free wafer diameter, which directly affects the SiC electronics capability. A micropipe is a screw dislocation with a hollow core (a cave diameter on the order of micrometers) in the SiC wafer that extends roughly parallel to the crystallographic c-axis [7]. SiC wafers also contain high density of closed-core defects, which like micropipes, cause a localized strain and SiC lattice deformation [7], [13]. In addition to micropipe defects, there are also non-hollow core (elementary) screw dislocation defects in SiC wafers and epilayers.

While these defects are not considered as fatal as micropipes<sup>4</sup>, recent experiments have shown that they degrade the leakage and breakdown characteristics of P-N junctions: [10], [50] and [86]. Considering permanent defect density reduction, overall wafer quality improvement and consequent increase of device chip area, the power handling capability will grow exponentially until 2010 and, according to Ohashi [87], can reach 500kVA by 2018 (see Figure 2-3).

#### Rodmap of SiC Devices & SiC Wafer Quality 1000 100,00 Device Rate 5.0kV, 100A (Active chip area) Device Killer Defect Density 3.3kV, 150A Power Handling Capability 2.5kV, 100A 1.2kV, 200A (100mm<sup>2</sup>) 10,00 100 (64mm<sup>2</sup>) 1.2kV, 70A Power handling 600V, 100A Defect density (36mm<sup>2</sup>) 1,00 10 600V, 10A (4mm<sup>2</sup>) 0,10 2002 2004 2006 2008 2010 2012 2014 2016 2018 2020 2022 Years

#### Figure 2-3 Progress in SiC Devices related to SiC material progress as enabling technology [87]

## 2.1.3 Power switching devices based on SiC semiconductor

#### **MOS Devices**

SiC is the most attractive compound semiconductor, because of its native oxide is  $SiO_2$  – comparable to oxides used in Si MOSFETs [4]. This means that the main power devices made-up in silicon, i.e. the power MOSFET, insulated gate bipolar transistor (IGBT), and MOS-controlled thyristor (MCT) can be fabricated in SiC too. However, because of technological differences, power devices in SiC will be very different from silicon devices, and a direct translation of silicon concepts to SiC is not always possible. As can be seen from Table 2-1 the SiC has a breakdown field app.10x higher than silicon,

<sup>&</sup>lt;sup>4</sup> As of 2003 the micropipe crystal defects were biggest challenging task in SiC production. Recently Japan researches (H. Ohashi) have shown virtually defect free SiC wafers (EPE2005, CIPS 2006).

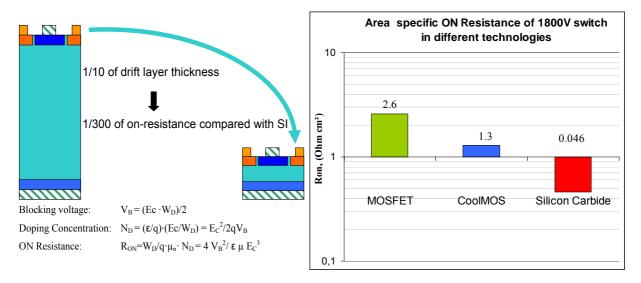

resulting to SiC power devices with very short depletion width W<sub>D</sub> (Figure 2-4a) and with practically 50 lower specific on resistance (Figure 2-4 b) than similar devices in silicon.

Figure 2-4 a) Much shorter drift layer thickness in the SiC devices leads to the ultra low (theor.300 times) ON-state resistance. b) Area specific resistance of the SiC switch compared to the conventional and charge compensated Si MOSFETs shows 50 times improvement

A drawback of SiC is that the voltage of P-N junction is higher because of higher energy gap. This means that SiC diodes will have generally higher ON state voltages. The carrier mobility is also lower then in Si, consequently the inversion channel mobility in SiC MOSFET is much lower (<90 cm²/Vs for inversion electrons), which means that in lower voltage range the MOSFET devices will have lower gain and current carrying capability. Since the thin drift regions can not be utilized due to limited minimum achievable channel thickness, the higher ON-state resistance is expected.

The main advantage of the SiC MOSFET would be obvious only at medium to high voltage ranges 3...5 kV. Above these voltages the SiC IGBT could be better choice. Moreover, SiC oxides are not showing the same reliability as in Si MOSFETs. They have higher threshold voltage shifts, gate leakage, and oxide failures than comparably biased silicon MOSFET's, [47]. In [12] differences between the basic electrical properties of n-type versus p-type SiC MOS devices are discussed. One of the obvious differences between thermal oxidations of Si and SiC to form SiO<sub>2</sub> is the presence of carbon (C) in SiC. While most of the C in SiC converts to gaseous CO and CO<sub>2</sub> and evaporates from the oxide layer during thermal oxidation, remaining C resides near the SiC-SiO<sub>2</sub> interface. This has detrimental impact on SiO<sub>2</sub> electrical quality [1]. Consequently mach longer and higher temperature maintenance (annealing) is required to improve the SiC oxide quality.

#### **JFET Devices**

Alok and Baliga [18] presented a high voltage 6H-SiC JFET for 450V. A buried gate JFET transistor is reported in [29]. In [35] Konstantinov et. al. have presented buried gate JFET with blocking voltages up to 600-700. Though there are many reports about different possibilities to realize SiC JFET, the only device available today, which can be practically implemented in the power converter circuits is the SiC VJFET from SiCED GmbH (available as engineering samples) [14].

#### **Other Devices**

There are also reports about other emerging devices in development and their possible applications like:

SiC Metal Semiconductor Field Effect Transistor – MESFET: [44], [49]

Gate Turn OFF Switches – GTO: [17], [23] and

SiC Thyristors - [16], [48].

Japan researches have recently reported about laboratory samples of SiC bipolar transistors and IGBTs [Ohashi 2005]. There are also recent reports about bipolar transistors [24] with acceptable current gain [37]. Friedrichs [28] has recently reported that with heterojunction bipolar SiC transistor - Bipolar Injection Field Effect Transistor (BIFET) basically higher current gain is achievable. However some aspects should be studied, before the Bipolar Junction Transistors (BJT) can be reliably manufactured: 1) Identify the causes of limitations in minority carrier life time.2) How to create highly conductive and high quality p type wafers 3) How to mange the difficulties for paralleling of dies to get higher current [101].

| Technology   | Transistor<br>Type | Operating Voltage [V] | Frequency Limit [MHz] | Possible Temperature [°C] | Integration<br>Scale |

|--------------|--------------------|-----------------------|-----------------------|---------------------------|----------------------|

| SiC          | Normally ON        | > 1200                | 200                   | 500                       | Discrete             |

| GaN          | Normally ON        | > 15                  | 100                   | 300                       | Small                |

| Vacuum Trans | Normally ON        | > 500                 | 2000                  | 500                       | Discrete             |

| SOI CMOS     | Normally OFF       | 5V                    | 20                    | 300                       | Medium               |

Table 2-2 Summary of the currently known high temperature transistor technologies

Summarizing the given overview of the state of the art SiC semiconductor and emerging power devices based on it, we can state, that by means of SiC the application fields of currently known power semiconductors can be significantly widened. Of the many conceivable device benefits, the key one from the perspective of this study is the ability to meet system conditions with one device when silicon technology requires several. For example, the high voltage and switching speed of SiC diodes and transistors allow reducing the dynamic losses same way as Si Schottky diodes can do, however only for lower voltage levels. Based on above mentioned we will focus on those system aspects, that substantially reduce the size or complexity of the circuit in which SiC device is mounted. For example, by keeping all other boundary parameters constant, and by increasing the switching frequency of the high voltage power field effect transistors from 80 kHz up to 300-400 kHz, the volume and weight associated with passive devices can be drastically reduced. All this aspects will be discussed in details in next chapters.

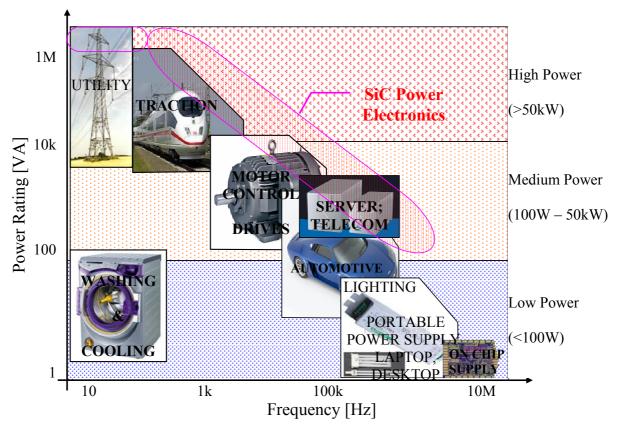

Figure 2-5 shows the step by step emergence of the SiC devices in different applications: Switch mode power supplies  $\rightarrow$  Industrial Drives and Motor Control  $\rightarrow$  Traction  $\rightarrow$  Utility and Megawatt applications

Figure 2-5 Related voltage, current and frequency ranges for different power devices and their application range extension by means of SiC semiconductor

# 2.2 Roadmap of power converters

Today only 12% of the world electricity is switched by power semiconductors. This will change... Stefhen Inc. 2002

Nowadays, Switch Mode Power Supplies (SMPS) have to fulfil many end-application requirements like industrial, automotive, telecom etc. Power converters, being the most material- and energy- demanding parts in electronic equipment, often define their size-weight, exploitation, reliability and cost factors. Due to different nature of application requirements, especially the nominal power level of an end-user, there is a set of commonly used converter topologies for different products. Usually, in power supplies dedicated for power levels from 700W and higher, the multi-switch double-ended topologies are chosen [57].

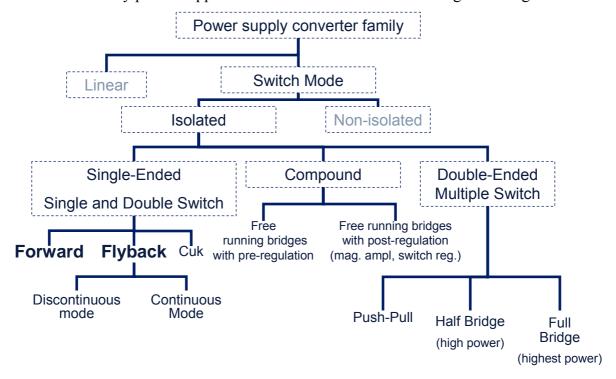

# 2.2.1 Classification of main topologies

General secondary power supplies tree is illustrated in the following chart: Figure 2-6

Figure 2-6 The secondary power supply converter tree

Assuming all components as well as the input power source ideal, two classes can be separated out from all possible converter topologies depicted in the Figure 2-6:- converters with finite energy accumulation (Buck Converter) and converters with infinite energy accumulation (Boost Converters) [86]. Designing and use of the power converters requires understanding of their main characteristics. The majority of the converter topologies are derived from 3 fundamental types: I- Buck, II -Boost and III- Inverting (Table 2-3). Though being a basic topology, the Inverting converter (Buck-Boost) is not fundamental, since its characteristics can be obtained with series connection of two previous fundamental converters. Basically these three topologies have the same components (Switch, Diode, Inductor, and Capacitor), but differently connected to the load side (Table 2-3). It is this "outer" side of the converter that classify the converters to the mentioned types.

Table 2-3 Fundamental topologies: Buck, Boost and Inverting converters

There are 3 different operation modes in that the power converter can operate:

- a) Continues Conduction Mode (CCM) operation with continues magnetic flux in inductive components

- b) Discontinues Conduction Mode (DCM) operation with discontinues magnetic flux in inductive components

- c) Critical conduction mode (BCM) boundary operation between two modes

Regarding the way how the energy is taken from source and provided to load, converters

can be classified as:

- a) Pulsed energy consumption from source and continues energy output to the load (I)

- b) Continues energy consumption from source and pulsed energy output to the load (II)

- c) Pulsed energy consumption from source and pulsed energy output to the load (III)

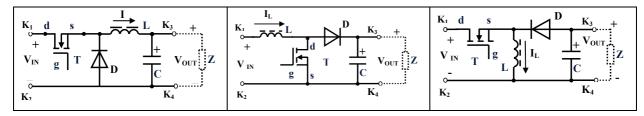

Further investigation of the converters in this thesis is based on two isolated "Forward" and "Flyback" converters, which can be derived from the fundamental converters [90]. Their basic characteristics and main relationships between input, output and regulation parameters are derived in [A1] and summarized in the Table 2-4. Due to isolation transformer the output voltage and current are recalculated to the primary side.

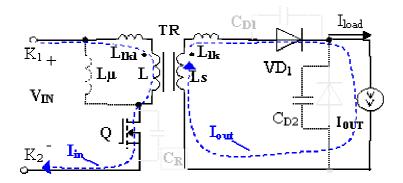

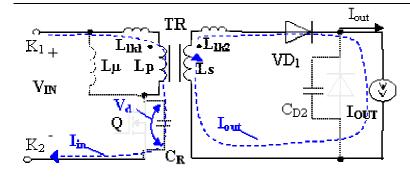

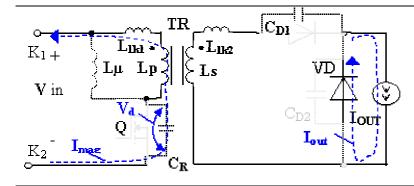

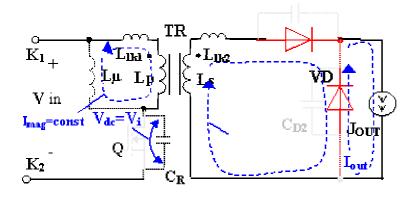

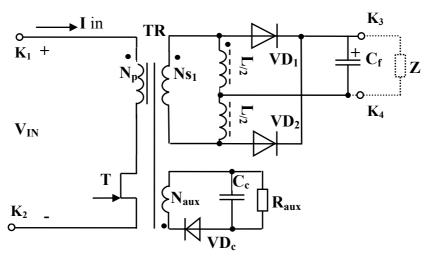

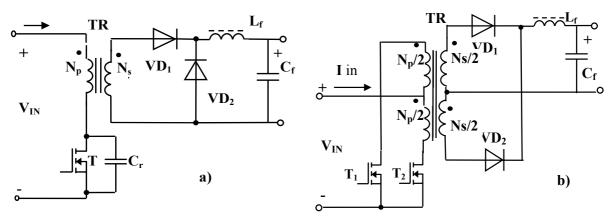

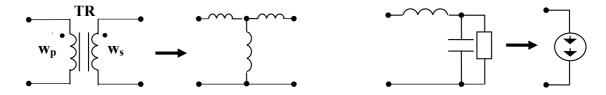

| Topology                       | $\begin{array}{c c} \hline  & \text{I in} \\ \hline  & \text{K1} \\ \hline  & \text{V in} \\ \hline  & \text{V} \\ \hline $ | $\begin{array}{c c} \hline  & \text{I in} \\ \hline  & \text{K1} + \\ \hline  & \text{Lp} \\ \hline  & \text{V in} \\ \hline  & \text{V} \\$ |  |

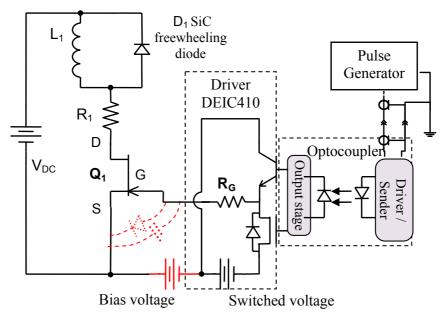

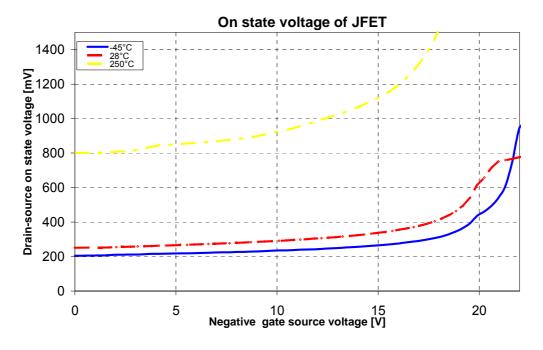

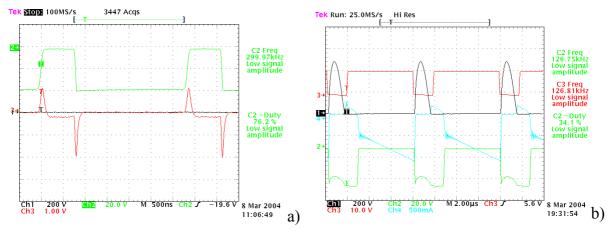

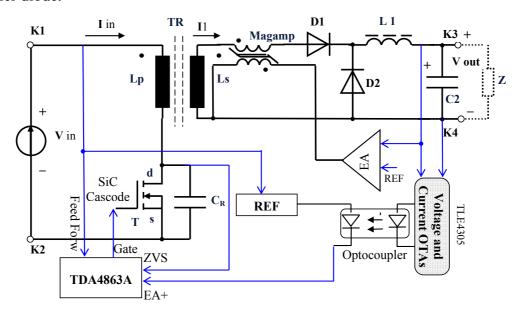

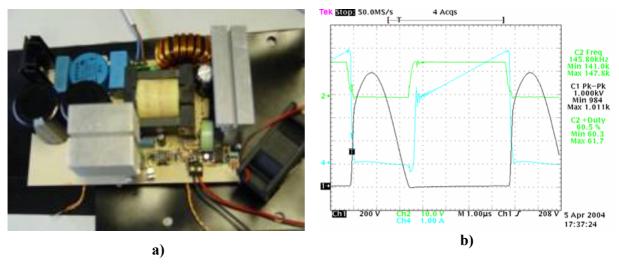

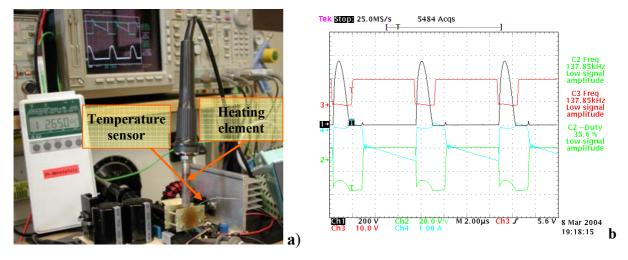

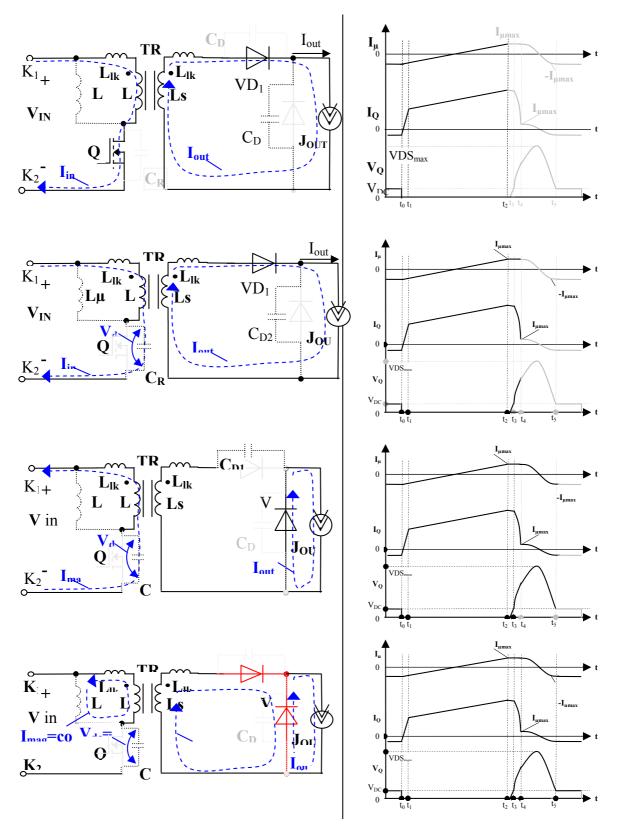

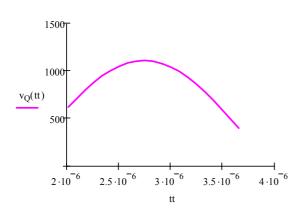

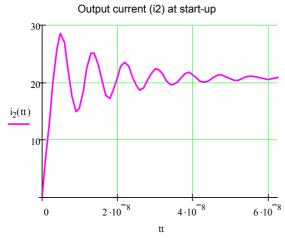

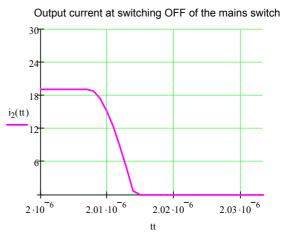

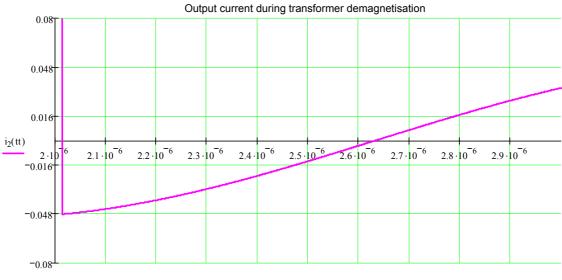

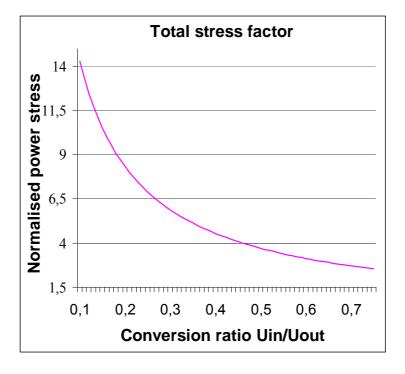

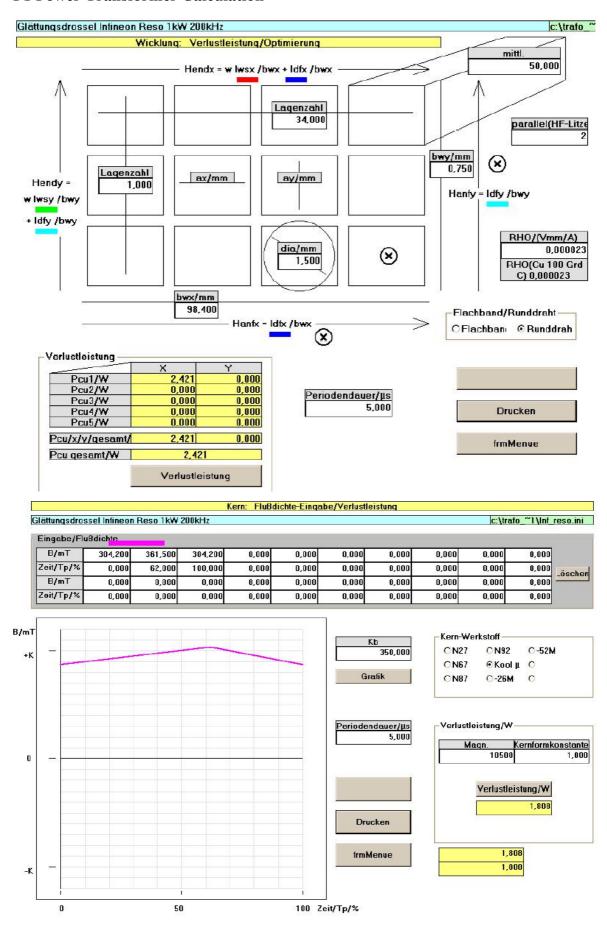

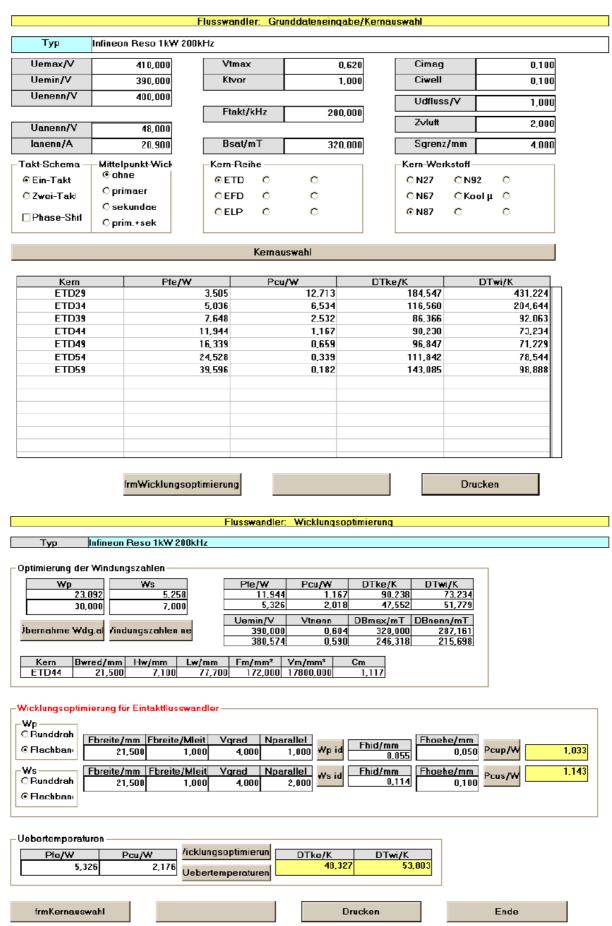

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|