# Schlussbericht des Teilvorhabens

Kompakte und hochintegrierte magnetische Bauelemente für den Betrieb bei höheren Frequenzen und Integrationskonzepte für schnelle Leistungshalbleiter

# Im Verbundvorhaben

FLIP: Optimierte Aufbau- und Verbindungstechnik für Photovoltaik-Wechselrichter

Teilvorhaben zum Themenfeld Leistungselektronik zur Energieeffizienz-Steigerung (LES) Teil 2: Elektronik für die Energie der Zukunft

Autoren des Berichts: Juliane Hinze, Dr.-Ing. Thiemo Kleeb, Christian Felgemacher

Förderkennzeichen: 16ES0129K

Projektlaufzeit: 01.09.2013 bis 30.11.2016

Das diesem Bericht zugrundeliegende Vorhaben wurde mit Mitteln des Bundesministeriums für Bildung und Forschung unter dem Förderkennzeichen ES1 LES2-42 gefördert. Die Verantwortung für den Inhalt dieser Veröffentlichung liegt beim Autor.

Zuwendungsempfänger: Universität Kassel

Kompetenzzentrum für dezentrale elektrische Energiever-

sorgungstechnik (KDEE) – Fachgebiet Elektrische

Energieversorgungssysteme (EVS)

Wilhelmshöher Allee 73

34121 Kassel

Ansprechpartner: Juliane Hinze

E-Mail: juliane.hinze@uni-kassel.de

Telefon: 0561-804-6305

Ansprechpartner: Prof. Dr.-Ing. habil. Peter Zacharias

E-Mail: peter.zacharias@uni-kassel.de

Telefon: 0561-804-6344

# Inhalt

| 1 | Kur        | zdars | tellung                                                                 | 1  |

|---|------------|-------|-------------------------------------------------------------------------|----|

|   | 1.1        | Auf   | gabenstellung und Ziele                                                 | 1  |

|   | 1.2        | Vor   | aussetzungen das Vorhabens                                              | 1  |

|   | 1.3        | Plar  | nung und Ablauf des Vorhabens                                           | 4  |

|   | 1.4        | Star  | nd der Wissenschaft und der Technik zum Antragszeitpunkt                | 5  |

|   | 1.5        | Ver   | netzung und Zusammenarbeit                                              | 6  |

| 2 | Ein        | geher | nde Darstellung                                                         | 7  |

|   | 2.1        | Übe   | erblick über die durchgeführten Arbeiten                                | 7  |

|   | 2.2        | Vor   | untersuchungen zu Anforderungen an die AVT                              | 7  |

|   | 2.2        | .1    | Einfluss des Gehäuses auf die Kommutierung und das thermische Verhalten | 8  |

|   | 2.2        | .2    | Parasitäre Induktivitäten im Kommutierungskreis                         | 9  |

|   | 2.2        | .3    | Benchmarking eingebetteter Module und SMD-Alternativen                  | 10 |

|   | 2.2<br>Tec |       | Thermische Bewertung der Modullösungen und Benchmarking mit gängigen    | 11 |

|   | 2.3        |       | gebettete Leistungshalbleiter                                           |    |

|   | 2.3        |       | Untersuchung eingebettetes OptiMOS-Modul                                |    |

|   | 2.3        |       | Untersuchung eingebettetes JFET-Modul                                   |    |

|   | 2.3        |       | Untersuchung eingebetteter JFET-Wechselrichter                          |    |

|   | 2.4        |       | gnetische Bauelemente                                                   |    |

|   | 2.4        | •     | Speicherdrosseln für hohe Schaltfrequenzen und Stromrippel              |    |

|   | 2.4        |       | Gleich-Gegentaktdrosseln für EMV Filter                                 |    |

|   | 2.4        |       | EMV Filter mit magnetisch integrierten Komponenten (für Demonstrator 1) |    |

|   | 2.4        |       | EMV Filter für Demonstrator 2                                           |    |

|   | 2.4        | .5    | Zusammenfassung                                                         |    |

|   | 2.5        |       | erlässigkeits-Untersuchung                                              |    |

|   | 2.5        |       | Modul-Charakterisierung                                                 |    |

|   | 2.5        |       | H3TRB Test                                                              |    |

|   | 2.5        | .3    | Thermal Shock Test                                                      |    |

|   | 2.5        | .4    | Passive Thermal Cycling Tests                                           |    |

|   | 2.5        |       | Power Cycling                                                           |    |

|   | 2.5        |       | Zusammenfassung                                                         |    |

| 3 |            |       | enfassung                                                               |    |

| 4 |            |       | tlichungen                                                              |    |

# 1 Kurzdarstellung

# 1.1 Aufgabenstellung und Ziele

Das Teilvorhaben des Fachgebiets "Elektrische Energieversorgungssysteme (EVS)" innerhalb des "Kompetenzzentrums für Dezentrale Elektrische Energieversorgungstechnik (KDEE)" hat einen Betrag zum Vorhaben "Optimierte Aufbau- und Verbindungstechnik für Photovoltaik-Wechselrichter (FLIP)" geleistet.

Ziel des Projektes "FLIP" war die Untersuchung, wie durch Einsatz schnellschaltender Halbleiterschalter, die Erhöhung der Taktfrequenzen auf mehrere 100 kHz und Senkung des Materialaufwands, sowie vereinfachter Strukturen und neuer Aufbautechniken, die eine vollautomatisierte Fertigung ermöglichen, die Kosten für Kleinwechselrichter speziell für PV-Anwendungen drastisch reduziert und gleichzeitig Zuverlässigkeit, Wirkungsgrad und Lebensdauer weiter verbessert werden können.

Das KDEE unterstützte dieses Vorhaben durch beratende Tätigkeiten in der Auslegungs- und Optimierungsphase, sowie bei der Ermittlung und Definition der Anforderungen an die AVT. Für die verschiedenen Demonstratoren mit eingebetteten Halbleitern wurden die Leiterplatten-Designs entworfen und im Anschluss wurden diese aufgebaut und untersucht. Des Weiteren wurden die eingebetteten Leistungshalbleiter auf ihre Lebensdauer untersucht und hochkompakte magnetische Filterelemente entwickelt, die für besonders für den Betrieb bei hohen Schaltfrequenzen geeignet sind.

# 1.2 Voraussetzungen das Vorhabens

Das Vorhaben wurde mit einem Konsortium durchgeführt, das die Wertschöpfungskette von der Leistungshalbleiterherstellung über die Leiterplattenherstellung bis zur Wechselrichterherstellung darstellt und von wissenschaftlicher Seite insbesondere im Gebiet der Aufbau- und Verbindungstechnik sowie Leistungshalbleitern und magnetischer Bauelemente aufgestellt ist.

#### **Universität Kassel / KDEE**

Das KDEE (Kompetenzzentrum für Dezentrale elektrische Energieversorgungstechnik) der Universität Kassel befasst sich unter der Leitung von Prof. Dr.-Ing. habil. Peter Zacharias mit geräteorientierter Energiesystemtechnik für die Nutzung erneuerbarer Energien mit besonderem Schwerpunkt bei der Stromrichtertechnik in Hybridsystemen, im Verteilnetz und bei dezentraler Energiewandlung sowie in mobilen Energieversorgungssystemen. Weitere Kompetenzen bestehen sowohl in der Charakterisierung und Applikation von neuen Leistungshalbleiter wie SiC und GaN, als auch in der Entwicklung und Vermessung von hochintegrierten und effizienten magnetischen Filter- und Übertragungselementen. Das KDEE verfügt zurzeit über 10 wissenschaftliche Angestellte und mehrere vollausgerüstete Labore zur Entwicklung und Erprobung von leistungselektronischen Schaltungen. Weiterhin verfügt die Universität Kassel über zahlreiche weitere Fachgebiete und Kompetenzen, die in das Vorhaben mit einbezogen wurden.

Die Aufgabe des KDEEs im Konsortium war die Unterstützung bei der Ermittlung der Definitionen und Anforderungen, sowie bei der Auslegungs- und Optimierungsphase. Das Design für alle drei

Demonstratoren mit eingebetteten Halbleiterschaltern wurde vom KDEE entworfen. Nach Fertigstellung durch die Projektpartner war es die Aufgabe des KDEE den Aufbau, die Inbetriebnahme und die Vermessung der Demonstratoren durchzuführen, sowie die angewendeten Aufbau- und Verbindungstechnik mit den eingebetteten Leistungshalbleiterschaltern zu bewerten. Die angewandte Technologie wurde mit dem Stand der Technik, d.h. mit diskreten Packages verglichen und hinsichtlich ihrer Lebensdauer untersucht. Eine weitere Aufgabe des KDEE bestand darin neue integrierte und hochkompakte magnetische Filterelemente zu entwickeln, welche für den hochfrequenten Einsatz in den Demonstratoren geeignet sind.

#### **Ruwel International GmbH**

RUWEL ist der traditionsreichste europäische Leiterplattenhersteller, der 1956 als erster die seriengefertigte "gedruckte Schaltung" auf dem Markt einführte, und ist heute einer der bedeutendsten Hersteller von Leiterplatten in Europa. RUWEL hat derzeit 225 Mitarbeiter am Standort Geldern und erzielte im Geschäftsjahr 2011 einen Umsatz von 54 Millionen Euro. Wir unterstützen unsere Kunden in optimaler Weise, ihren Beschaffungsaufwand effizient zu gestalten. RUWEL produziert Leiterplatten für nahezu alle Technologiebereiche und das in allen Stückzahlen – vom Entwicklungsmuster bis zur Großserie. Zu den Kunden gehören die großen, weltweit agierenden Elektronikkonzerne sowie mittelständische Unternehmen. RUWEL ist bei Leiterplatten für die Solartechnik in Europa Marktführer und nimmt eine führende Rolle bei Leiterplatten in den Bereichen regenerative Energietechnik, Industrie-, Medizin- sowie der Automobilindustrie ein. Ein prozessorientiertes Qualitätsmanagementsystem ist eine wesentliche Voraussetzung für einen hohen Grad an Kundenzufriedenheit. RUWEL arbeitet in vielen Projekten und engagiert sich bei der Verbandsarbeit (ZVEI, FED) zu den Themen Hochstrom, Entwärmung, RFID, Traceability, Zuverlässigkeit von Bauteilen bei bleifreiem Löten sowie neuen Basismaterialien. RUWEL verpflichtet sich einem nachhaltigen Umweltschutz durch einen hohen Grad an Innovationen, einer Umweltpolitik für die Zukunft sowie in der nachhaltigen Nutzung von Ressourcen, vor allem von Energie (Zertifizierung nach 50001) und Rohstoffen.

Die Aufgabe von Ruwel im Projektkonsortium war die Ermittlung, Erprobung und Festlegung der benötigten Basismaterialien, Fertigungsverfahren und –Techniken, mit den die festgelegten Anforderungen bzw. Spezifikationen erfüllten werden, die im Projekt gemeinsam ermittelt und festgelegt worden sind. Im Weiteren stand die Ermittlung der optimierten Fertigung zur serienmäßigen Herstellung einer "Embedding"-Schaltung bzw. –Moduls zum Aufgabenbereich. Zudem wurden die Moduls bzw. Schaltung über Temperaturwechsel-Tests und Temperaturlagerungs-Tests auf ihre Zuverlässigkeit geprüft.

### **SMA Solar Technology AG**

Die SMA Solar Technology AG ist mit einem Umsatz von rund 1 Mrd. Euro in 2015 Weltmarktführer bei Photovoltaik-Wechselrichtern, einer zentralen Komponente jeder Solarstromanlage. Sie hat ihren Hauptsitz in Niestetal bei Kassel und ist auf vier Kontinenten in 21 Ländern mit ausländischen Tochtergesellschaften vertreten. Die Unternehmensgruppe beschäftigt mehr als 3.500 Mitarbeiter und produziert ein breites Spektrum von Wechselrichtertypen, das geeignete Wechselrichter für jeden eingesetzten Photovoltaik-Modultyp und alle Leistungsgrößen von Photovoltaik-Anlagen bietet. Das Produktspektrum beinhaltet sowohl Wechselrichter für netzgekoppelte Photovoltaik-Anlagen als auch für Inselsysteme. Hierzu gehören insbesondere auch innovative Systemlösungen zur

Netzintegration der Photovoltaik einschließlich Batteriespeichern und Energiemanagementsystemen. Die SMA Solar Technology AG verfügt als Technologie- und Innovationsführer über rund drei Jahrzehnte Erfahrung auf dem Gebiet der Wechselrichter-Entwicklung sowie ihrer systemtechnischen Einbindung in Energieversorgungssysteme. Neben der eigentlichen Produktentwicklung neuer Wechselrichtersysteme befassen sich die z.Z. rund 500 Wissenschaftler und Ingenieure der verschiedenen Entwicklungsabteilungen bei SMA im Rahmen zahlreicher Kooperationsprojekte auch mit vielfältigen übergeordneten Fragestellungen, die sich derzeit vor allem auf das Themengebiet Netzintegration und Umbau der Stromversorgung konzentrieren. In zahlreichen Forschungsvorhaben und Entwicklungsprojekten hat SMA vielfältige Innovationen erarbeitet und stets in erfolgreiche Produkte umgesetzt.

Die Aufgabe von SMA im Konsortium betraf insbesondere die Bewertungen der Lösungen im Hinblick auf das Wechselrichtergesamtsystem und dessen Kostenreduktion. Hierbei wurden durch den Aufbau von Demonstratoren die Auswirkungen unterschiedlicher Umsetzungskonzepte in der Aufbau- und Verbindungstechnik, sowie der Fertigungstechnik hinsichtlich des Gesamtsystems untersucht und optimiert. Die Tätigkeiten beinhalteten außerdem vertiefende Untersuchungen zu Bauteilen und Funktionsgruppen, die durch die hohen Taktfrequenzen signifikant beeinflusst wurden. Hierbei handelte es sich um die Speicherinduktivitäten, das EMV-Filter, die Sensorik, das Regelungskonzept, das Boardnetzkonzept inkl. Leistungshalbleitertreiberversorgung sowie die Kondensatorauswahl.

#### **TU-Berlin**

Der Forschungsschwerpunkt "Technologien der Mikroperipherik" der Technischen Universität Berlin erforscht und entwickelt Methoden und Technologien der Aufbau- und Verbindungstechnik von mikroelektronischen und mikrosystem-technischen Bauteilen. Schwerpunkt sind die Integrationsund Verbindungstechniken auf der Chip- und Leiterplatten-Ebene (Electronic Packaging), einschließlich der Prozesse, Technologien, Testmethoden und Zuverlässigkeitsprüfungen für künftige Systemintegration. Von besonderer Bedeutung ist dabei die enge Kooperation mit dem Fraunhofer IZM. Die apparative Ausstattung beinhaltet unter anderem Leiterplatten-Laminiertechnik, Metallabscheidung und Laser-Strukturiertechnik in Kombination mit umfangreicher Montagetechnik. Projektrelevante Forschungsschwerpunkte, die in den letzten Jahren bei der TUB bearbeitet wurden und werden, liegen in den Bereichen hochintegrierter Substrate, Einbettung von Bauteilen in organische Substratmaterialien und Packaging für Medizintechnik und Automotiv-Anwendungen.

Die TU bringt Ihre in früheren Projekten zur Einbett-Technologie erworbenen Erkenntnisse und Expertise in die Konzeptionierung und Umsetzung von Embedded-Modulen ein. Insbesondere der Projektpartner RUWEL International, für den die Technologie neu ist, stand während der gesamten Projektlaufzeit in engem Kontakt mit der TU Berlin. Hinsichtlich der Herstellung von Modulen ist die Bestückung der Leiterplatten-Innenlage ausschließlich an der TU Berlin durchgeführt worden, da die notwendigen Maschinen (hochpräzise Chip-Platzierung, Positionsbestimmung der Chips x-y-z mit Bezug auf Registriermarken) innerhalb des Konsortiums nur an der TU Berlin zur Verfügung stehen. In einer Reihe von Prozess-Trainings wurden zunächst MOSFET-Chips mittels leitfähigen Klebers mit den Innenlagen verbunden. Für die Demonstratoren wurden SiC Chips mittels Silber-Nanonsintern verbunden. An der TU Berlin wurden aktive Leistungszyklen sowie eine Reihe von detaillierten Analysen an aufgetretenen Ausfällen durchgeführt.

### **Infineon Technologies AG**

Mit weltweit rund 26.000 Mitarbeiterinnen und Mitarbeitern erzielte Infineon im Geschäftsjahr 2011 (Ende September) einen Umsatz von 4 Milliarden Euro. Infineon Technologies AG ist als Hersteller von Halbleiterbauelementen weltweit die Nummer 1 im Segment der Leistungselektronik. Infineon ist weltweiter Vorreiter bei SiC-Bauelementen (thinQ!™ in 2001) und Si-

Kompensationsbauelementen (CoolMOS™). Infineon hat in Deutschland Aktivitäten insbesondere am Standort München (Chipentwicklung), Dresden (zukünftig weltweit führend bei der Fertigung von Leistungshalbleitern auf 300 mm Wafern), Warstein (Kompetenzzentrum für IGBT Module mit Entwicklung/Produktion/Applikation) und Regensburg (Sensorentwicklung, Wafer Level Packaging, Chip Embedding Technologien sowie Forschung und Entwicklung für alle neuen Gehäuse weltweit von Infineon einschließlich Kompetenzzentrum für heterogene Integration). Als assoziierter Partner ist Infineon im Projekt hauptsächlich am Austausch von technischen Erkenntnissen beteiligt. Im Laufe des Projekts stellte Infineon Muster von Bauelementen zur Verfügung, um das Projekt zu unterstützen.

# 1.3 Planung und Ablauf des Vorhabens

Das Gesamtvorhaben wurde in sechs thematische Arbeitspakte unterteil, die jeweils wiederum in zahlreiche Unterpakete gesplittet wurden. Das Teilvorhaben "Kompakte und hochintegrierte magnetische Bauelemente für den Betrieb bei höheren Frequenzen und Integrationskonzepte für schnelle Leistungshalbleiter" hatte dabei Anteile an den Arbeitspaketen AP1, AP2, AP3, AP5 und AP6, wobei der Schwerpunkt der Tätigkeiten auf die Arbeitspakete AP2 und AP3 entfiel. Darüber hinaus wurde mehr Aufwand in die Arbeitspaket AP5 und AP6 gelegt als ursprünglich geplant.

In der folgenden Tabelle sind die (Unter)-Arbeitspakete aufgeführt, auf die sich die Tätigkeiten des Teilvorhabens erststrecken.

| AP# | Titel des Arbeitspaketes und Kurz-Beschreibung der Tätigkeiten                       |

|-----|--------------------------------------------------------------------------------------|

| 1   | Konzeptphase:                                                                        |

|     | Ermittlung Anforderung an die Leistungshalbleiter, Voruntersuchungen zur Aufbau- und |

|     | Verbindungstechnik, Topologie-Recherche und Bewertung, sowie Auswahl der Technologie |

|     | und Topologie                                                                        |

| 2.1 | Bewertung von Aufbaukonzepten                                                        |

| 2.4 | Auslegung, Konstruktion und Aufbau                                                   |

| 2.5 | Elektrische Messungen                                                                |

| 2.6 | Zuverlässigkeitsmessungen                                                            |

| 3   | Magnetische Elemente                                                                 |

|     | Bewerten von Aufbautechniken und Materialien, Entwicklung neuer Integrationskonzepte |

|     | inkl. thermischer und elektrischer Modellierung, sowie Auslegung und Aufbau für die  |

|     | Demonstratoren und Vergleich mit anderen Systemen                                    |

| 4.6 | Studien und Konzepte zur Wärmeverteilung und Wärmeabfuhr                             |

| 4.7 | Anordnung und Montage                                                                |

| 5.1 | Integrationskonzept                                                                  |

| 5.2 | Endgültige Auslegung des ersten Demonstrators                                        |

| 5.4 | Bewertung der Ergebnisse und Erarbeitung von Verbesserungsmöglichkeiten              |

| 5.5 | Auslegung des zweiten Demonstrators                                                  |

| 6.1 | Elektrische Tests                                                                    |

| 6.3 | Zyklentests                                                                          |

| 6.4 | Zuverlässigkeits- und Lebensdauerabschätzung                                         |

Tabelle 1: Arbeitspakete des Teilvorhabens

Der ursprünglich geplante zeitliche Ablauf des Gesamtvorhabens ist in Tabelle 2 verdeutlich. Der Meilenstein 2 musste aufgrund von leichten Verzögerungen bei der Fertigung des ersten Prototyps verschoben werden. Hierdurch und durch zusätzliche Fertigungszyklen, die zur Sicherung der Prozessstabilität nötig waren, kam es zu weiteren Verzögerungen für die Bereitstellung der Module für den ersten und zweiten Demonstrator.

Um dennoch die Projektziele zu erreichen, wurde im Rahmen einer Sitzung des Verbunds der Arbeitsund Meilensteinplan angepasst und das Projekt um drei Monate bis zum 30.11.2016 kostenneutral verlängert. Die Anpassung des Zeitplanes ist in Tabelle 3 dargestellt.

|     |    | 1. Jahr |    |    |    | 2. Jahr |    |    | 3. Jahr |    |    |    |

|-----|----|---------|----|----|----|---------|----|----|---------|----|----|----|

|     | Q1 | Q2      | Q3 | Q4 | Q1 | Q2      | Q3 | Q4 | Q1      | Q2 | Q3 | Q4 |

| AP1 |    | M1      |    |    |    |         |    |    |         |    |    |    |

| AP2 |    |         |    | M2 |    | M3      |    |    |         | M5 |    |    |

| AP3 |    |         |    | M2 |    | М3      |    |    |         | M5 |    |    |

| AP4 |    |         |    | M2 |    | M3      |    |    |         | M5 |    |    |

| AP5 |    |         |    |    |    |         |    |    |         | M5 |    |    |

| AP6 |    |         |    |    |    |         |    | M4 |         |    |    | M6 |

Tabelle 2: Geplanter zeitlicher Verlauf und Meilensteine des Gesamtvorhabens

|     | 1. Jahr |    |    |    | 2. Jahr |    |    | 3. Jahr |    |    | 4.<br>Jahr |    |    |

|-----|---------|----|----|----|---------|----|----|---------|----|----|------------|----|----|

|     | Q1      | Q2 | Q3 | Q4 | Q1      | Q2 | Q3 | Q4      | Q1 | Q2 | Q3         | Q4 | Q1 |

| AP1 |         | M1 |    |    |         |    |    |         |    |    |            |    |    |

| AP2 |         |    |    |    |         |    | M2 |         |    |    | M3         |    | M5 |

| AP3 |         |    |    | M2 |         | М3 |    |         |    |    |            |    | M5 |

| AP4 |         |    |    | M2 |         | М3 |    |         |    |    |            |    | M5 |

| AP5 |         |    |    |    |         |    |    |         |    |    |            |    | M5 |

| AP6 |         |    |    |    |         |    |    | (M4)    |    |    | M4         |    | M6 |

Tabelle 3: Angepasster zeitlicher Verlauf und Meilensteine des Gesamtvorhabens

Da sich die Projekte FLIP und IFASS von ihren Projektzielen und ihrem Fokus in verschiedene Richtungen entwickelt haben, so dass keine Gemeinsamkeiten zwischen den Projekten mehr vorhanden waren, wurden die regelmäßigen Treffen des Konsortiums nach Absprache mit dem Projektträger ab 2016 eingestellt.

# 1.4 Stand der Wissenschaft und der Technik zum Antragszeitpunkt

Neue Leistungshalbleiter basierend auf Silizium-Carbid (SiC) und Gallium-Nitrid (GaN) besitzen sehr schnelles Schaltvermögen. Gängige Leistungsmodule und diskrete Gehäuse für diese Halbleiter verursachen jedoch in der Regel parasitäre Induktivitäten des Kommutierungskreises von mehr als 30nH. Dies begrenzt die maximalen Stromsteilheit di/dt aufgrund zu großer Überspannungen, so dass das volle Potenzial der Schalter nicht genutzt werden kann. Daher wurden im Rahmen des Projektes FLIP alternative Aufbau- und Verbindungstechniken (AVT) untersucht mit Fokus auf die Einbettung und deren Gehäusetechnologie.

Die magnetischen Bauelemente in leistungselektronischen Wandlern haben einen signifikanten Anteil an Volumen, Kosten und Verlusten. Um diese zu reduzieren, kann zum einen die Taktfrequenz erhöht werden und zum anderen neue Integrationsverfahren entwickelt werden. Im Rahmen des Projektes FLIP wird hier angesetzt und Filter- und Speicherelemente für hohe Taktfrequenzen entworfen, sowie neue strukturelle und funktionelle Integrationsverfahren entwickelt und getestet.

Die AVT eines PV-Wechselrichter-Seriengerätes besteht in der Regel aus drei wesentlichen Gruppen: Aktive Leistungshalbleiter, passive Elemente und der Elektronik. Diese sind oftmals auf mehreren Leiterplatten verteilt, wodurch der Aufbau aus vielfältigen Montageschritten besteht. Durch neue AVT, wie die Erhöhung der Integrationsdichte durch das Einbetten von Leistungshalbleitern, die Verwendung von integrierten magnetischen Bauelementen und die Reduzierung von Montageschritten durch reine SMT Technik, kann eine Miniaturisierung und Kostensenkung erreicht werden.

Die beteiligten Projektpartner – insbesondere die Industriepartner – verfügten bereits über vielfältige Schutzrechte bezüglich ihrer jeweiligen Produkte. Es waren keine bestehenden Schutzrechte Dritter bekannt, die der Umsetzung des geschilderten Lösungsansatzes entgegengestanden oder sich speziell auf den generellen Weg des Lösungsansatzes bezogen hätten. Die Universität Kassel/KDEE selbst besaß keine Schutzrechte mit direkter Relevanz für die geplanten Arbeiten.

# 1.5 Vernetzung und Zusammenarbeit

Das Projekt FLIP durchläuft die Wertschöpfungskette vom Leistungshalbleiter über dessen Einbettung und Herstellung der eingebetteten Module und Leiterplatten, hin zu deren elektrischen Charakterisierung und schließlich zur Systemintegration in PV-Wechselrichtern. Hierbei ergab sich eine enge Zusammenarbeit zwischen allen Partnern. Die TU Berlin bereitete die Halbleiterschalter für das einbetten vor und übernahm deren Platzierung. Die Firma Ruwel International GmbH stellte die hierfür benötigten Leiterplatten her und übernahm das Einbetten und die Herstellung der Module. Parallel hierzu wurden ebenfalls eingebettete Module von der TU Berlin hergestellt und zur Verfügung gestellt. Die Universität Kassel stellte das Design der Module, übernahm die elektrischen Tests und baute und untersuchte die Demonstratoren mit den eingebetteten Halbleiterschaltern. Die Firma SMA Technology AG untersuchte die Systemintegration für PV-Wechselrichter und neue AVT Ansätze wie die reine SMT Herstellung. Zur Optimierung und Entwicklung neuer magnetischer Bauelemente arbeitete die Universität Kassel eng mit der Firma SMA Technology AG zusammen. Die Firma Infineon Technologies AG war im Konsortium ein assoziierter Partner, welcher das Projekt bei der Wahl der Leistungshalbleiter unterstütze und diese zur Verfügung stellte.

# 2 Eingehende Darstellung

# 2.1 Überblick über die durchgeführten Arbeiten

Die an der Universität Kassel durchgeführten Arbeiten lassen sich grob vier Schwerpunkten zuordnen:

- 1. In der Konzeptphase wurden die Projektpartner bei der Findung der Anforderungen und Zielspezifikationen für die Demonstratoren unterstützt

- 2. Für die Untersuchung der neuen Aufbau- und Verbindungstechnik wurde das Design für die Module und Demonstratoren mit eingebetteten Halbleitern entworfen. Diese wurden nach der Fertigung aufgebaut, in Betrieb genommen und charakterisiert. Im Anschluss wurde die elektrische und thermische Performance der Demonstratoren getestet und mit dem Stand der Technik verglichen.

- 3. Neue magnetische Bauelemente wurden entwickelt und für den Betrieb bei hohen Frequenzen ausgelegt. Hierzu wurden neue Integrationskonzepte der Filterbauelemente untersucht.

- 4. Die gesamten im Projekt vorgenommenen Lebensdauertests wurden geplant und koordiniert. Neben den am KDEE durchgeführten Lebensdauertests, wurden auch alle elektrischen Charakterisierungen der Samples, sowie deren Kontroll-Tests vorgenommen.

# 2.2 Voruntersuchungen zu Anforderungen an die AVT

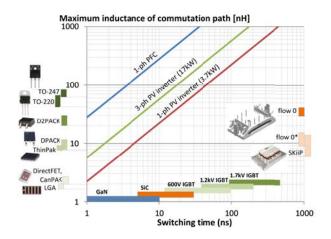

Um Anforderungen an die AVT definieren zu können, wurden in einem ersten Schritt Berechnungen durchgeführt, um die maximale Induktivität des Kommutierungskreises als Funktion der gezielten Schaltzeiten zu bestimmten. In dieser Berechnung werden sowohl die maximale Zwischenkreisspannung, wie auch die Spannungsklasse der Leistungshalbleiter berücksichtigt. Das Ergebnis ist in Abbildung 1 zu sehen. Als Referenz sind auf der y-Achse die parasitären Induktivitäten der typischen Kommutierungskreise mit bestehenden Gehäusen und Leistungsmodulen dargestellt. Wie in Kapitel 1.4 bereits beschrieben, wird eine AVT benötigt, so dass die Fähigkeiten der schnellen Leistungsschalter vollständig ausgenutzt werden können. Um dies zu erreichen sind Werte der Kommutierungsinduktivität von kleiner als 10nH erforderlich<sup>1</sup>.

Abbildung 1: Maximale Induktivität des Kommutierungskreises als Funktion der Schaltzeiten für verschiedene Applikationen

<sup>&</sup>lt;sup>1</sup>CIPS 2014: "Power Semiconductor Packaging in PV Inverters up to 30 kW power, a difficult choice", Juliane Hinze

### 2.2.1 Einfluss des Gehäuses auf die Kommutierung und das thermische Verhalten

Um den Einfluss des gewählten Halbleiter-Gehäuses zu untersuchen, wurde in einem zweiten Schritt das elektrische Verhalten eines CoolMOS C7 650V Halbleiterchips mit  $65m\Omega$  R<sub>DS(on)</sub> untersucht, der in verschiedenen SMD und THT Packages eingebaut wurde. Hierbei wurde auch der Einfluss eines Kelvin-Source-Pins mit betrachtet. Im Anschluss wurden das Verhalten und die Anwendbarkeit des Leistungshalbleiters mit den verschiedenen Gehäusen bei hohen Taktfrequenzen untersucht.

Für die Untersuchungen wurden vier Platinen für die vier verschiedenen Gehäuse ThinPak und TO-247-4 (beide mit Kelvin-Source-Pin), sowie D²Pak und TO-247 entworfen. Hierbei wurde der Fokus auf einen niederinduktiven Kommutierungskreis und ein möglichst identisches Design gelegt. Insgesamt wurden zwei verschiedene Betrachtungen angestellt. Zum einen wurden alle mit der gleichen Treiber-Konfiguration angesteuert und alle thermisch gleich angebunden (mit ThinPak als Referenz) und zum anderen erhielt jedes Package die optimale Treiber-Konfiguration und die bestmögliche thermische Anbindung. Für die elektrische Charakterisierung wurde eine Doppelpuls-Messung bei einem Arbeitspunkt von 350V und 10A durchgeführt. Für die thermische Betrachtung und die Ermittlung der Verluste wurde der Aufbau als Hochsetzsteller betrieben, der Wirkungsgrad gemessen und die Gehäusetemperatur kontrolliert. Hierbei lagen die Ausgangsspannung bei 350V und die Ausgangsleistung bei 2,3kW.

| Package  | Einschaltmoment | Ausschalten  |                      |         |  |  |

|----------|-----------------|--------------|----------------------|---------|--|--|

|          | du/dt [V/ns]    | du/dt [V/ns] | U <sub>max</sub> [V] | f [MHz] |  |  |

| ThinPak  | 63,5            | 25,9         | 402                  | 22,2    |  |  |

| TO-247-4 | 62,9            | 26,7         | 398                  | 22,4    |  |  |

| D²Pak    | 31,5            | 26,7         | 408                  | 21,6    |  |  |

| TO-247   | 31,5            | 27           | 402                  | 21,2    |  |  |

Tabelle 4: Elektrische Charakterisierung im Doppelpulsversuch bei gleicher Treiber-Konfiguration

Es stellte sich heraus, dass die optimale Treiber-Konfiguration für die verschiedenen Gehäuse unterschiedlich ist, obwohl überall der gleiche Halbleiterchip verbaut wurde. Wird für einen direkten Vergleich eine feste Treiber-Konfiguration für alle vier Varianten verwendet, so zeigt sich, dass die Gehäuse mit Kelvin-Source-Pin doppelt so schnell einschalten als die Gehäuse ohne diesen Pin. Zudem ist deren Schalterüberspannung tendenziell etwas geringer. Auf die Schaltflanke im Ausschaltmoment und auch die Oszillationsfrequenz scheint das Gehäuse keinen Einfluss zu haben. Wird für jedes Gehäuse die jeweils optimale Treiber-Konfiguration verwendet, so sind die Unterschiede nicht mehr so deutlich, jedoch ist die Tendenz weiterhin gut zu erkennen.

Für die Hochsetzsteller-Messung wurde die jeweils optimierte Treiber-Konfiguration verwendet. Die Vermessung findet für Taktfrequenzen von 200kHz, 250kHz und 300kHz statt. Hierbei sind alle Gehäuse thermisch gleich angebunden und die Temperaturen der Gehäuseoberfläche wurden mit einer Infrarot-Thermokamera kontrolliert und aufgenommen. Die Aufbauvariante mit D²Pak musste für diesen Test aufgrund eines technischen Defektes rausgenommen werden. In Tabelle 5 sind alle Werte der Messungen zusammengefasst. Für die Messungen musste ab dem Betrieb bei 250kHz ein anderer Treiber verwendet werden, dadurch ergab sich eine neue optimierte Treiber-Konfiguration der TO-247-4 Variante, welche mit '\*' gekennzeichnete wurde.

|                           | ThinPak | TO-247-4 | TO-247 | ThinPak           | TO-247-4 | TO-247-4* | TO-247 | TO-247-4         | TO-247 |

|---------------------------|---------|----------|--------|-------------------|----------|-----------|--------|------------------|--------|

|                           | 200kHz  |          |        | 250kHz            |          |           |        | 300kHz           |        |

| η [%]                     | 98,095  | 98,535   | 98,236 | 97,855            | 97,953   | 97,988    | 98,010 | 97,820           | 97,741 |

| T <sub>Package</sub> [°C] | 111     | 94       | 97     | 130               | 128      | 109       | 109    | 128              | 126    |

| P <sub>v</sub> [W]        | 18,0    | 13,9     | 16,8   | 20,3              | 19,3     | 19,1      | 18,8   | 20,7             | 21,4   |

| Messzeit                  | 50min   | 25min    | 55min  | Abbruch!<br>20min | 45min    | 65min     | 65min  | Abbruch!<br>5min | 55min  |

Tabelle 5: Zusammenfassung der Wirkungsgradmessung des Hochsetzstellers (jeweils optimierte Treiber-Konfiguration und thermisch gleiche Anbindung)

Es zeigt sich, dass alle Varianten bei 200kHz betrieben werden können und dabei einen moderaten Wirkungsgrad besitzen. Ab 250kHz kann der ThinPak nicht mehr betrieben werden, da die Verlustwärme durch die Leiterplatte, trotz Einsatz von Thermal-Vias, nicht gut genug abgeführt werden kann. Ausschließlich die Variante TO-247 konnte bei 300kHz betrieben werden - bei einem Wirkungsgrad von 97,7%. Da die Gehäuse von TO-247 und TO-247-4 grundsätzlich gleich sind und diese somit auch die Temperatur gleich gut abführen können, ist darauf zu schließen, dass die Halbleiterchips unterschiedliche Verluste produzieren. Bereits bei der Treiber-Konfiguration und dem thermischen Abgleich haben sich Unterschiede zwischen den beiden Varianten gezeigt.

Um prüfen zu können bis zu welcher Taktfrequenz der TO-247 mit diesem Schalter geeignet ist, wurde seine thermische Anbindung optimiert und die Messungen wiederholt. Die Ergebnisse sind in Tabelle 6 aufgeführt. Es zeigte sich, dass bereits mit den gebräuchlichen THT Gehäusen Taktfrequenzen mit 400kHz erreicht werden können. Allerdings ist hierbei mit Wirkungsgradverringerungen von ca. 2-3% zu rechnen. Mit den gebräuchlichen Leistungshalbleitern sind die Schaltverluste und somit die Wärme das begrenzende Kriterium.

|                                | 250kHz | 300kHz | 350kHz | 400kHz |

|--------------------------------|--------|--------|--------|--------|

| η [%]                          | 98,03  | 97,84  | 97,58  | 97,42  |

| T <sub>Package</sub> [°C]      | 80     | 87     | 99     | 103    |

| P <sub>Verluste, ges</sub> [W] | 18,5   | 20,5   | 23,0   | 24,7   |

Tabelle 6: Gehäuse TO-247 mit optimaler thermischer Anbindung

Ein Ergebnis dieser Untersuchung war, dass die Halbleiter in den TO-Gehäusen in diesem Arbeitspunkt problemlos mit 400kHz betrieben werden konnten. Die SMD Variante konnte mit bis zu 200kHz betrieben werden. Das Abbruchkriterium lag hier bei der Temperatur. Zudem verschlechterte sich der Wirkungsgrad im einstelligen Prozentbereich. Mit Halbleitern die weniger Schaltverluste produzieren, wäre ein hochfrequentes Takten im Bereich von mehreren 100 kHz somit problemlos möglich.

# 2.2.2 Parasitäre Induktivitäten im Kommutierungskreis

Die Verteilung der parasitären Induktivitäten im Kommutierungskreis wurde durch den Aufbau einer Schaltzelle auf einer kleinen Platine untersucht. Hierbei wurde der Fokus auf die Eigeninduktivitäten der Bauteile und die Induktivitäten der Leiterbahnen zwischen den Bauteilen gelegt. Für die Untersuchung der Bauteile und der Leiterbahnwege zwischen ihnen wurden diese im ersten Schritt mit einem Impedanzmessgerät vermessen. So konnten die Kleinsignal-Serienersatzschaltbilder der einzelnen Komponenten bestimmt werden. In einem zweiten Schritt wurde das elektrische Verhalten am Schalter über einen Doppelpulsversuch und bei Variation der Bauteile untersucht. Um ggf.

spätere Messungen zu reduzieren, wurde in einem dritten Schritt versucht den Aufbau in dem Simulationsprogramm Simplorer zu rekonstruieren und die Messergebnisse zu reproduzieren. Zusätzlich wurde noch im Anschluss die Leiterplattengeometrie in dem Programm Q3D aufgebaut, um so die parasitären Leiterbahn-Induktivitäten ebenfalls zu simulieren. Es konnte so die Wirkung der Eigeninduktivitäten im Aufbau geklärt werden und das begrenzende Kriterium für eine minimale parasitäre Induktivität bestimmt werden. Der Einfluss der Keramikkondensatoren auf den Kommutierungsweg und das Schaltverhalten konnte so ebenfalls verdeutlicht werden. Entscheidend für einen minimalen Kommutierungsweg und somit für eine minimale Kommutierungsinduktivität ist, neben den Bauteil-Induktivitäten, der Kommutierungskondensator, welcher am nächsten an den Schaltern platziert ist. Dieser muss jedoch eine Mindestgröße besitzen, so dass er in der Lage ist die Energie im Schaltmoment zu übernehmen.

### Stromverteilung auf die Kondensatoren

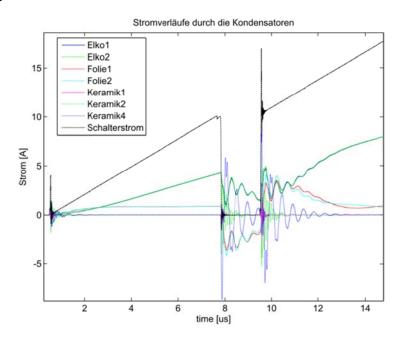

Die Simulation mit Simplorer wurde weiterhin dazu verwendet die Stromverteilung auf die Kondensatoren während des Schaltvorganges zu untersuchen. In Abbildung 2 sind der Schalterstrom sowie die Kondensatorströme abgebildet. Es ist zu erkennen, dass es hier einige Resonanzkreise gibt die zu Schwingungen führen und viel Energie zwischen den Kondensatoren hin und her geschoben wird. Auch sind die Dämpfungen und das Verhalten der verschiedenen Kondensatorarten während des Stromanstiegs und im Schaltmoment zu erkennen.

Abbildung 2: Verlauf der Schalter- und Kondensatorströme in einer Kommutierungszelle

### 2.2.3 Benchmarking eingebetteter Module und SMD-Alternativen

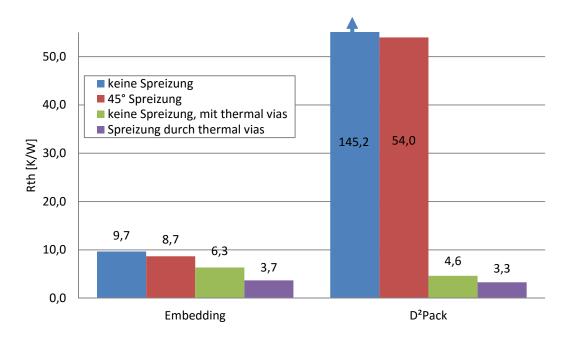

Bei dieser Voruntersuchung sollten die thermischen Eigenschaften eines "einfachen" eingebetteten Moduls (ohne Optimierungen) gegenüber einem Aufbau mit SMD Bauteilen und einer zweilagigen Standard FR4 Platine geprüft werden. Dabei wurden die thermischen Widerstände unter verschiedenen Näherungen in beiden Gehäusevarianten und mit und ohne Einsatz von Thermal-Vias, rechnerisch bestimmt. In Abbildung 3 sind die Ergebnisse dieser Untersuchung dargestellt. Es ist zu erkennen, dass ein eingebettetes Modul einen deutlich niedrigeren thermischen Widerstand besitzt als eine SMD Variante und dies obwohl die angebundene Fläche bei der Einbettung deutlich kleiner ist. Werden jedoch zusätzliche Thermal-Vias verwendet, so verbessert sich der thermische

Widerstand des SMD Aufbaus signifikant. Beide Aufbauvarianten erreichen so einen ähnlich guten thermischen Widerstand, wobei der des SMD Aufbaus, aufgrund seiner viel größeren Fläche, sogar noch etwas besser ausfällt.

Abbildung 3: Thermische Widerstände vom Chip bis zum Kühlkörper beim Aufbau als eingebettetes Modul und als SMD Aufbau, mit und ohne Thermal-Vias. Berechnung unter verschiedenen Wärmeflussannahmen.

#### 2.2.4 Thermische Bewertung der Modullösungen und Benchmarking mit gängigen Technologien

Um die thermische Performance von verschiedenen Aufbauvarianten bewerten zu können, wurde der thermische Widerstand R<sub>th</sub> vermessen. Hierbei wurden verschiedene diskrete SMD Gehäuse mit unterschiedlichen Chipgrößen, sowie die Technologie der Einbettung miteinander verglichen. Bei den diskreten Gehäusen wurden Thermal-Vias eingesetzt, deren Wirkungsfläche ebenfalls variiert wurde. Zur thermischen Anbindung an den Kühlkörper wurde zum einen eine thermisch leifähige und elektrisch Isolierende Folie verwendet und zum anderen Wärmeleitpaste. Hierbei konnte die Wärmeleitpaste nur bei den eingebetteten Modulen verwendet werden, da diese Aufgrund ihrer IMS Struktur elektrisch isoliert sind.

Ein zentrales Ergebnis der Messungen ist, dass die thermische Performance zwischen diskreten Gehäusen mit Thermal-Vias und der Einbettungs-Technologie mit IMS Struktur sich im gleichen Bereich bewegen. Hierbei hat die Dicke der Isolierung zwischen Chip und IMS Bodenplatte einen großen Einfluss, ebenso die Chipgröße bei gleichbleibendem diskretem Gehäuse. Der Einfluss der Fläche und somit der Anzahl der Thermal-Vias hat dagegen einen kleineren Effekt auf den thermischen Widerstand. Mit dieser Messung konnten die theoretischen Ergebnisse der thermischen Performance zwischen diskreten SMD Gehäuse mit Thermal-Vias und der Einbettung von Halbleitern bestätigt werden.

### 2.3 Eingebettete Leistungshalbleiter

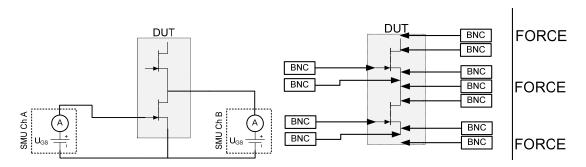

Die Universität Kassel hat das Design aller eingebetteten Module und Demonstratoren übernommen. Hierbei wurde der Fokus auf die Anordnung der Bauteile und die maximale Senkung der parasitären Effekte gelegt. Im Anschluss wurden die Module mittels des Doppelpulsverfahrens elektrisch Charakterisiert und die Demonstratoren aufgebaut, in Betrieb genommen und ihre elektrische Performance bestimmt. Zusätzlich wurde ein Vergleich zwischen den eingebetteten und diskreten SMT Gehäusen der verwendeten Leistungsschalter durchgeführt.

### 2.3.1 Untersuchung eingebettetes OptiMOS-Modul

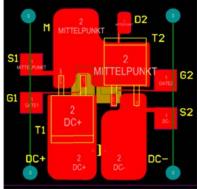

Für die erste Aufbauvariante wurden Silizium MOSFETs aus der Produktfamilie der OptiMOS (100V/100A) verwendet, welche als Halbbrücke realisiert wurde. Der Fokus bei diesem eingebetteten Modul lag in der Einführung und Beherrschung der Prozesse zur Herstellung des Moduls. Aufgabe der Universität Kassel bestand darin, ein einfaches und ein für die Anwendung im Labor geeignetes Design zu entwerfen und im Anschluss die allgemeine Funktionsweise zu prüfen. Da die Herstellung des eingebetteten Moduls auf reiner FR4-Basis fertigungstechnisch nicht zu funktionsfähigen Modulen geführt hat, wurde der Aufbau mittels der IMS Technologie realisiert. In Abbildung 4 ist das Design des ersten Entwurfs zu sehen. Die IMS-Aufbauvariante ist mit diesem fast identisch, es wurden nur die Thermal-Vias und der Bottom-Layer (blau) entfernt, da dieser nicht mehr benötigt wurde.

Abbildung 4: Design des ersten eingebetteten Testmoduls mit OptiMOS Halbleiterchips

### 2.3.1.1 Elektrische Vermessung des OptiMOS-Moduls

Zu Beginn wurden alle Module einem allgemeinen Funktionstest unterzogen: Vorwärtsverhalten, Rückwärtsverhalten (Test der intrinsischen Diode), Breakdown-Test und R<sub>DS(on)</sub>. Erst bei der zweiten Modulserie auf IMS-Basis der Firma Ruwel International GmbH waren funktionsfähige Module vorhanden (9 von 12 Stück). Parallel hierzu wurden funktionsfähige Module der TU Berlin geliefert, welche für die weiteren Test verwendet wurden.

1 Referenzplatine mit D<sup>2</sup>Pak 2-Platinen-System

2 Referenzplatine mit D<sup>2</sup>Pak 1-Platinen-System

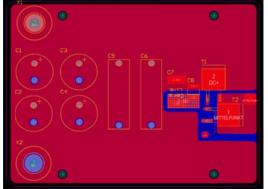

Abbildung 5: Aufbauvarianten zum eingebettetem Modul mit diskreten Gehäusen und OptiMOS Halbleitern

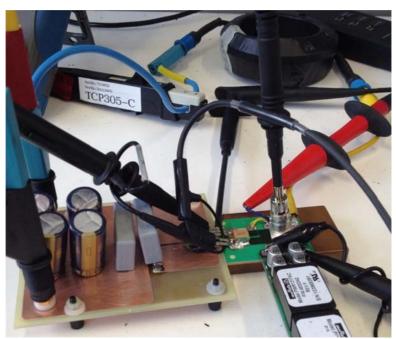

Im Rahmen des Projektes wurde sich auf ein 2-Platinen-System geeinigt. Um eine elektrische Charakterisierung der eingebetteten Module zu erhalten, ist ein Doppelpulstest durchgeführt worden. Hierfür wurde eine zweite Platine für den Zwischenkreis entworfen. Um die Einbettungs-Technologie mit den herkömmlichen diskreten Gehäuseformen vergleichen zu können, wurde eine zweite Modul-Platine entworfen, die die gleichen Ausmaße wie das eingebettete Modul besitzt, jedoch wo die gleichen Schalter in einem diskreten D<sup>2</sup>Pak Package verwendet werden. Diese erste Referenzplatine ist 2-lagig und auf FR4-Basis. Zudem wurde eine zweite Referenzplatine entworfen, bei welcher alle diskreten Komponenten auf einer einzigen FR4-Platine aufgebaut wurden, so dass die Vor- und Nachteile des 2-Platinen-Systems mit denen des 1-Platinen-Systems verglichen werden konnten. In Abbildung 5 sind die beiden zusätzlichen Aufbauvarianten dargestellt und in Abbildung 6 ist der Versuchsaufbau zu sehen. Zur Verbindung zwischen den Platinen wurden SMD Strombügel verwendet. Ein 220nF Keramik-Kondensator war als Kommutierungskondensator direkt auf dem Modul aufgebracht, um so die Kommutierungsinduktivität so klein wie möglich zu halten. Zusätzlich wurden verschiedene Kondensator-Variationen im Aufbau eingesetzt und deren Auswirkungen auf die elektrische Performance untersucht, sowie erste Dämpfungsmaßnamen eingeführt. Außerdem wurde bei den Messungen der neue CeraLink Kondensator der Firma Epcos als Kommutierungskondensator getestet

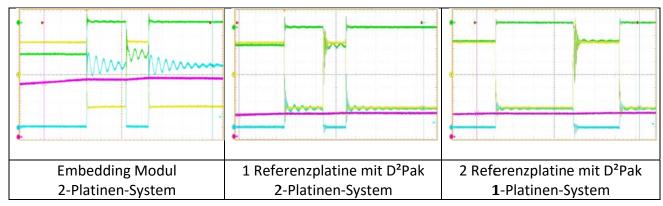

In Abbildung 7 sind die Doppelpulsverläufe der drei Aufbauvarianten dargestellt. Bei allen drei Aufbauten befinden sich die Überspannungen an ihren oberen Grenzen. Es ist zu erkennen, dass aufgrund geringerer Überspannungen ein deutlich höherer Arbeitspunkt beim eingebetteten Modul gewählt werden konnte (50V/ 45A), im Gegensatz zu den Aufbauvarianten mit diskreten Gehäusen (28V/ 19A und 28V/ 23A). Auch ist zu sehen, dass durch das 2-Platinen-System eine deutlich größere und viel schwächer gedämpfte Grundschwingung vorhanden ist. Diese ist auf die höheren parasitären Induktivitäten der Zwischenkreisanbindung zurückzuführen.

Abbildung 6: Messaufbau des eingebetteten OptiMOS-Moduls mit Zwischenkreisplatine für den Doppelpulstest

Abbildung 7: Strom und Spannungsverläufe der verschiedenen Aufbauvarianten mit dem OptiMOS Chip (grün: Diodenspannung, blau: Schalterspannung, gelb: Gatespannung, magenta: Drosselstrom)

Es hat sich der Vorteil der Einbettungs-Technologie gegenüber dem Aufbau mit diskreten Bauteilen gezeigt. Die elektrische Performance in Bezug auf Überspannungen, Spannungsverläufe und Schaltgeschwindigkeiten waren deutlich besser.

Unterschiede zwischen dem 1- und 2-Platinen-Systems finden sich hauptsächlich in den Oszillationen wieder. Der Aufbau im 1-Platinen-System verringert die Oszillationen der Grundschwingung deutlich. Es hat sich gezeigt, dass ein Aufbau der Embedding Technologie, welche direkt in die Leiterkarte integriert wird, die meisten Vorteile bringen würde. Unabhängig vom Aufbau mit einer oder mehreren Leiterplatten, haben sich deutliche elektrische Vorteile der Embedding Technologie gegenüber dem Aufbau mit diskreten Packages gezeigt.

# 2.3.2 Untersuchung eingebettetes JFET-Modul

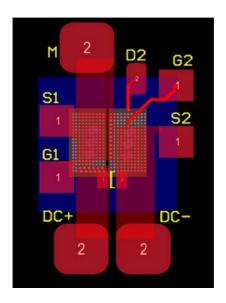

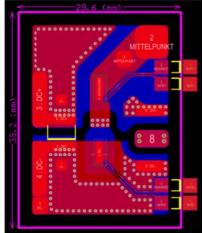

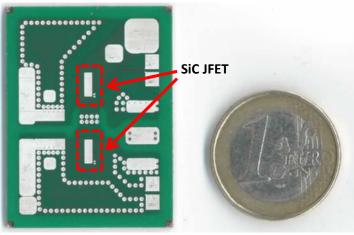

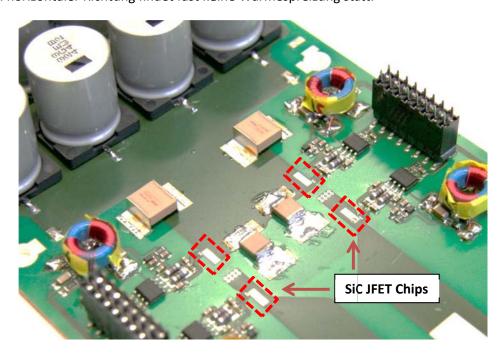

Der zweite Prototyp mit eingebetteten Schaltern wurde mit neuen Silizium-Carbid (SiC) JFET 650V normally on Leistungshalbleiterschaltern der Firma Infineon Technologies AG realisiert. Hierfür wurden ebenfalls zwei Schalter verwendet und das Modul als Halbbrücke aufgebaut. Der Versuchsaufbau wurde als ein 2-Platinen-System realisiert. Auf der Hauptplatine waren neben dem Zwischenkreis auch die Treiber-Versorgung, die Schalteransteuerung und die Speicherdrossel aufgebracht. Kupferbänder haben den Zwischenkreis mit dem Modul verbunden und Null Ohm Melf Widerstände die Schalter mit dem Treiber. Die Speicherdrossel selbst diente ebenfalls als Verbindungsglied zwischen den beiden Platinen. In Abbildung 8 ist das Design und das gefertigte Modul mit den eingebetteten JFET Schaltern zu sehen, welches eine Größe von ca. 2,9cm x 3,9cm besitzt. Der gesamte Aufbau des Doppelpulsversuches ist in Abbildung 9 dargestellt.

Abbildung 8: Design des eingebetteten JFET Halbbrücken-Moduls (links) und das fertige Modul (rechts) (

Abbildung 9: Aufbau Doppelpulsversuch mit eingebettetem JFET Halbbrücken-Modul

Zusätzlich wurden zwei weitere Module mit diskretem SMD Gehäuse und den gleichen Schaltern aufgebaut. Das Erste wurde über eine zweilagige FR4 Platine und das Zweite über eine einlagige IMS-Platine realisiert. So konnten die verschiedenen Technologien hinsichtlich ihrer elektrischen wie auch ihrer thermischen Eigenschaften miteinander verglichen werden. Alle drei Aufbauvarianten wurden über den Doppelpulsversuch untersucht und als Tiefsetzsteller betrieben.

|                        | Einschaltmoment               |                            | Ausschaltmoment               |                             |

|------------------------|-------------------------------|----------------------------|-------------------------------|-----------------------------|

| Aufbauvariante         | U <sub>max,Freilauf</sub> [V] | du/dt <sub>on</sub> [V/ns] | U <sub>max,Schalter</sub> [V] | du/dt <sub>off</sub> [V/ns] |

| <b>Eingebettet IMS</b> | 443                           | 64,4                       | 108                           | 13,1                        |

| Diskret IMS            | 483                           | 25,3                       | 412                           | 14,5                        |

| Diskret FR4            | 451                           | 22,5                       | 416                           | 15,1                        |

Tabelle 7: Ergebnis Doppelpulsversuch der drei Aufbauvarianten mit dem SiC JFET Schaltern

Entsprechend der im Projekt gewählten Spezifikationen, wurde ein Arbeitspunkt für den Doppelpulsversuch von 400V und 10A gewählt. In Tabelle 7 sind die Ergebnisse der Doppelpulsmessungen mit den SiC JFET Modulen gegenübergestellt. Es ist zu erkennen, dass die Überspannungen bei dem eingebetteten Modul deutlich niedriger sind, vor allem im Ausschaltmoment. Auch das Einschaltverhalten der eingebetteten Variante ist signifikant besser.

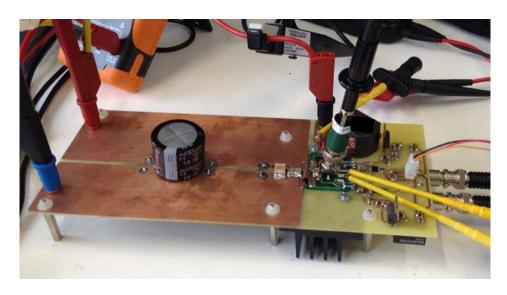

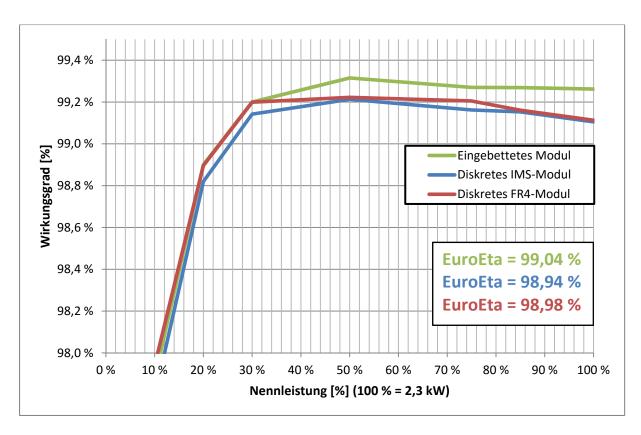

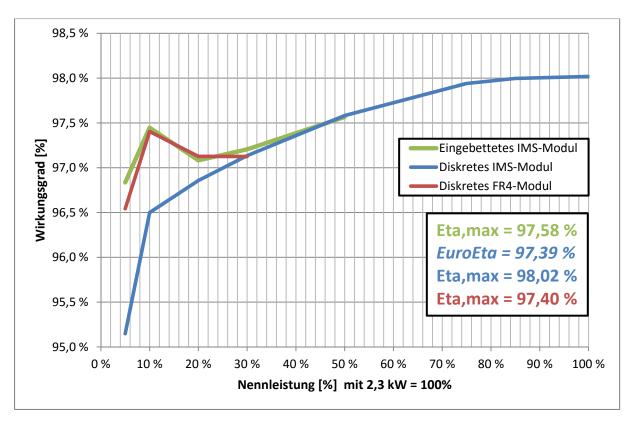

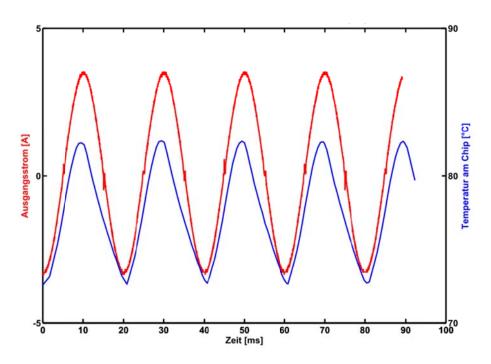

Im Anschluss wurden alle drei Aufbau-Varianten als Tiefsetzsteller mit den Zielspezifikationen betrieben. Die gewählte Eingangsspannung lag somit bei 400V, welche auf netzkonforme 230V herunter gesetzt wurde, bei einer Nennleistung von 2,3 kW. Da die Schalter mit einer Pulsweitenmodulation (PWM) angesteuert wurden, wurden am Ausgang positive sinusförmige Halbwellen mit einer Frequenz von 100Hz erzeugt, so dass über einen dahinter geschalteten Polwender eine netzkonforme 50Hz Spannung bzw. Strom erzeugt werden konnte. Da ein Ziel im Projekt der Betrieb mit hohen Frequenzen war, wurde mit einer Taktfrequenz von 100kHz und bei freier Konvektion gestartet. Im Anschluss wurde die Taktfrequenz auf bis zu 300kHz erhöht. Die Temperaturen der Speicherdrossel und der Oberfläche direkt über den eingebetteten Halbleiterchips wurde mit einer Infrarot-Thermographie-Kamera kontrolliert. Da die Chips nur ca. 35µm unterhalb der Moduloberfläche platziert sind, ist davon auszugehen, dass die gemessenen Oberflächen-Temperaturen sehr nah bei den tatsächlichen Halbleiterchip-Temperaturen liegen. Es stellte sich heraus, dass sich die Speicherdrossel beim 100 kHz Betrieb sehr stark erwärmt und bei Nennleistung ihre thermischen Grenzen mit Temperaturen > 80°C erreicht.

Abbildung 10: Wirkungsgradmessung des Tiefsetzstellers mit drei Aufbauvarianten bei einer Taktfrequenz von 100 kHz und einer Nennleistung von 2,3 kW; fester Modulationsgrad von 0,82 und freier Konfektion

Die Temperaturen über den Halbleiterchips sind bei diesem Arbeitspunkt hingegen mit maximal 80°C unkritisch. Bei steigenden Frequenzen sinken die Drosseltemperaturen erwartungsgemäß, so dass hier keine kritischen Werte mehr erreicht werden. Die Halbleiterchip Temperaturen steigen jedoch stark an, so dass beim Betrieb mit Taktfrequenzen > 100 kHz ein Lüfter zur aktiven Kühlung verwendet werden musste. In Abbildung 10 sind die Wirkungsgradverläufe der drei verschiedenen Aufbau-Varianten bei einer Taktfrequenz von 100 kHz und bei freier Konvektion dargestellt. Es ist deutlich zu erkennen, dass die bessere elektrische Performance des eingebetteten Moduls, gegenüber den diskreten Aufbau-Varianten, weniger Verluste verursacht und somit den besten Wirkungsgrad erreicht, welcher über 99% liegt.

Ab 250 kHz Taktfrequenz konnte bei dem Aufbau mit eingebettetem Modul, aufgrund zu hoher Halbleiterchip-Temperaturen, die Nennleistung nicht mehr erreicht werden und bei 300 kHz war nur noch ein Betrieb bis 50% der Nennleistung (1.150 W) möglich. Die Halbleiterchip-Temperaturen der diskreten Aufbauvariante auf FR4-Basis besaßen bereits bei 100 kHz und Nennleistung 115°C und konnten trotz Kühlung bei 200 kHz nur noch bis 50% und bei 300kHz nur noch bei 30% der Nennleistung betrieben werden. Die diskrete Aufbau-Variante auf IMS-Basis hingegen konnte bei 300 kHz und Nennleistung betrieben werden. Die Wirkungsgradverläufe aller drei Aufbau-Varianten bei 300 kHz und aktiver Lüftung sind in Abbildung 11 dargestellt. Auch hier liegen die Wirkungsgrade aller Aufbauvarianten bei über 97%. Die gute thermische Performance des diskreten IMS-Moduls ist auch auf die Wirkung der aktiven Kühlung zurück zu führen. Die eingebetteten Halbleiterchips bieten aufgrund ihrer Größe eine geringere Fläche für die Kühlung und durch ihre planare Form kann die Wärme nicht so gut abgegeben werden. Der diskrete Aufbau hingegen bietet durch sein viel größeres Gehäuse eine sehr große Fläche, welche von der kühlenden Luft umschlossen wird. Somit kann die Wärme effektiver an die Luft abgegeben werden.

Abbildung 11: Wirkungsgradmessung des Tiefsetzstellers mit drei Aufbauvarianten bei einer Taktfrequenz von 300 kHz und einer Nennleistung von 2,3 kW; fester Modulationsgrad von 0,82 und aktiver Kühlung

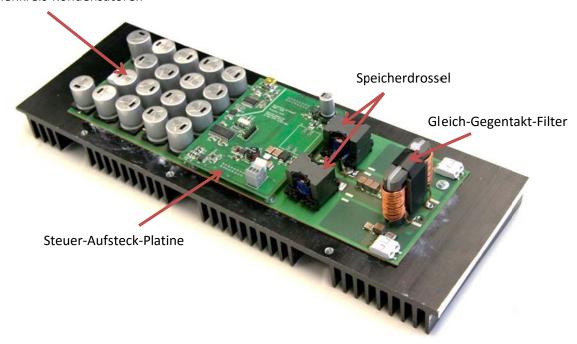

# 2.3.3 Untersuchung eingebetteter JFET-Wechselrichter

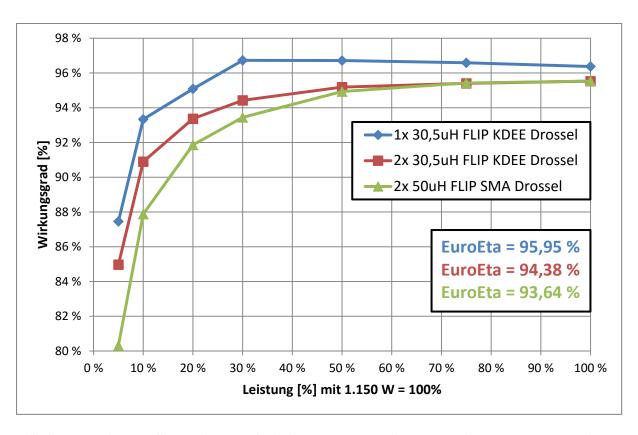

Für den endgültigen Demonstrator wurden auf die Erfahrungen und Ergebnisse des Tiefsetzsteller-Teildemonstrators zurückgegriffen. Hierfür wurden ebenfalls die bereits erprobten SiC-JFET Leistungshalbleiterschalter verwendet, sowie die gleichen Arbeitspunkte. Die gesamte Hauptplatine, auf der sich auch die Schalter befinden, besteht aus einer IMS-Leiterplatte mit einer 1mm dicken Kupfer-Bodenplatte. Der Fokus bei diesem Demonstrator lag bei einer Taktfrequenz von 300 kHz, weswegen die Nennleistung auf 1.150 W reduziert wurde. Die verwendeten Speicherdrossel (2x 30,5µH) wurden speziell für den Betrieb bei 300 kHz ausgelegt. Zusätzlich wurde der Wechselrichter mit zwei weiteren Drossel-Konfigurationen von 2x 50µH und 1x 30,5µH getestet. Die Ergebnisse der Wirkungsgradmessungen mit den verschiedenen Speicherdrossel-Konfigurationen ist in Abbildung 12 dargestellt. Es ist eine Abhängigkeit der Schalterverluste zur Drosselinduktivität erkennbar. Je kleiner die Induktivität wird, desto weniger Schaltverluste und somit auch Gesamtverluste werden erzeugt. Dementsprechend fällt auch weniger Verlustwärme bei den Schaltern ab und muss abgeführt werden. Demgegenüber stehen jedoch die Drosselverluste, welche bei immer kleiner werdender Induktivität größer werden.

Abbildung 12: Wirkungsgradkurven des PV-Wechselrichter-Demonstrators bei einer Nennleistung von 1.150 W und einer Taktfrequenz von 300kHz, in Abhängigkeit der Speicherdrossel-Konfiguration

| Aufbau     | Chip-Temperatur | <b>Drossel-Temperatur</b> | Gesamtverluste |

|------------|-----------------|---------------------------|----------------|

| 1x 30,5 μH | 112 °C          | 81 °C                     | 43,3 W         |

| 2x 30,5 μH | 125 °C          | 46 °C                     | 53,2 W         |

| 2x 50 μH   | 127 °C          | 39 °C                     | 53,4 W         |

Tabelle 8: Ergebnisse des 2. Demonstrators im Wechselrichterbetrieb bei Nennleistung von 1.150 W, 300 kHz und verschiedenen Speicherdrossel-Konfigurationen

In Abbildung 13 ist der zweite Demonstrator mit all seinen Komponenten dargestellt. Die eingebetteten SiC JFET Schalter befinden sich unterhalb der aufsteckbaren Steuerplatine, welche für die Treiber-Ansteuerung und Versorgung zuständig ist. In Abbildung 14 ist ein Ausschnitt der Demonstrator-Platine dargestellt, auf der die vier eingebetteten SiC JFET Schalter und die dazugehörigen Treiber zu sehen sind.

#### Zwischenkreis-Kondensatoren

Abbildung 13: Zweiter Demonstrator mit eingebetteten SiC JFET Leistungshalbleiterschaltern (Maße 28,8mm x 9,3mm)

Durch ein in die Aufsteckplatine gemachtes Loch konnte über eine Infrarot-Thermographie-Kamera das thermische Verhalten eines der Halbleiterschalter aufgenommen werden. Es wurden relativ große Temperaturhübe von 10°C bei einem Arbeitspunkt von 50% der Nennleistung (575W) festgestellt. In Abbildung 15 ist zu erkennen wie sich die unterschiedliche Belastung auf den Schalter aufgrund der Pulsweitenmodulation auswirkt. Es ist ebenfalls zu erkennen wie die Belastung dem sinusförmigen Ausgangsstrom folgt. Ebenfalls konnte die Temperaturverteilung an der Platinen-Oberfläche über dem Halbleiterchips aufgenommen werden. Es stellte sich heraus, dass die Temperatur innerhalb des Chips nicht gleichmäßig verteilt ist, sondern sich in der Mitte ein Hotspot bildet. In horizontaler Richtung findet fast keine Wärmespreizung statt.

Abbildung 14: Nahaufnahme der vier eingebetteten SiC JFET Schalter unterhalb der aufgesteckten Steuerplatine

Abbildung 15: Korrelation zwischen der Gehäusetemperatur eines SiC JFET Schalters und des 50 Hz Ausgangsstroms

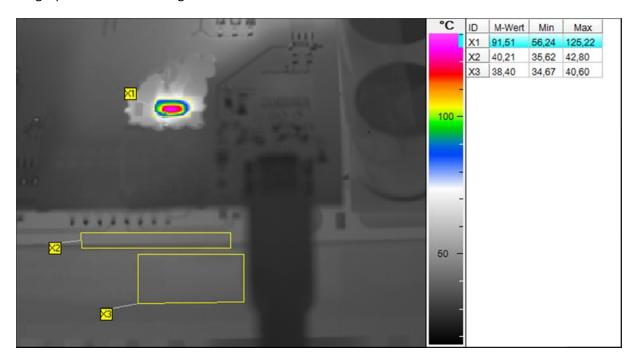

Eine verbesserte Wärmespreizung in horizontaler Richtung ist anzustreben. Dies könnte zum Beispiel erreicht werden, in dem die innere Kupferlage auf der die Halbleiterchips montiert wurden, dicker gestaltet wird oder sogar Kupferinlays verwendet werden. In diesem Aufbau ist die innere wie auch die äußere Kupferlage nur 35µm dick. In Abbildung 16 ist exemplarisch eines der Thermographie-Bilder dargestellt, welches bei Nennleistung und bei der 2x 50µH Speicherdrossel-Konfiguration aufgenommen wurde. Die Fläche X1 umrahmt den Halbleiterchip, die Fläche X2 einen Teil der IMS-Bodenplatte und X3 einen Teil des Kühlkörpers. Die angegebenen Werte rechts im Bild stellen den Mittelwert, den Minimalwert und den Maximalwert der Temperaturen in °C dar, die innerhalb der aufgespannten Flächen aufgenommen wurden.

Abbildung 16: Thermographie-Bild eines SiC JFET Schalters des 2. Demonstrators beim Betrieb mit 300 kHz, Nennleistung und den 2x 50µH Speicherdrosseln (Bereiche der Messungen: X1 Chipfläche, X2 IMS Bodenplatte, X3 Kühlkörper)

# 2.4 Magnetische Bauelemente

# 2.4.1 Speicherdrosseln für hohe Schaltfrequenzen und Stromrippel

Zur Miniaturisierung von Speicherdrosseln lassen sich zwei Strategien verfolgen. Die Erhöhung der Schaltfrequenz und die Erhöhung der Flussdichte. In jedem Fall führt die Erhöhung beider Werte zu erhöhten Kernverlusten. Die Miniaturisierung ist daher in jedem Fall durch die thermische Belastung des Materials begrenzt. Eine Verkleinerung des Bauelements erfordert die Abfuhr der Verlustleistung über eine kleinere Oberfläche. Die Verringerung des Volumens führt zwangsläufig zu einer Erhöhung der Verlustleistungsdichte. Durch eine Verbesserung der Kühlung lassen sich höhere Verlustleistungsdichten erreichen.

Letztendlich ermöglichen daher vor allem verlustarme Materialien ein hohes Miniaturisierungspotential. Wenn die umgesetzte Verlustleistung jedoch nicht mehr abgeführt werden kann, muss die Oberfläche und damit die Kerngröße zwangsläufig wieder erhöht werden.

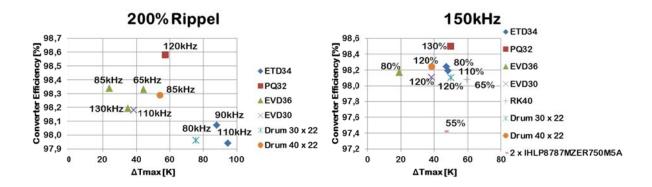

Für die Optimierung der Hochsetzsteller-Speicherdrossel wurden verschiedenen Kerngeometrien bei zwei unterschiedlichen Arbeitspunkten betrieben:

- Maximale Induktion bis zu 0,3T die Frequenz wird so niedrig wie möglich eingestellt.

- Die Betriebsfrequenz wird auf 150kHz eingestellt, die Induktion stellt sich entsprechend ein und liegt unter 0,3T.

Alle Drosseln sind leichter als 100g und weisen eine Bauhöhe von weniger als 25mm auf und erfüllen somit die Voraussetzung für eine vollautomatische SMD-Bestückung.

Weiterhin wurden alle Drosseln beidseitig an zwei Kühlkörpern angebunden. Jeder Kühlkörper hat einen thermischen Widerstand von 5 K/W, dadurch ergibt sich ein thermischer Gesamtwiderstand von 2,5 k/W. Die Drosseln werden hierbei nur passiv gekühlt.

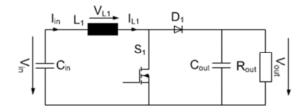

#### Bauelemente

Schalter S1: C7 CoolMOS 650V Diode D1: C3D20120 (1200V SiC)

Drossel L1: Prüfling

Abbildung 17: Schaltung des Versuchsaufbaus zur thermischen Charakterisierung der Drosseln

Die Drosseln werden mit einem 2 kW Hochsetzsteller, bei 200 V Eingangsspannung und 400 V Ausgangsspannung, betrieben. Dabei wurden der Wirkungsgrad des Konverters und die Temperaturerhöhung der Drossel für die beiden oben genannten Betriebsbedingungen gemessen. Die Ergebnisse der Messungen sind in Abbildung 18 zu finden.

Der Betrieb der Drosseln bei maximaler Induktion führt dazu, dass der Halbleiterschalter des Hochsetzstellers bei einem geringen Strom einschaltet und bei einem hohen Strom ausschaltet. Da die Einschaltverluste des Schalters jedoch deutlich höher sind als die Ausschaltverluste, verringern sich die Halbleiterverluste in diesen Betriebspunkten. Die Verluste in den Drosseln steigen jedoch an, was sich in einem erhöhten Temperaturhub ausdrückt.

Abbildung 18: Konverter-Wirkungsgrad und Temperaturhub der Drosseln

Werden die Drosseln bei 150kHz betrieben reduziert sich die Induktion. Die Verluste in der Drossel werden also geringer und der Temperaturhub verringert sich entsprechend. Dafür muss der Schalter bei einem höheren Strom einschalten, was zu erhöhten Einschaltverlusten führt. Weiterhin trägt auch die Frequenzerhöhung zu einer Erhöhung der Schaltverluste bei. Das Ausschalten bei geringerem Strom kann die erhöhten Einschaltverluste nicht kompensieren. Die Gesamtverluste der Halbleiter steigen daher an.

In Abbildung 18 sind die Hochsetzsteller Wirkungsgrade bei 2 kW Leistung für verschiedene Drosseln in Abhängigkeit des Temperaturhubs dieser Drosseln für die beiden Drossel-Betriebsbedingungen dargestellt. Die Verluste der einzelnen Komponenten (Halbleiter und Drosseln) sind dabei von untergeordneter Relevanz, solange die Temperaturbelastung der Bauteile nicht kritisch wird. Für die Optimierung des Systems ist der Konverter-Wirkungsgrad relevant, der möglichst hoch sein soll. Der Temperaturhub der Bauelemente (hier die Drosseln) soll jedoch möglichst gering sein, um eine möglichst lange Lebensdauer zu garantieren.

Die höchsten Wirkungsgrade im Versuch wurden mit der PQ32 Drossel erreicht (siehe Tabelle 9 und Abbildung 19). Der Temperaturhub ist noch moderat. Ein kleiner Wickel ermöglicht eine Begrenzung der Wicklungsverluste. Der PQ32 ist nur mit dem Kern an den Kühlkörper angebunden. Dadurch kann der Kern sehr gut gekühlt werden. Die Wicklung muss jedoch durch natürliche Konvektion und über den Kern gekühlt werden. Der leichte und kompakte Aufbau der Drossel ermöglicht entsprechende SMD-Varianten, daher und aufgrund des hohen Konverter-Wirkungsgrades kann diese Drossel für die Anwendung favorisiert werden.

| Kern                 | PQ32               | EVD36                |

|----------------------|--------------------|----------------------|

| Material             | N97                | Fi325                |

| Wicklung             | Litze 660 x 0,05mm | Litze 420 x 0,071 mm |

| Induktivität         | 49 μΗ              | 58,5 μΗ              |

| <b>DC Widerstand</b> | 18 mΩ              | 20,5 mΩ              |

| Gewicht              | 62 g               | 99,5 g               |

Tabelle 9: Daten der PQ32 (höchster Konverter-Wirkungsgrad) und der EVD36 Drossel (geringster Temperaturhub)

Der geringste Temperaturhub wurde mit der EVD36 Drossel (siehe Tabelle 9 und Abbildung 19) ermöglicht. Diese Drossel wurde mit dem Wicklungspacket und dem Kern an den Kühlkörper angebunden. Dadurch wird eine effektive Kühlung von Kern und Wicklung möglich. Da die EVD36 Drossel mit fast 100g eine der schwersten Prüflinge war wurde noch eine kleinere Variante aufgebaut. Der EVD30 ist kleiner und leichter, kann jedoch nicht zu einer Verbesserung des

Konverter-Wirkungsgrades beitragen und führt beim 150kHz Betrieb auch zu einem höheren Temperaturhub des Prüflings.

Abbildung 19: PQ32 (links) und EVD36 Drossel (rechts)

Weiterhin wurden auch zugekaufte SMD-Drosseln, wie die IHLP8787, mit Pulver-Kernmaterial, getestet. Mit einer Kantenlänge von 2,2cm und einer Höhe von 1,3cm ist diese Drossel sehr kompakt (und bereits in SMD ausgeführt). Um die Drosselverluste zu begrenzen wurde der Stromrippel reduziert, indem zwei Drosseln in Serie geschaltet wurden. Das führt jedoch zu einem hohen Gesamt-DC-Widerstand und damit hohen Drosselverlusten. Weiterhin führt der geringe Stromrippel zu hohen Einschaltverlusten des Schalters. Die sehr kompakte Bauweise der Drossel führt daher leider zu einem geringen Wirkungsgrad und ist für die vorliegende Anwendung nicht zielführend.

Weiterhin wurden auch diverse ETD-Kern-Drosseln getestet. Beim Versuch mit maximalem Stromrippel führten diese Drosseln jedoch zu einem geringen Konverter-Wirkungsgrad, wobei ein großer Anteil der Verluste in den Drosseln entsteht. Dies ist durch die Wicklungslänge, sowie dem großen Wicklungspacket und einem großen Luftspalt zu erklären, wodurch hohe Verluste in der Wicklung entstehen. Bei erhöhter Frequenz verringert sich der Temperaturhub aufgrund geringerer Proximity-Verluste in der Wicklung. Dennoch liegt der erziele Wirkungsgrad im Vergleich zu den anderen Prüflingen nur im Mittelfeld. Ähnliche Ergebnisse erzielen die mit Rollenkernen ausgeführten Drosseln (Drum). Hier drohen, aufgrund der Streufelder, erhöhte Proximity-Verluste, welche zu hohen Drosselverlusten und Temperaturhüben führen. Weiterhin wurde bei 150kHz eine RK40 Ringkern-Drossel getestet. Diese Drossel ermöglicht einen besonders geringen Stromrippel. Da die Wicklung den Kern vollständig bedeckt, müssen die Kernverluste begrenzt werden, da der Kern sich durch die Wicklung hindurch kühlen muss. Es ergibt sich ein relativ hoher Temperaturhub bei mäßigem Wirkungsgrad. Damit schein auch die Ringkern-Geometrie wenig zielführend für die Anwendung zu sein.

### 2.4.2 Gleich-Gegentaktdrosseln für EMV Filter

Magnetische EMV Filterbauelemente werden in Gegentakt- und Gleichtaktdrosseln unterteilt. Die Bauelemente sind entsprechend für die Dämpfung von Gleich- oder Gegentaktstörungen optimiert. Sie weisen jedoch auch eine parasitäre Streuinduktivität auf. In der Praxis wird versucht die parasitäre Streuinduktivität von Gleichtaktdrosseln für die Gegentakt-Dämpfung des EMV Filters nutzbar zu machen. Da Gleichtaktdrosseln häufig mit Ringkernen realisiert werden, ist deren Streuinduktivität i.d.R. sehr gering. Gleichtaktdrosseln können daher keinen signifikanten Beitrag zu Gegentakt-Dämpfung leisten. Durch entsprechende Modifizierung der Kerngeometrie oder durch die Wahl einer anderen Kerngeometrie lassen sich entsprechende Erhöhungen der Streu-, bzw.

Gegentakt-Induktivitäten, erzielen. Dadurch entstehen magnetische Bauelemente, welche Gleichund Gegentaktstörung effektiv Dämpfen können.

Die Erhöhung der Gegentakt-Induktivität kann durch Erhöhung der Windungszahl, die auch die Gleichtakt-Induktivität erhöht, oder durch das Einfügen von ferromagnetischen Segmenten in den Streupfad des Bauelements erfolgen. Beim Einfügen von ferromagnetischen Segmenten in den Streupfad ergibt sich eine Erhöhung des magnetischen Flusses. Dadurch ergibt sich eine bessere Ausnutzung des Kernmaterials. Es muss jedoch darauf geachtet werden, dass der Kern nicht in Sättigung gerät, da sonst keine Filterdämpfung mehr auftritt.

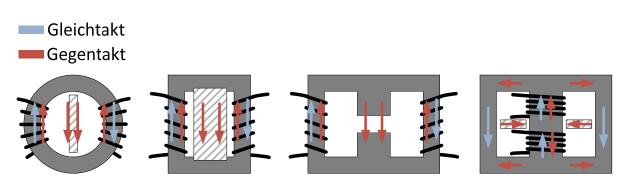

Für den Entwurf von Gleich-Gegentaktdrosseln können verschiedene Kerngeometrien gewählt werden. Die Auswahl der Geometrie und des Kernmaterials haben erheblichen Einfluss auf die Gleich- und die Gegentaktinduktivität des Bauelements. Prinzipiell können die Bauelemente für die Dämpfung von Gleichtakt- oder Gegentaktstörungen optimiert werden, wobei der Entwurf von Bauelementen mit signifikanten Gleich- und Gegentakt-Induktivitäten ebenfalls möglich ist. Im nachfolgenden werden die einzelnen Geometrien und deren inhärente Eigenschaften kurz beschrieben:

- Ringkerne: Ringkerne ermöglichen die Realisierung von hohen Gleichtakt-Induktivitäten. Sie werden daher bevorzugt zur Gleichtaktdämpfung eingesetzt. Die Streuinduktivität ist aufgrund der Geometrie sehr gering. Häufig beträgt die Streuinduktivität weniger als 1% der Gleichtaktinduktivität. Um signifikante Gegentakt-Induktivitäten zu ermöglichen, müssen ferromagnetische Segmente in die Bauelemente-Struktur eingefügt werden. Dabei gibt es prinzipiell folgende Möglichkeiten:

- Streusegment im Joch des Ringkerns: Diese Maßnahme führt in der Praxis maximal zu einer Verdopplung der Streuinduktivität. Wenn nur begrenzte Gegentakt-Induktivitäten benötigt werden, lässt sich diese Methode ohne Mehraufwand implementieren. Die Wicklungen auf den Ringkernen werden ohnehin durch Plastiksegmente getrennt. Diese werden einfach durch Ferrit-Segmente ersetzt. Der Kostenaufwand ist hierbei, aufgrund des geringen Materialeinsatzes, minimal.

- Streusegment außerhalb des Ringkerns: Hier gibt es verschiedene Möglichkeiten das Segment zu platzieren. Parallel zur Wicklung und/oder oberhalb und unterhalb des Ringkerns. Da der Großteil des Streuflusses sich im Außenbereich zum Ringkern zurück schließt, kann die Gegentakt-Induktivität mit dieser Methodik auch vervielfacht werden. Dafür werden aber ggf. große und schwere ferromagnetische Segmente benötigt, die sowohl die Bauteilkosten, als auch Gewicht und Volumen deutlich erhöhen.

U-Kerne werden i.d.R. in zwei Hälften gefertigt. Das ermöglicht den Einsatz von Wickelkörpern. D.h. die Wicklungen können besser automatisiert gefertigt werden, was bei den Ringkernen nur bei kleinen Leiterquerschnitten möglich ist. Die Verwendung von zwei

Kernhälften führt jedoch auch zu dem Nachteil, dass sich beim Zusammenstecken der beiden Kernhälften sehr kleine Luftspalte an den Schnittflächen der Kerne ergeben. Diese verringern vor allem die Gleichtakt-Induktivität. Daher müssen zur Realisierung von hohen Gleichtakt-Induktivitäten ggf. mehr Windungen aufgetragen werden, was zwar die Verluste erhöht, im Gegenzug aber auch zu einer Erhöhung der Gegentakt-Induktivität führt.

- **E-Kerne**: Bei den E-Kernen ergeben sich zwei unterschiedliche Platzierungsmöglichkeiten für die Wicklungen:

- O Wicklungen auf den Außenschenkeln: Bei diesem Aufbau werden nur die Außenschenkel als Gleichtakt-Flusspfad verwendet, da sich der Gleichtaktfluss im Mittelschenkel aufhebt. Der Gegentaktfluss schließt sich entsprechend über den Mittelschenkel. Dadurch ermöglicht ein Luftspalt im Mittelschenkel die Einstellung der Gegentakt-Induktivität. Da sowohl der Gleich- als auch der Gegentaktfluss durch ferromagnetische Kernabschnitte fließen, lässt sich das Bauelement leicht auslegen und Gleich- und Gegentakt-Induktivitäten unabhängig voneinander einstellen.

- Wicklungen auf dem Mittelschenkel: Hier werden i.d.R. beide Wicklungen übereinander platziert. Diese Platzierung bietet eine einfache und Kostengünstige Aufbautechnik. Der Streufluss schließt sich senkrecht durch die Wicklungen und quer durchs Wickelfenster. Die Streuinduktivität kann erhöht werden, indem ferromagnetische Segmente ins Wickelfenster eingebracht werden.

Da E-Kerne, genau wie U-Kerne, i.d.R. geteilt werden, lassen sich die Wicklungen auf Wickelkörper aufbringen. Bei der Teilung des Kerns muss auch hier darauf geachtet werden, dass die kleinen Luftspalte an den Anlageflächen zu einer Permeabilitäts-Verringerung für die Gleichtakt-Induktivität führen.

• Pot-Kerne: Bei den Pot- oder Schalten-Kernen werden die Wicklungen auf dem Mittelschenkel aufgebracht. Der Querschnitt ist i.d.R. Rund, was, im Vergleich zum E-Kern, zu einer Minimierung der mittleren Windungslänge führt. Der Streufluss breitet sich genau wie beim E-Kern quer durch das Wickelfenster aus. Zur Erhöhung der Gegentakt-Induktivität kann eine ferromagnetische Scheibe ins Fenster eingebracht werden. Schalenkerne haben den Vorteil, dass der Kern selbst eine gute Abschirmung ermöglicht und sich somit nur sehr kleine Streufelder in der Umgebung des Bauteils ausbreiten. Schalenkerne sind jedoch sehr kostspielig. Die Integration von angepassten Segmenten für die Erhöhung der Gegentakt-Induktivität treiben die Kosten noch weiter nach oben.

Abbildung 20: Prinzipieller Aufbau verschiedener Gleich-Gegentakt-Drosseln; von links nach rechts: Ring-Kern, U-Kern, E-Kern, E- oder Pot-Kern

Abbildung 20 zeigt die zuvor beschriebenen Geometrien mit beispielhaften Streusegmenten und der entsprechenden Ausbreitung des Gleich- und Gegentakt-Flusses.

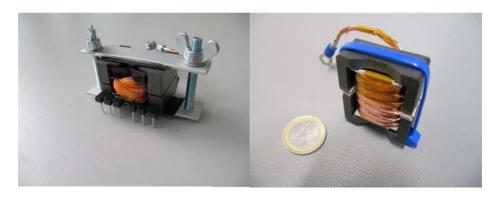

Im Rahmen des Projekts wurden verschiedene Gleich-Gegentaktdrosseln entworfen und aufgebaut. Dabei wurden hauptsächlich Ring- und U-Kerne verwendet (siehe Abbildung 21 und Abbildung 23). Beim Entwurf kann entweder die Gentakt- oder die Gleichtakt-Induktivität priorisiert werden. Bei Ringkernen wird i.d.R. primär die Gleichtakt-Induktivität ausgelegt. Diese lässt sich einfach über die Kerngröße (bzw. über den Induktivitätsfaktor oder AL-Wert) und die Windungszahl skalieren. Die Gegentakt-Induktivität stellt sich entsprechend ein, wobei große Kerne und viele Windungen entsprechend auch zu großen Gegentakt-Induktivitäten führen.

Für einen Einsatz im EMV Filter muss auch darauf geachtet werden, dass die parasitäre Kapazität der Drossel begrenzt wird. Da der Einsatz eines ferromagnetischen Kerns nicht vermieden werden kann, müssen die Wicklungskapazitäten minimiert werden. Hier ist die Implementierung von einlagigen Wicklungen zu bevorzugen. Sollte dies nicht möglich sein, sollten Wickeltechniken angewandt werden, welche die Potentialdifferenzen zwischen nebeneinander liegenden Windungen begrenzen (z.B. Z-Wicklung).

Abbildung 21: Ring-Kerne mit verschiedenen Streu-Segmenten

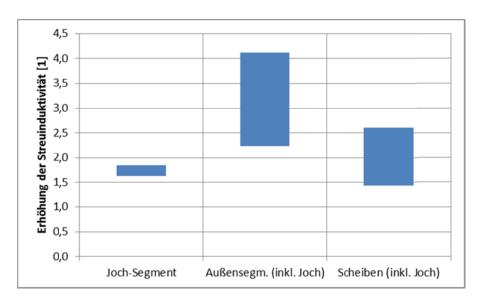

In Abbildung 22 ist die Erhöhung der Streuinduktivität von Ringkern-Gleich-Gegentaktdrosseln durch verschiedene Segmente dargestellt. Die Anordnung der Segmente kann beispielhaft Abbildung 21 entnommen werden. Das Diagramm beinhaltet die Messergebnisse der Streuinduktivität von verschiedenen Drosseln, die während des Projekts aufgebaut wurden, um den Einfluss der Streusegmente zu untersuchen. Dargestellt sind die Ergebnisse aus 26 Messungen mit unterschiedlichen Drosselkombinationen und verschiedener Kerne.

In Abbildung 22 ist zu erkennen, dass die Streusegmente im Joch die Streuinduktivität der gewählten Prüflinge um bis zu 85% erhöhen konnten. Da es bei der Dimensionierung der Streusegmente im Joch nur einen begrenzten Spielraum gibt, ergibt sich auch nur eine geringe Variation der Ergebnisse. Bei der Platzierung der Außensegmente und der Scheiben-Segmente ergeben sich deutlich größere Variationen, da sich hier durch die Größe des Segments selbst mehr Skalierungsmöglichkeiten ergeben. Weiterhin kann auch der Abstand zum Ringkern eingestellt werden, was einen erheblichen Einfluss hat. Außerdem lassen sich auch verschiedene Kombinationen für zusätzliche Segmente realisieren – z.B. ein Streusegment im Joch und zwei Scheiben ober- und unterhalb. Es ist zu erkennen, dass eine Erhöhung der Streuinduktivität um den Faktor 4 mit den Außensegmenten möglich ist. Mit den Scheibensegmenten ober- und unterhalb des Ringkerns konnte die Streuung auf den 2,5-fachen Wert erhöht werden.

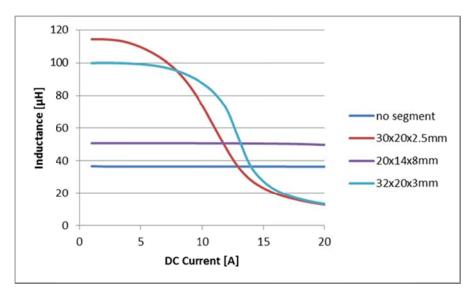

Abbildung 22: Erhöhung der Streuinduktivität für Ringkern-Gleich-Gegentakt-Drosseln bei verschiedenen Streu-Segment-Anordnungen

Da der Einsatz von Segmenten außerhalb des Kerns sowohl Volumen, als auch Gewicht des Bauteils deutlich erhöht, wurde für die Entwicklung von weiteren Gleich-Gegentaktdrosseln ein UR-Kern gewählt. Die Daten der ausgelegten Gleich-Gegentaktdrossel, die auch für den zweiten Demonstrator verwendet wurde, sind in Tabelle 10 zu finden. Die Streuinduktivität wurde mittels eines aufgeklebten Mittel-Segments auf beiden Seiten erhöht. Durch den Spalt zwischen UR-Kern und Segment kann die Streuinduktivität sehr genau eingestellt werden. Abbildung 24 zeigt die gemessene Streuinduktivität für verschiedene Streu-Segmente. Hier lässt sich gut erkennen, dass bei einer Fehl-Anpassung des Luftspalts eine partielle Sättigung der Drossel auftreten kann. Daher muss die Streuinduktivität entsprechend begrenzt werden. Dennoch lässt sich durch Wahl der Geometrie, die bereits eine erhebliche Streuinduktivität aufweist, auch eine deutliche Erhöhung der Streuinduktivität erreichen. Diese konnte von 37μH (ohne Segment) bis auf 100μH erhöht werden, was einer Erhöhung um den Faktor 2,7 entspricht. Auf eine Erhöhung auf 114μH wurde verzichtet, um eine Sättigung des Kerns zu vermeiden.

| Kern     | UR42             |

|----------|------------------|

| Material | 77               |

| Wicklung | Volldraht 1,12mm |

|          | je 17 Windungen  |

| Lcm [µH] | 794              |

| Ldm [μH] | 36 – 114         |

| Rdc [mΩ] | Max. 15          |

Tabelle 10: Daten der UR42 Gleich-Gegentaktdrossel

Abbildung 23: UR-Kern Gleich-Gegentaktdrossel mit (links) und ohne (rechts) Streu-Segment

Abbildung 24: Streuinduktivität der UR-Kern-Gleich-Gegentaktdrossel für verschiedene Streu-Segmente

# 2.4.3 EMV Filter mit magnetisch integrierten Komponenten (für Demonstrator 1)

Vor allem die Implementierung von hohen Filterdämpfungen erfordert große Induktivitäts- und Kapazitätswerte. Obwohl die Erhöhung von geforderten Dämpfungswerten auch durch die Erhöhung der Anzahl der Filterstufen ermöglicht werden kann, wird der Aufwand für das Filter in jedem Fall größer. Entweder werden die Filterbauelemente selbst größer, oder es werden mehr Bauelemente benötigt. Beides führt zu erhöhtem Aufwand und damit erhöhten Kosten.

Durch die Implementierung von Gleich-Gegentaktdrosseln, die sowohl Gleich-, als auch Gegentakt-Störungen effektiv dämpfen können, lässt sich jedoch der Aufwand begrenzen. Eine Erhöhung der Gegentakt-Induktivität bei vorhandenen Gleichtaktdrosseln lässt sich mit begrenztem Aufwand realisieren. Dadurch kann auf zusätzliche Gegentaktdrosseln im Filter verzichtet werden und damit eine Erhöhung des Filterinnenwiderstandes vermieden werden.

Für den ersten (Tiefsetzsteller-) Demonstrator wurden zwei Filter ausgelegt (siehe Abbildung 25). Filter 1 wurde dabei nur mit diskreten Bauelementen bestückt, wobei Filter 2 die vorher entwickelten Gleich-Gegentaktdrosseln verwendet (siehe Abbildung 23 und Tabelle 10). Da die Streuinduktivität der diskreten Gleichtaktdrosseln von Filter 1 zu gering war, um die gewünschte Dämpfung zu erreichen, wurden je Filterstufe zwei zusätzliche diskrete Gegentaktdrosseln eingebaut. Bei Filter 2

wurden die diskreten Gegentakt-Drosseln dann zusammen mit den Gleichtakt-Drosseln durch die entwickelten Gleich-Gegentaktdrosseln ersetzt. Dadurch konnte der Innenwiderstand des Filters, von  $152m\Omega$  auf  $108m\Omega$ , um fast 30% reduziert werden, was auch für die Verluste des Filters gilt. Gleichzeitig wurde die Anzahl der benötigten Komponenten um vier Bauelemente reduziert.

Filter 1: mit diskreten Bauelementen Filter 2: mit integrierten Gleich-Gegentaktdrosseln

Abbildung 25: EMV-Filter mit diskreten Drosseln und mit integriertern Gleich-Gegentakt-Drosseln

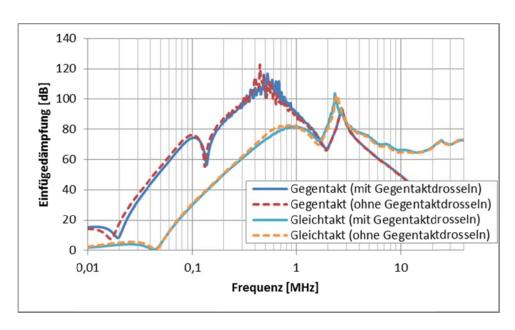

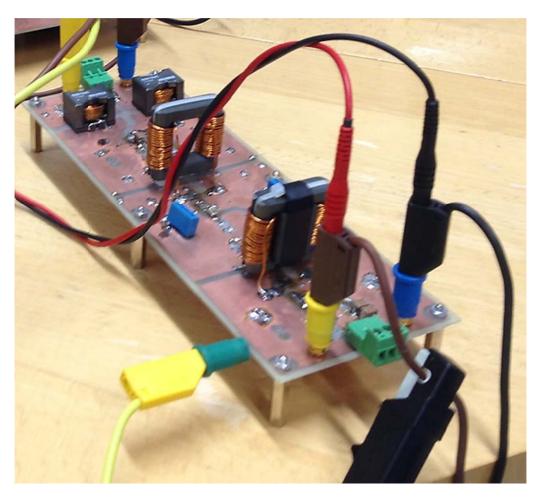

Abbildung 26 zeigt die Einfügedämpfung für den Gleich- und den Gegentakt der beiden EMV Filter nach Abbildung 25 im Vergleich. Beim Vergleich der Einfügedämpfung in Abbildung 26 ist zu erkennen, dass sich beide Filter nahezu identisch Verhalten. D.h. die konstruktiven Änderungen im Filteraufbau haben sich nicht nachteilig auf die Dämpfung ausgewirkt. Abbildung 27 zeigt den Aufbau des Filters nach Abbildung 25 mit den Gleich-Gegentaktdrosseln. Dieses Filter wurde mit dem eingebetteten JFET Modul aus Kapitel 2.3.2 getestet.

Abbildung 26: Gegen- und Gleichtaktdämpfung eines EMV-Filters mit und ohne diskrete Gegentaktdrosseln

Abbildung 27: EMV-Filter mit zweistufigem Gleich-Gegentakt-Filter

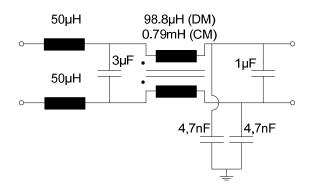

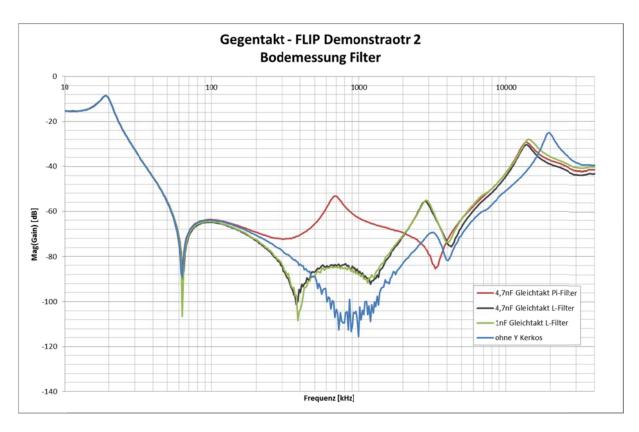

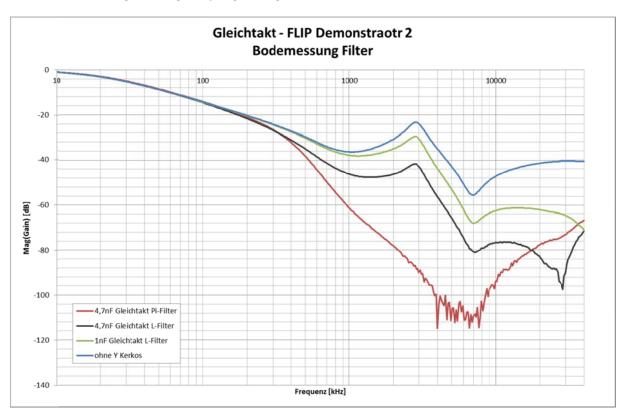

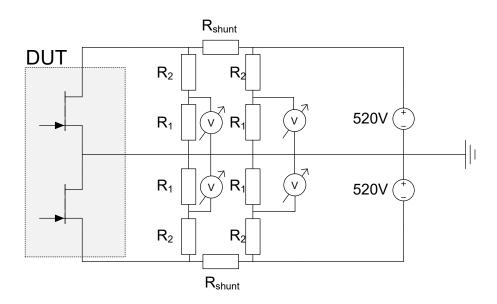

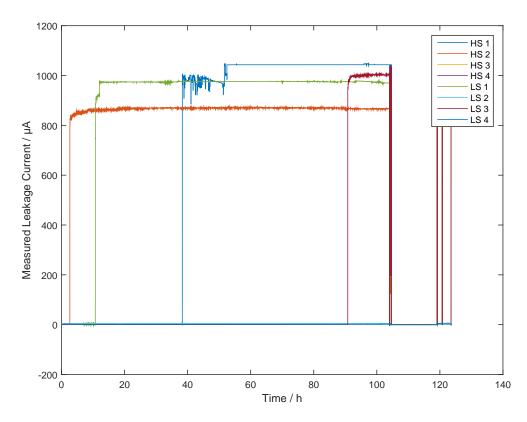

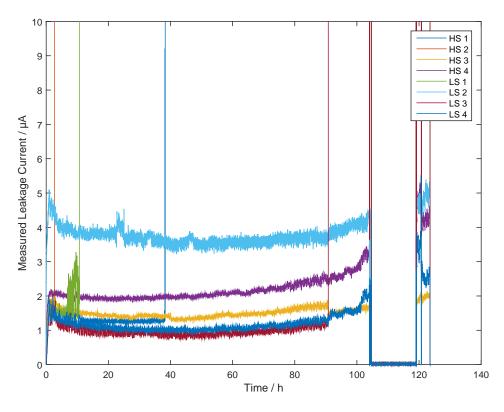

# 2.4.4 EMV Filter für Demonstrator 2