# Device Characterization and Modeling of Large-Size GaN HEMTs

Jaime Alberto Zamudio Flores

Jaime Alberto Zamudio Flores

Device Characterization and Modeling of Large-Size GaN HEMTs

This work has been accepted by the Faculty of Electrical Engineering and Computer Science of the University of Kassel as a thesis for acquiring the academic degree of Doktor der Ingenieurwissenschaften (Dr.-Ing.).

Supervisor: Prof. Dr.-Ing. G. Kompa Co-Supervisor: Prof. Dr.-Ing. A. Bangert

Defense day: 23 April 2012

Bibliographic information published by Deutsche Nationalbibliothek

The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie;

detailed bibliographic data is available in the Internet at <a href="http://dnb.dnb.de">http://dnb.dnb.de</a>.

Zugl.: Kassel, Univ., Diss. 2012 ISBN print: 978-3-86219-364-6 ISBN online: 978-3-86219-365-3

URN: http://nbn-resolving.de/urn:nbn:de:0002-33651

© 2012, kassel university press GmbH, Kassel www.uni-kassel.de/upress

Printed in Germany

#### Aknowledgments

I wish to express my sincere gratitude to my Ph. D. supervisor Prof. Dr.-Ing. G. Kompa, for giving the opportunity to pursuit my degree under his supervision when he was head of the former High-Frequency Engineering (HFT) Department, now Department of Microwave Electronics (MiCEL), of the Kassel University. I thank him for his confidence in me during the research projects in which I participated, as well as for his unvaluable guidance and support throughout the development of the research work that is presented here.

I am also deeply thankful to my second examiner Dr.-Ing. A. Bangert, head of the Department of Microwave Electronics (MiCEL) of the Kassel University, for his continued support to my research and for giving me the chance to collaborate in other projects of the MiCEL Department.

Also many thanks to the other members of the examination committee Prof. Dr. sc. techn. Bernd Witzigmann and Prof. Dr.-Ing. Peter Lehmann for accepting to sit in the commission and to evaluate my research work.

I thank my present colleagues and co-workers at MiCEL for all their assistance, the time shared and their team-work spirit: A. A. Hussein, R. Ghahremani, R. J. Hadi, R. Chatim, C. Sandhagen and H. Nauditt-Ruppel; and also to those colleagues who left the Department at some point during my work: Dr. S. Dahmani, Dr. S. E. Ramanujam, B. Wittwer, Dr. R. Ma, Dr. S. Monsi, Dr. A. Z. Markos and Dr. A. Jarndal.

Special thanks to Dr. E.S. Ramanujam and B. Wittwer for performing single-tone and two-tone measurements for model verification, and to Dr. Dahmani for his heat-transfer simulations and fruitful discussions, which have helped me in the electro-thermal modeling part of the present work.

Thanks also to Dr. M. Schlechtweg and Dr. R. Quay of the Fraunhofer Institute for Applied Physics (IAF, Freiburg im Breisgrau) for supplying GaN HEMTs that were used in the present work.

Finally, I wish to thank the German Acadamic Exchange Service (DAAD) and the Mexican National Council of Science and Technology (CONACyT) for granting me a Ph. D. scholarship.

Jaime Alberto Zamudio Flores Kassel, February 2012.

## **Index of Contents**

|      | t of Figuresv                                                |      |

|------|--------------------------------------------------------------|------|

| List | t of Tablesx                                                 | xix  |

| List | t of Symbols                                                 | XX   |

| List | t of Abbreviations and Acronymsx                             | XV   |

| Abs  | stractxx                                                     | vii  |

|      | sammenfassungx                                               |      |

| Cha  | apter 1 Introduction                                         | 1    |

| 1.1  | Elements of the UMTS Technology                              | . 2  |

| 1.2  | Transistors with Wide-Bandgap Semiconductors for UMTS        |      |

| 1.3  | Transistor Modeling for Power Amplifier Design               | . 4  |

|      | 1.3.1 Proposed Type of Modeling                              | . 5  |

|      | 1.3.2 Challenges of Modeling Transistors of Wide-Bandgap     |      |

|      | Semiconductors                                               | . 7  |

|      | 1.3.3 Challenges of Modeling Advanced Large-Size Transistors |      |

|      | for High-Power Amplifiers                                    | . 7  |

| 1.4  | Main Objectives of the Research Work                         |      |

| 1.5  | Outline of the Thesis                                        | . 9  |

| Cha  | apter 2 GaN HEMTs for UMTS Power Amplifiers                  | 11   |

| 2.1  | GaN HEMTs Compared with Devices of Other Semiconductors      |      |

|      | for UMTS Power Amplifiers                                    | . 11 |

|      | 2.1.1 GaN Compared with GaAs, Si and SiC                     | . 11 |

|      | 2.1.2 GaN Compared with SiC                                  | . 12 |

|      | 2.1.3 GaN HEMTs Compared with LDMOS FETs of Si               | . 13 |

| 2.2  | Physical Structure and Operation of AlGaN/GaN HEMTs          | . 15 |

|      | 2.2.1 Basic Layer Structure and Band Diagram                 | . 15 |

|      | 2.2.2 Formation of the 2DEG                                  | . 16 |

|      | 2.2.3 Functional Description of Advanced Layer Structures    | . 18 |

| 2.3  |                                                              |      |

|      | 2.3.1 Charge-Trapping Induced Dispersion                     |      |

|      | 2.3.1.1 Definition of Dispersion and Attributed Effects      |      |

|      | 2.3.1.2 Trapping due to the Novelty of GaN Technology        |      |

|      | 2.3.1.3 Trapping due to the Nonnative Substrate              | . 25 |

|     | 2.3.2  | Parasitic Effects of GaN Devices                          | 25  |

|-----|--------|-----------------------------------------------------------|-----|

|     | 2.3.3  | Self-Heating Effects on GaN Devices                       | 26  |

| Cha | oter 3 | B Device Characterization for Modeling                    | 28  |

|     |        |                                                           |     |

| 3.1 |        | afacturers and Technology of the Studied Devices          |     |

| 3.2 |        | Acquisition for Modeling                                  |     |

|     | 3.2.1  | Static-DC IV Measurements                                 |     |

|     |        | 3.2.1.1 Description                                       |     |

|     |        | 3.2.1.2 Measurement Techniques and Setup                  |     |

|     |        | 3.2.1.3 Measured Results                                  |     |

|     | 3.2.2  | S-Parameter Measurements                                  |     |

|     |        | 3.2.2.1 Description                                       |     |

|     |        | 3.2.2.2 Measurement Techniques and Setup                  |     |

|     |        | 3.2.2.3 Measured Results                                  |     |

|     | 3.2.3  | Pulsed-DC Measurements                                    |     |

|     |        | 3.2.3.1 Description                                       |     |

|     |        | 3.2.3.2 Measurement Techniques and Setup                  |     |

|     |        | 3.2.3.3 Results on Passive <i>Quiescent</i> Bias Points   |     |

|     | _      | 3.2.3.4 Results of Active <i>Quiescent</i> Bias Points    |     |

| 3.3 | _      | e-Signal Characterization for Model Verification          |     |

|     |        | Description                                               |     |

|     | 3.3.2  | Measurement Setups                                        | 60  |

| Cha | pter 4 | Proposed Strategy for Small-Signal Modeling               | 62  |

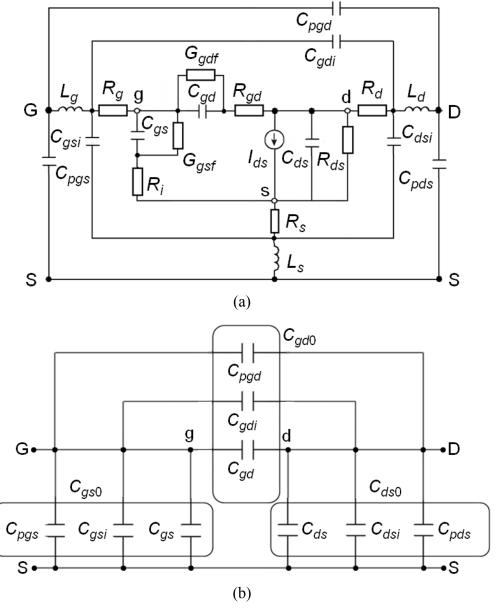

| 4.1 | Smal   | l-Signal Electrical Equivalent Circuit                    | 62  |

|     | 4.1.1  | Physical Meaning of the Circuit Elements                  | 63  |

|     | 4.1.2  | Physical Meaning of the Extrinsic Capacitance Parameters. | 65  |

| 4.2 |        | nsic Parameter Extraction                                 |     |

|     | 4.2.1  | Analysis of the Generation of Capacitance Ratio Values in |     |

|     |        | the TECR Algorithm                                        | 74  |

|     | 4.2.2  | Proposed Generation of Capacitance Ratio Values           | 89  |

|     | 4.2.3  | Equation System of Capacitance Parameters in Pinch-Off    | 95  |

|     |        | Sweeps of Values on Capacitance Parameters                |     |

|     |        | Extraction of Extrinsic Resistance Parameters             |     |

| 4.3 |        | sic Parameter Extraction                                  |     |

| 4.4 |        | bility of the Small-Signal Model                          |     |

|     | 441    | Scaling Rules in Terms of the Gate Electrode Width        | 118 |

|     | 4.4.2 Scaling Rules in Terms of the Gate Electrode Number           | 119 |

|-----|---------------------------------------------------------------------|-----|

| Cha | apter 5 Results of Small-Signal Modeling                            | 122 |

| 5.1 | Results of Extrinsic Parameter Extraction                           |     |

|     | 5.1.1 Optimal Frequency Range of the Extraction                     | 122 |

|     | 5.1.2 Starting and Optimized Values of the Extrinsic Parameters     | 124 |

| 5.2 | Results of Intrinsic Parameter Extraction                           |     |

|     | 5.2.1 Frequency and Bias Dependency of Intrinsic Parameters         |     |

|     | 5.2.2 Verification Tests with S-Parameters on Active Bias Points.   |     |

| 5.3 |                                                                     |     |

|     | 5.3.1 Extracted Parameter Values for Different Device Sizes         |     |

|     | 5.3.2 Scalability of Model Parameters in Terms of $w_{f_g}$         | 140 |

|     | 5.3.3 Scalability of Model Parameters in Terms of $n_{f_g}$         | 146 |

|     | 5.3.4 Tests of the Scaling Rules                                    |     |

|     | 5.3.4.1 Tests of Scalability for $w_f$ -Scaled Models               | 149 |

|     | 5.3.4.2 Tests of Scalability for <i>Quasi-Scaled Models</i>         |     |

|     | 5.3.4.3 Tests of Scalability for <i>Two-Step Scaled Models</i>      | 153 |

| Cha | apter 6 Proposed Strategy for Large-Signal Modeling                 | 156 |

| 6.1 | Large-Signal Modeling with Electrical Equivalent Circuits           | 156 |

| 6.2 | Non-Quasi-Static Charge Modeling                                    | 157 |

|     | 6.2.1 Large-Signal Charge Sources                                   | 159 |

|     | 6.2.2 Large-Signal Current Sources of the Gate Diodes               | 167 |

| 6.3 | Modeling of <i>I</i> <sub>ds</sub>                                  | 169 |

|     | 6.3.1 Definitions and Assumptions of the Adopted $I_{ds}$ Model     | 170 |

|     | 6.3.2 Electro-Thermal Modeling                                      | 173 |

| 6.4 | Measurement-Based Extraction of $I_{ds}$ -Model Parameters          | 175 |

|     | 6.4.1 Extraction of the Parameters $I_{ds}^{Iso}$ , $f_G$ and $f_D$ | 175 |

|     | 6.4.2 Extraction of the Parameters $f_{th}$ and $f_P$               | 177 |

|     | 6.4.3 Extraction of Trapping and Thermal Time Constants             | 181 |

| Cha | apter 7 Large-Signal Modeling Verification                          | 188 |

| 7.1 | Large-Signal Model Implementation                                   | 188 |

| 7.2 | Tests of Large-Signal Model Verification                            | 190 |

|     | 7.2.1 Verification Tests with S-Parameters                          | 191 |

|     | 7.2.2 Pulsed-DC IV Verification Tests                               | 193 |

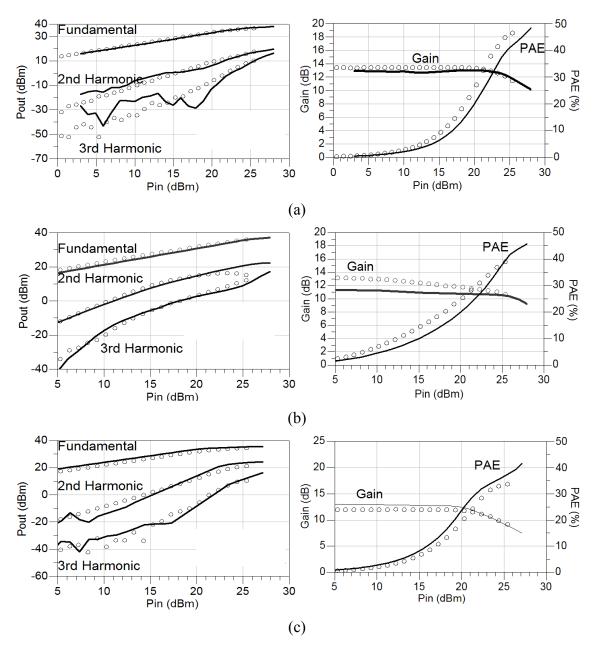

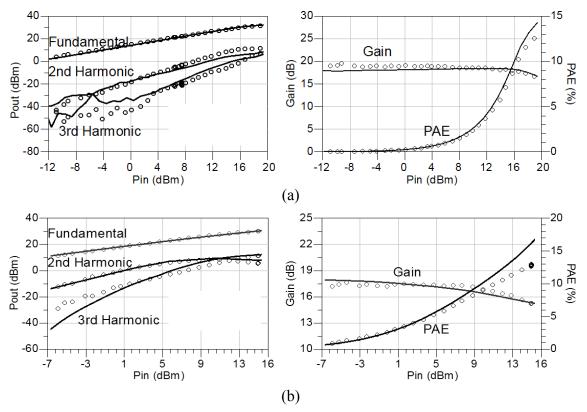

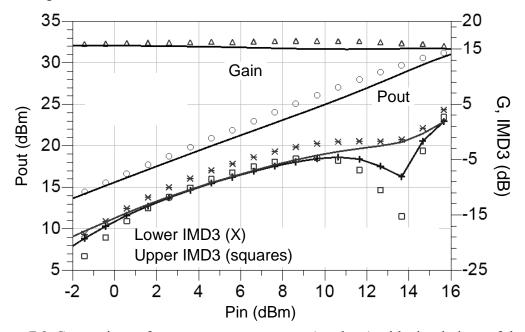

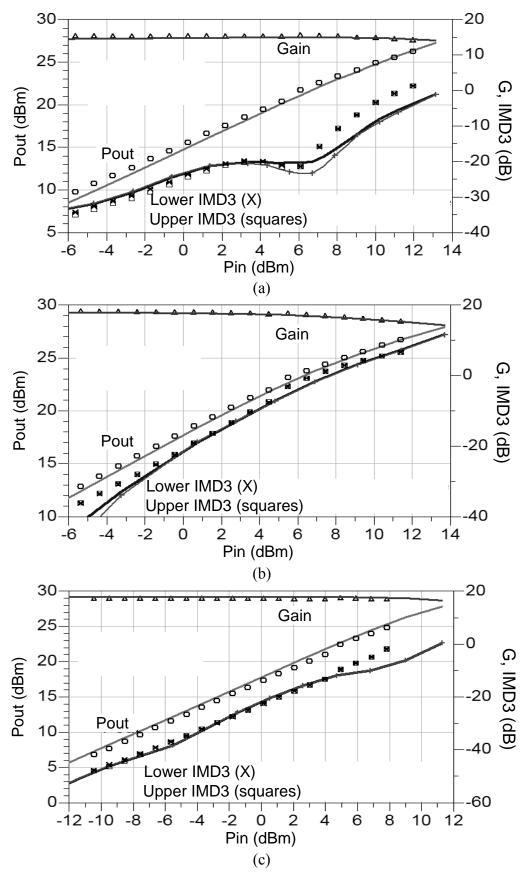

|     | 7.2.3 Verification Tests with Single-Tone and Two-T | one Stimuli. 195 |

|-----|-----------------------------------------------------|------------------|

| Cha | apter 8 Conclusions and Future Work                 | 203              |

| 8.1 | Conclusions from the Research Results               | 203              |

| 8.2 | Outlook of Future Work                              | 208              |

| Ref | erences                                             | 210              |

# List of Figures

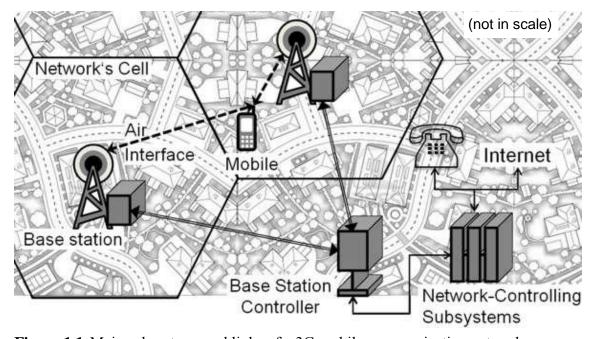

| Figure 1.1 | Main subsystems and links of a 3G mobile communication network                                                                                                                                                                                                                                                                                | . 1  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

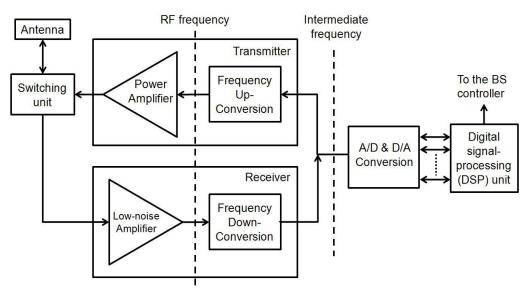

| Figure 1.2 | Block diagram of a conventional UMTS base station.                                                                                                                                                                                                                                                                                            | . 2  |

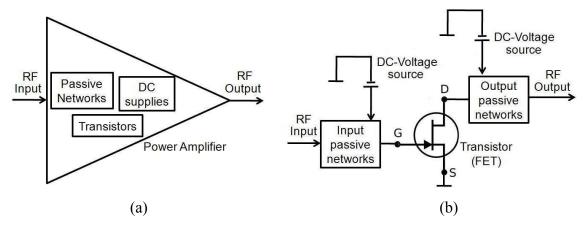

| Figure 1.3 | (a) Elements of the power amplifier (b) and basic configuration                                                                                                                                                                                                                                                                               | . 3  |

| Figure 2.1 | Illustration of record power densities versus operation frequency based on diverse published results of GaN HEMTs [24-28] and Si LDMOS FETs [22, 29, 30].                                                                                                                                                                                     | . 14 |

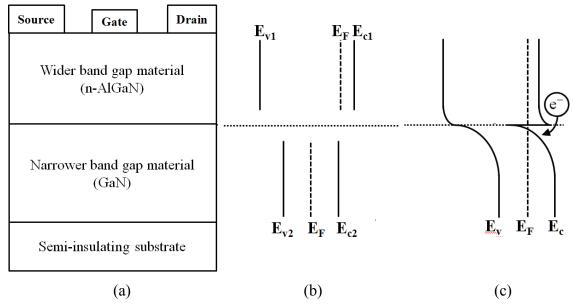

| Figure 2.2 | (a) Basic AlGaN/GaN HEMT layer structure, (b) band diagram of the heterojunction before the equilibrium condition and (c) afterwards.                                                                                                                                                                                                         | . 16 |

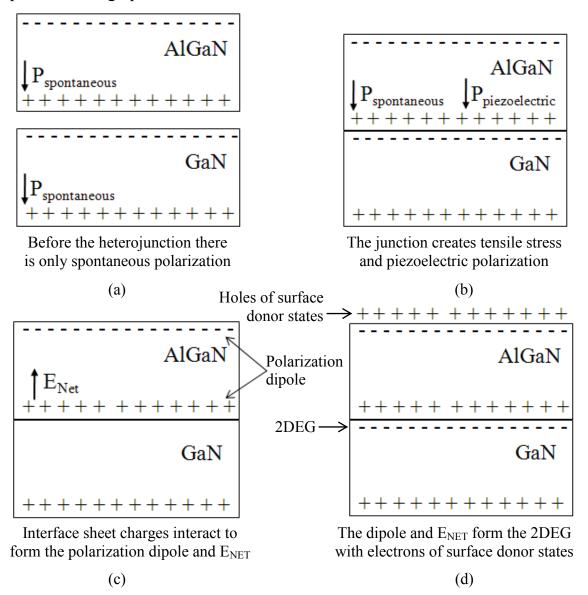

|            | Illustration of 2DEG formation on GaN HEMTs redrawn from [35]: In (a) the heterojunction does not exist yet, in (b) the heterojunction is created and tensile stress occurs, in (c) the polarization dipole appears, and in (d) the 2DEG is formed.                                                                                           | . 18 |

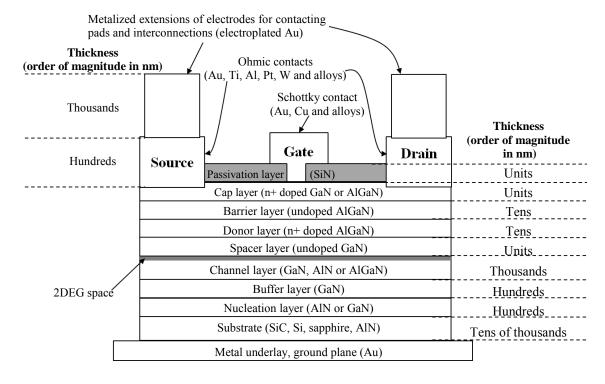

| Figure 2.4 | Layer structure with detail of different layers that are commonly found in advanced AlGaN/GaN HEMTs to improve performance [17, 19, 26, 33, 35-38]                                                                                                                                                                                            | . 19 |

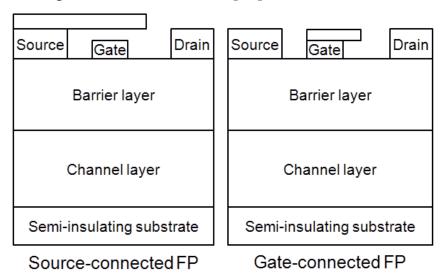

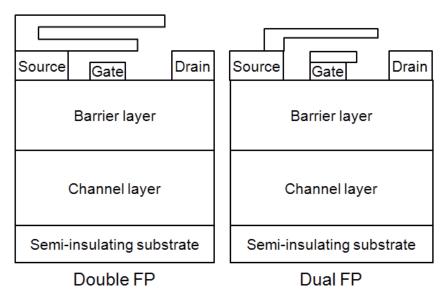

| Figure 2.5 | Different variants of field plates of modern GaN HEMTs, redrawn from [42].                                                                                                                                                                                                                                                                    | . 21 |

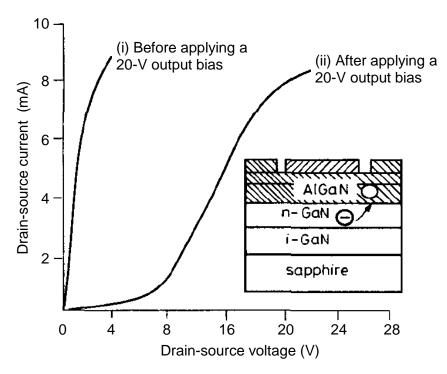

| Figure 2.6 | Illustration of the current-collapse effect induced by charge trapping. Inset: Suggested location of the traps in the layer structure [44]                                                                                                                                                                                                    | . 23 |

| Figure 3.1 | Layer structure schematic of the studied Nitronex® device, taken from [51]                                                                                                                                                                                                                                                                    | . 29 |

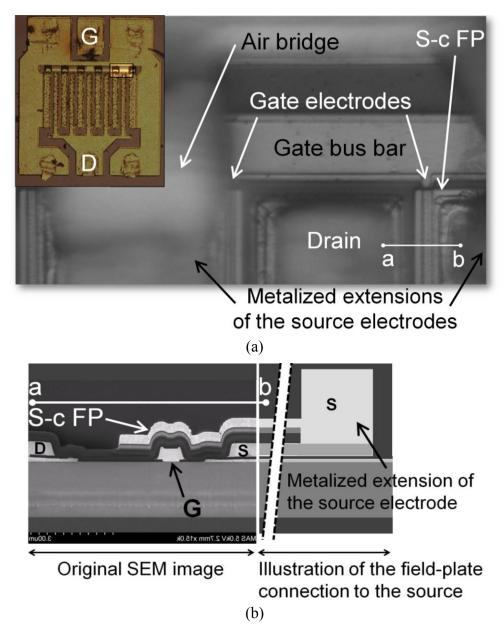

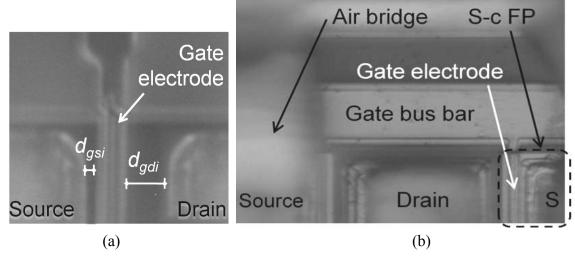

| Figure 3.2 | Images of the studied 2-mm device highlighting the source-connected field plates along the segment a-b: (a) Top-view micrograph made for this work with an inset to point out the location of the image in the finger layout. (b) Side-view SEM image taken from [51] with an added diagram to show the field-plate connection to the source. | . 30 |

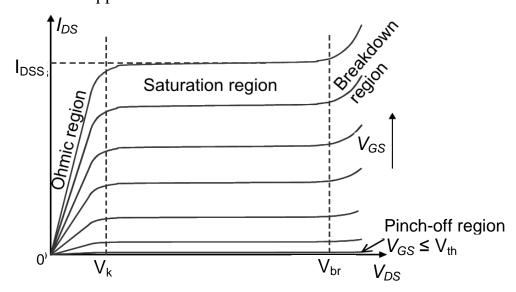

| Figure 3.3 | Regions and relevant values of an ideal static-DC IV output characteristic.                                                                                                                                                                                                                                                                   |      |

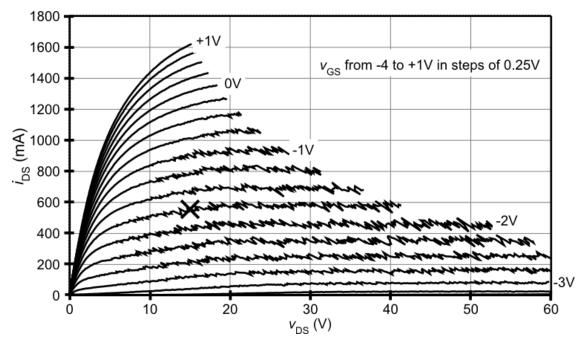

| Figure 3.4 |                                                                                                                                                                                                                                                                                                                                               |      |

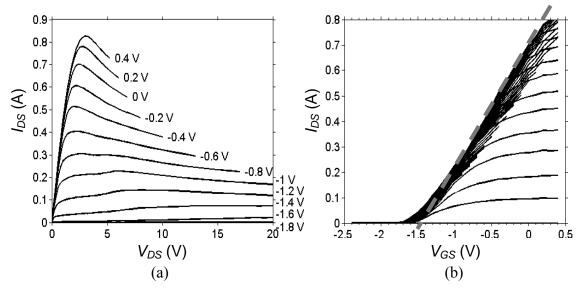

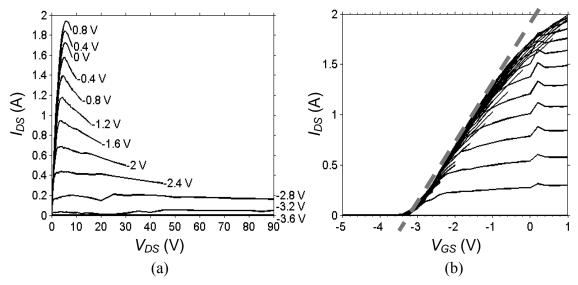

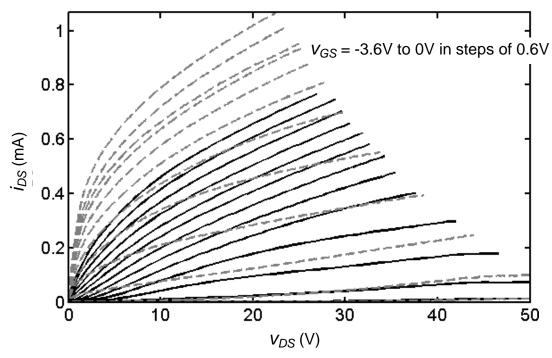

| Figure 3.5 | Static-DC IV (a) output and (b) transfer characteristics of the 3.2-mm device. In (b) the graphical estimation of $V_{th}$ =-3.3V is sketched (thick dashed line).                                                                                                                                                                            | . 34 |

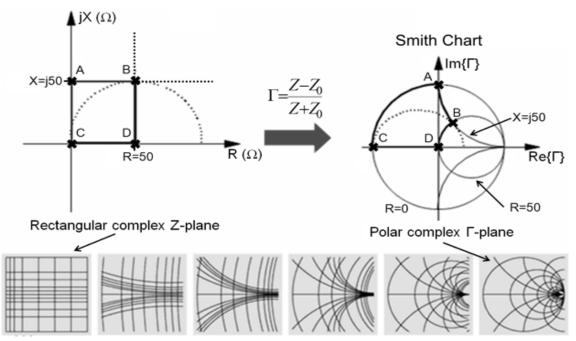

| Figure 3.6 | Illustration of the Smith Chart and plane transformation, redrawn from [55].                                                                                                                                                                                                                                                                  | . 36 |

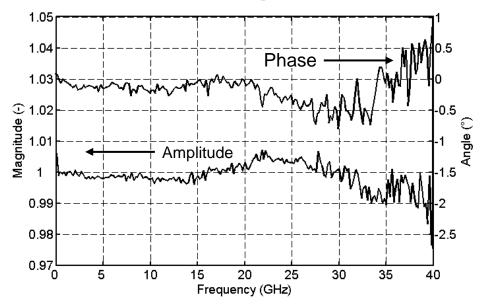

| Figure 3.7 | Measured reflection coefficient of an off-set open employed for verification of the VNA on-wafer calibration (including phase compensation for the offset length)                                                                                                                                                                             | . 38 |

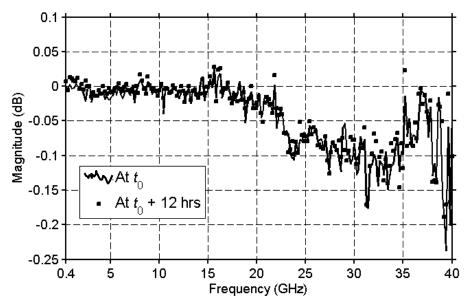

| Figure 3.8  | Measured reflection coefficient of an off-set open before and after a                                   |    |

|-------------|---------------------------------------------------------------------------------------------------------|----|

|             | 12-hour measurement session, indicating similar verification results                                    |    |

|             | of the on-wafer VNA calibration, and thus absence of short-term                                         |    |

|             | drift                                                                                                   | 38 |

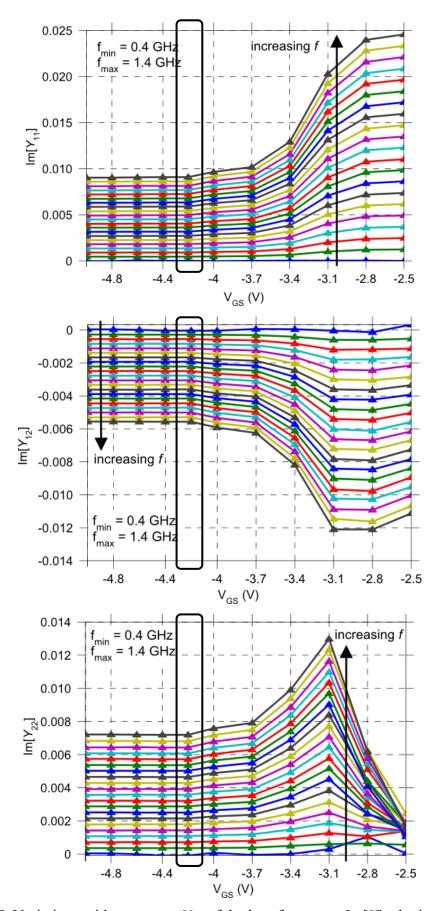

| Figure 3.9  | Variations with respect to $V_{GS}$ of the low-frequency Im[Y], obtained                                |    |

|             | from S-parameters measured around $V_{th}$ , for the selection of $V_{pinch}$                           |    |

|             | off for the <i>cold pinch-off</i> condition of the 3.2-mm device.                                       | 40 |

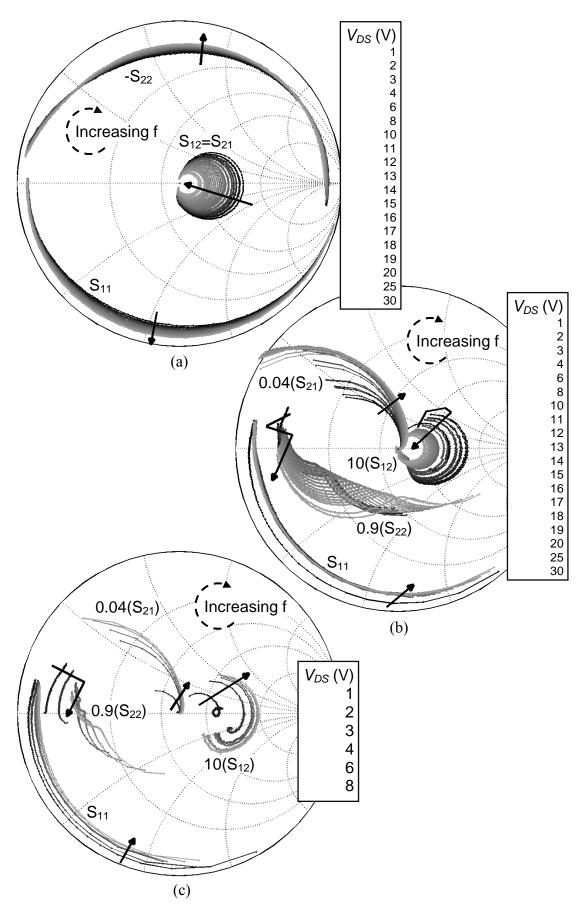

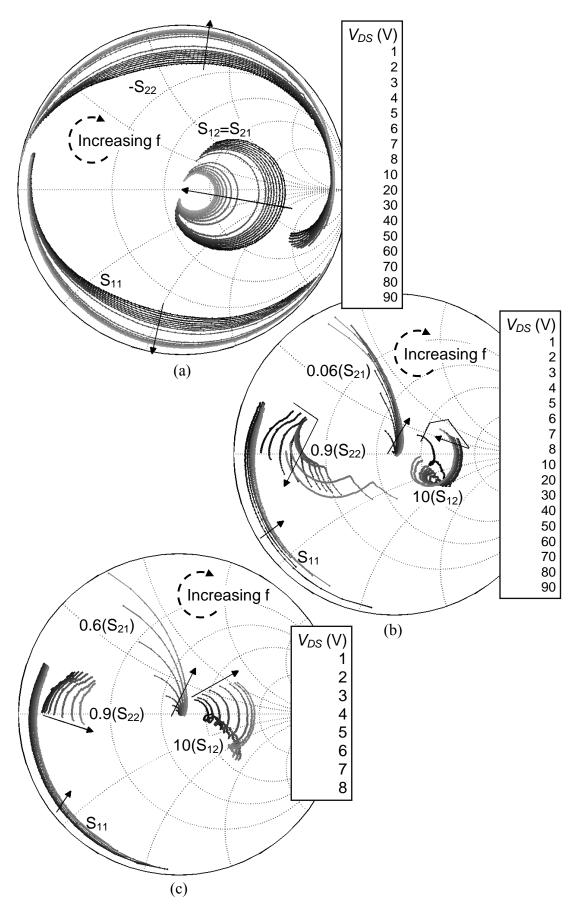

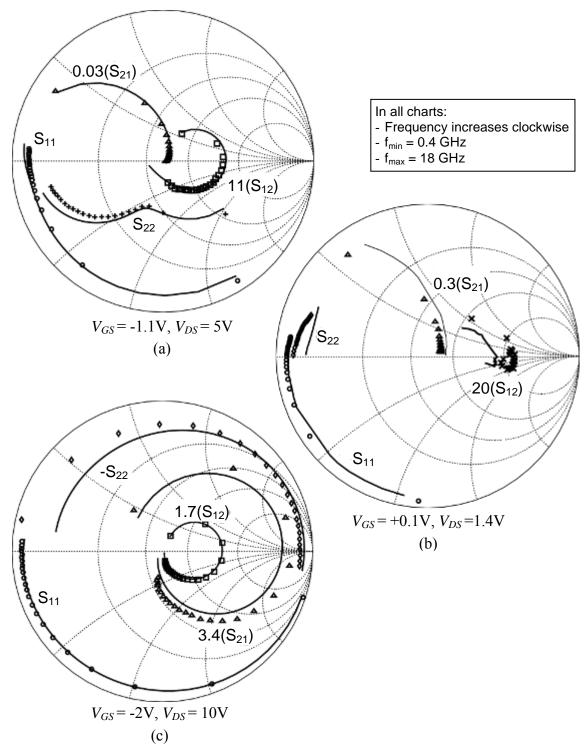

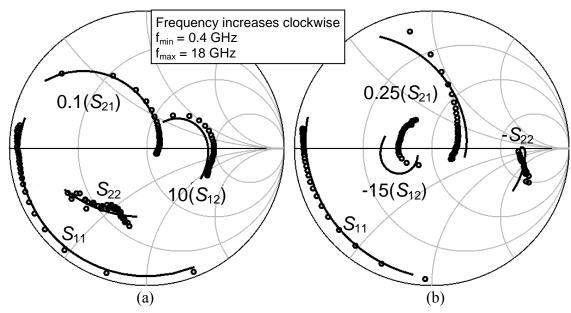

| Figure 3.10 | Example S-parameters of the 3.2-mm device measured on 200                                               |    |

|             | frequency points from 0.4 to 18 GHz on active bias points with: (a)                                     |    |

|             | $V_{GS} = V_{\text{pinch-off}}$ , (b) $0V > V_{GS} > V_{\text{pinch-off}}$ and (c) $V_{GS} = 0V$ (solid |    |

|             | arrows indicate variations with increasing $V_{DS}$ )                                                   | 42 |

| Figure 3.11 | Example S-parameters of the 3.2-mm device measured on 197                                               |    |

|             | frequency points from 0.4 to 18 GHz on active bias points with: (a)                                     |    |

|             | $V_{GS} = V_{\text{pinch-off}}$ , (b) $0V > V_{GS} > V_{\text{pinch-off}}$ and (c) $V_{GS} = 0V$ (solid |    |

|             | arrows indicate variations with increasing $V_{DS}$ )                                                   | 43 |

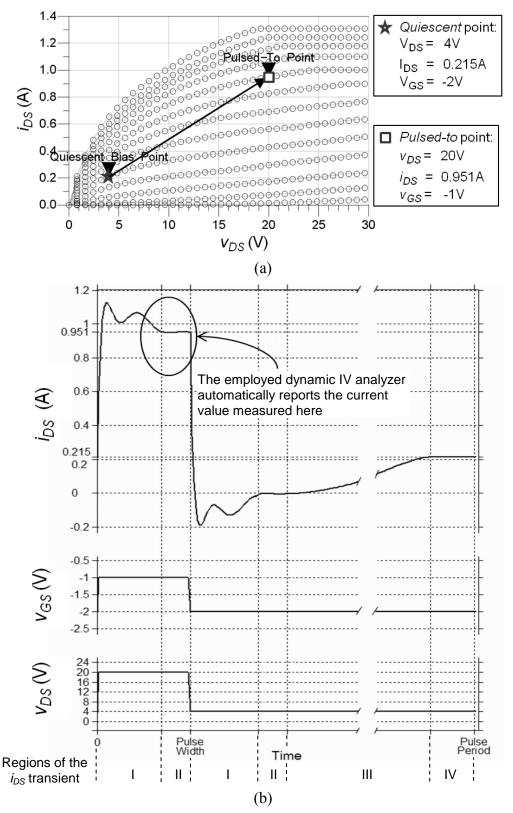

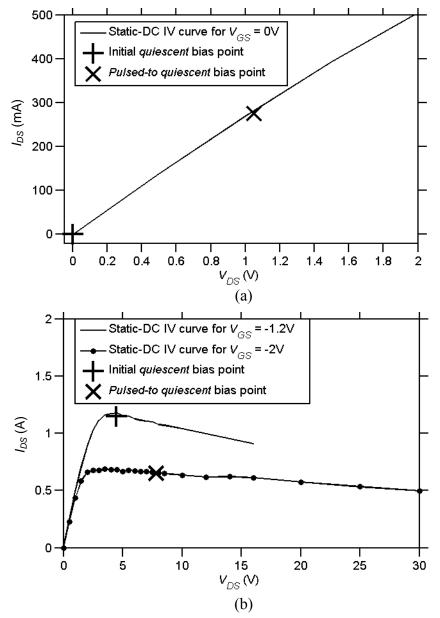

| Figure 3.12 | (a) Example of pulsed-DC IV characteristics (circles) from a                                            |    |

|             | quiescent bias point (star), highlighting an example pulsed-to point                                    |    |

|             | (square). (b) Applied voltage pulses and measured current transient                                     |    |

|             | that are illustrated in (a) by an arrow between the quiescent bias and                                  |    |

|             | an example <i>pulsed-to</i> point, hinting the regions of the $i_{DS}$ transient                        | 45 |

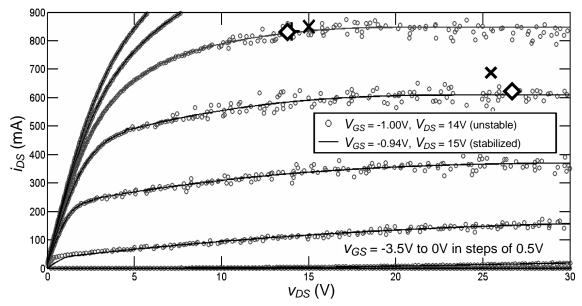

| Figure 3.13 | Unstable pulsed-DC IV measurements of the 3.2-mm device on the                                          |    |

|             | quiescent bias point (X-marker) $V_{GS} = -1.75 \text{V}$ , $V_{DS} = 15 \text{V}$ , $I_{DS} \approx$   |    |

|             | , D <sub>0</sub>                                                                                        | 47 |

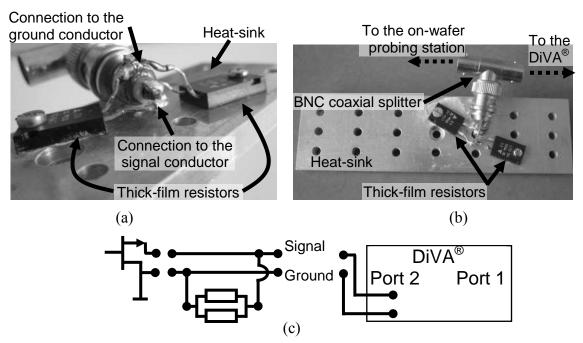

| Figure 3.14 | (a) Side-view and (b) top-view photographs of the stabilizing                                           |    |

|             | element and (c) equivalent circuit of the implementation of the                                         |    |

|             | stabilization technique.                                                                                | 48 |

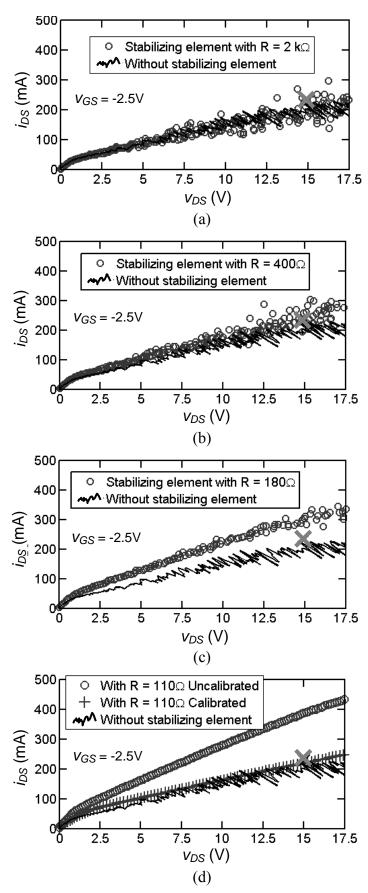

| Figure 3.15 | Pulsed-DC IV tests using the 3.2-mm IAF device and stabilizing                                          |    |

|             | elements with different resistance values: (a) 2 k $\Omega$ , (b) 400 $\Omega$ , (c)                    |    |

|             | $180\Omega$ and (d) $110\Omega$ . Common <i>quiescent</i> bias point (X markers) with                   |    |

|             | $V_{GS}$ = -2.5V, $V_{DS}$ = 15V, $I_{DS} \approx 0.24$ A, $P_{DS} \approx 3.6$ W                       | 49 |

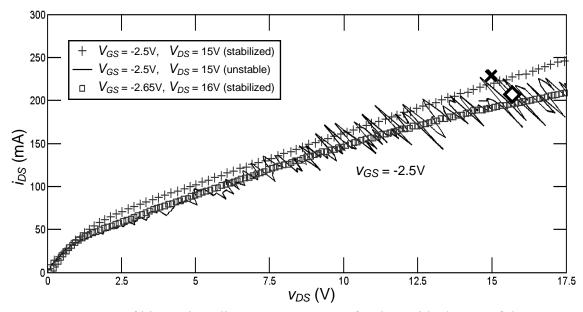

| Figure 3.16 | Test of bias-point adjustment to account for the residual error of the                                  |    |

|             | stabilizing element, showing unstable (solid line) and stable (crosses                                  |    |

|             | and squares) pulsed-DC IV measurements on a quiescent bias point                                        |    |

|             | (X marker) and stable measurements equivalent to the unstable trace                                     |    |

|             | with the bias point adjusted (diamond).                                                                 | 51 |

| Figure 3.17 | Further test of bias-point adjustment to account for the residual error                                 |    |

|             | of the stabilizing element, showing unstable pulsed-DC IV                                               |    |

|             | measurements (circles) on a quiescent bias point (X marker) and                                         |    |

|             | stable measurements that are equivalent (solid lines) on an adjusted                                    |    |

|             | quiescent bias point (diamond).                                                                         | 51 |

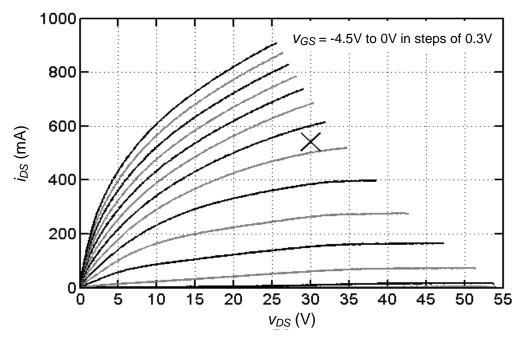

| Figure 3.18 | Pulsed-DC IV measurement obtained with the stabilization                                                |    |

|             | technique, otherwise unfeasible due to the high $P_{DS}$ of nearly 16W                                  |    |

|             | and the <i>quiescent</i> bias point location (X marker), which was $V_{GS} = -$                         |    |

|             | $2V, V_{DS} = 30V, I_{DS} \approx 0.54A.$                                                               | 52 |

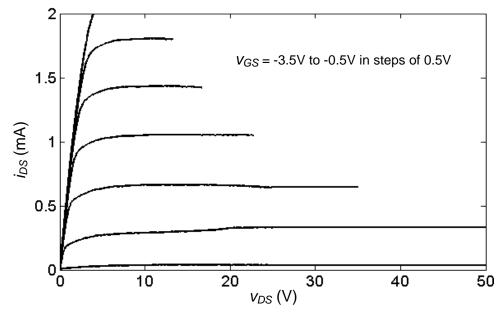

| Figure 3.19        | Results of pulsed-DC IV measurements on $V_{GS} = 0$ V and $V_{DS} = 0$ V                                      |      |

|--------------------|----------------------------------------------------------------------------------------------------------------|------|

|                    | of the 3.2-mm device.                                                                                          | . 53 |

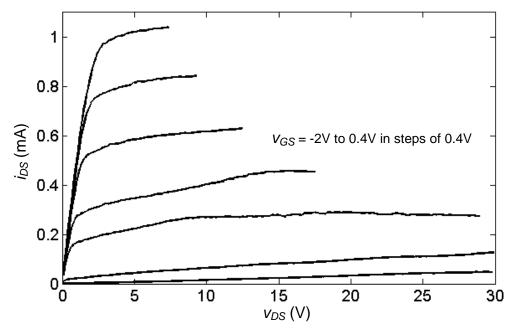

| <b>Figure 3.20</b> | Results of pulsed-DC IV measurements on $V_{GS} = 0$ V and $V_{DS} = 0$ V                                      |      |

|                    | of the 2-mm device                                                                                             | . 54 |

| <b>Figure 3.21</b> | Results of pulsed-DC IV measurements for the 3.2-mm device on                                                  |      |

|                    | passive quiescent bias points ( $I_{DS} = 0$ A and $P_{DS} = 0$ W) with $V_{GS} = -$                           |      |

|                    | 6V and $V_{DS} = 0$ V (solid line), and with the same $V_{GS}$ and $V_{DS} = 54$ V                             |      |

|                    | (dashed line).                                                                                                 | . 55 |

| Figure 3.22        | Results of pulsed-DC IV measurements for the 2-mm device on                                                    |      |

|                    | passive quiescent bias points ( $I_{DS} = 0$ A and $P_{DS} = 0$ W) with $V_{GS} = -$                           |      |

|                    | 4V and $V_{DS} = 0$ V (solid line), and with the same $V_{GS}$ and $V_{DS} = 30$ V                             |      |

|                    | (dashed line).                                                                                                 | . 55 |

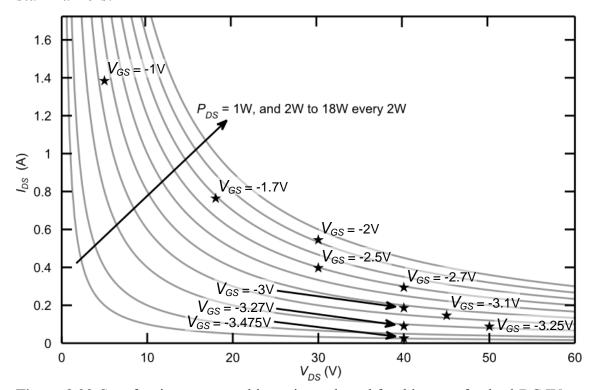

| Figure 3.23        | Set of active quiescent bias points selected for this part of pulsed-                                          |      |

|                    | DC IV characterization of the 3.2-mm device (star markers)                                                     | . 56 |

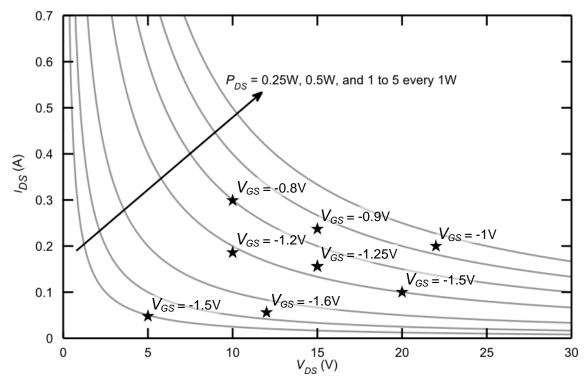

| Figure 3.24        | Set of active quiescent bias points selected for this part of pulsed-                                          |      |

|                    | DC IV characterization of the 2-mm device(star markers)                                                        | . 57 |

| <b>Figure 3.25</b> | Pulsed-DC IV characteristics of the 3.2-mm device measured on the                                              |      |

|                    | active quiescent bias points $V_{GS} = -3.475 \text{V}$ , $V_{DS} = 40 \text{V}$ , $P_{DS} \approx 1 \text{W}$ |      |

|                    | (solid line), and $V_{GS} = -2.7 \text{V}$ , $V_{DS} = 40 \text{V}$ and $P_{DS} \approx 12 \text{W}$ (dashed   |      |

|                    | line).                                                                                                         | . 58 |

| <b>Figure 3.26</b> | Pulsed-DC IV characteristics of the 2-mm device measured on the                                                |      |

|                    | active quiescent bias points $V_{GS} = -0.9 \text{V}$ , $V_{DS} = 15 \text{V}$ , $P_{DS} \approx 2 \text{W}$   |      |

|                    | (solid line), and $V_{GS} = -1.25 \text{V}$ , $V_{DS} = 15 \text{V}$ and $P_{DS} \approx 4 \text{W}$ (dashed   |      |

|                    | line).                                                                                                         | . 58 |

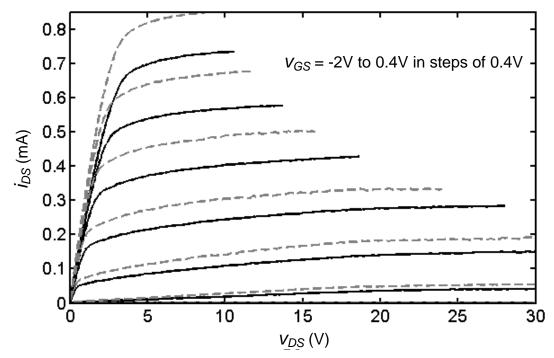

| <b>Figure 3.27</b> | Large-signal multi-harmonic load-pull measurement setup proposed                                               |      |

|                    | by Wittwer et al. [72] applied for the single-tone and two-tone                                                |      |

|                    | device characterization used for model verification.                                                           | . 61 |

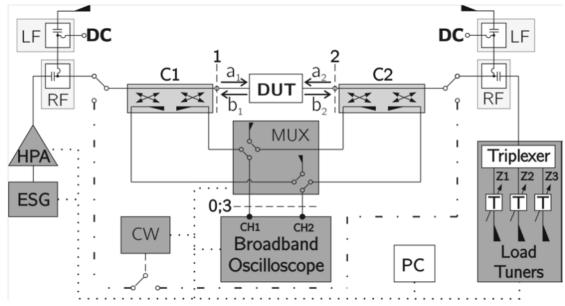

| <b>Figure 3.28</b> | Large-signal frequency-domain measurement setup for distortion                                                 |      |

|                    | and envelope load-pull characterization proposed by Srinidhi et al.                                            |      |

|                    | [71] applied for the two-tone device characterization used for model                                           |      |

|                    | verification.                                                                                                  | . 61 |

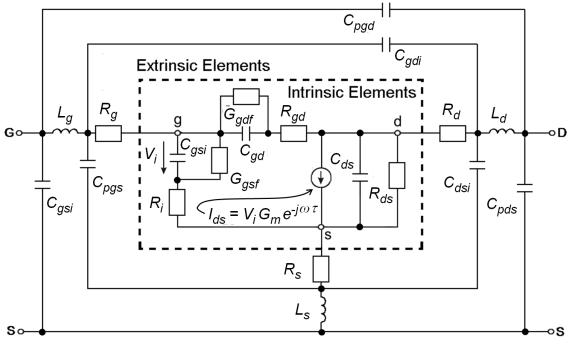

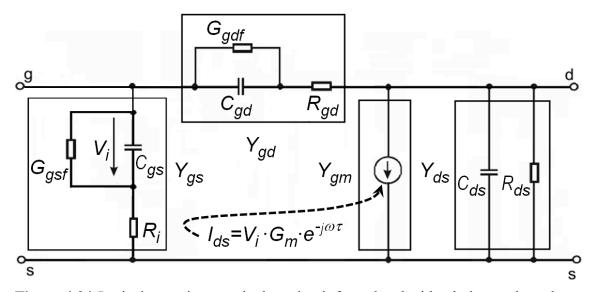

| Figure 4.1         | Small-signal electric equivalent circuit for GaN HEMTs used in this                                            |      |

|                    | thesis                                                                                                         | . 63 |

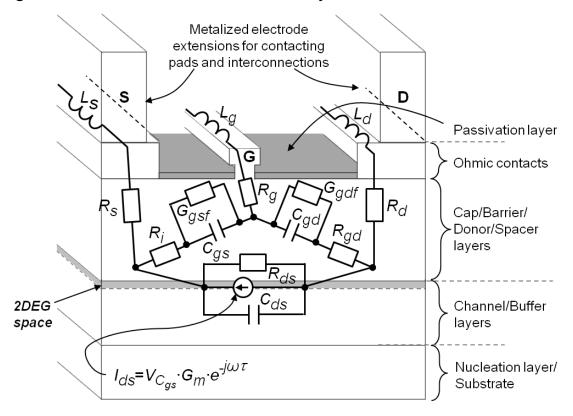

| Figure 4.2         | Illustration of the physical meaning of the electric equivalent circuit                                        |      |

|                    | used for the small-signal model of GaN HEMTs (except extrinsic                                                 |      |

|                    | capacitive effects)                                                                                            | . 64 |

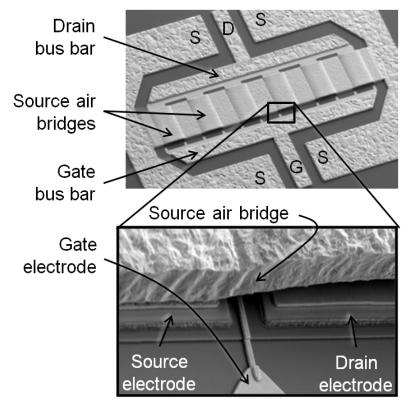

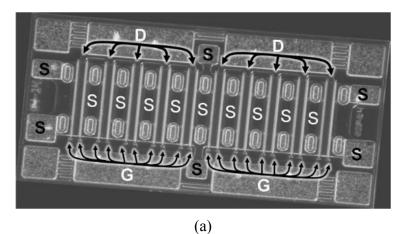

| Figure 4.3         | Photographs of a device shown in [82], highlighting air bridges and                                            |      |

|                    | bus bars in transistor layouts with more than two gate electrodes                                              |      |

|                    | (fingers).                                                                                                     |      |

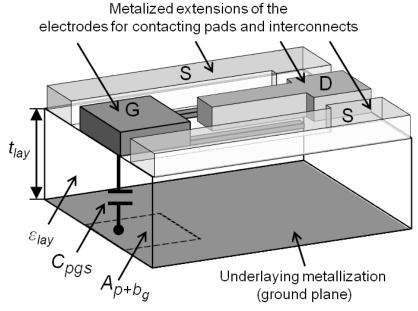

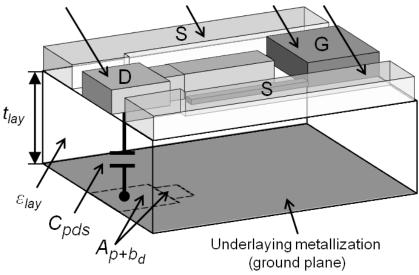

|                    | Illustration of the physical meaning of $C_{pgs}$ .                                                            |      |

|                    | Illustration of the physical meaning of $C_{pds}$ .                                                            |      |

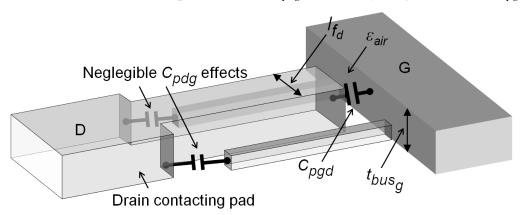

|                    | Illustration of the physical meaning of $C_{pgd}$ .                                                            |      |

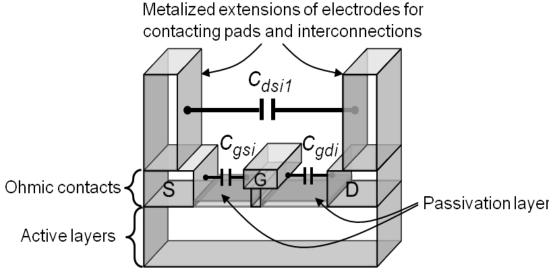

|                    | Illustration of the physical meaning of $C_{gsi}$ , $C_{gdi}$ and $C_{dsi1}$                                   |      |

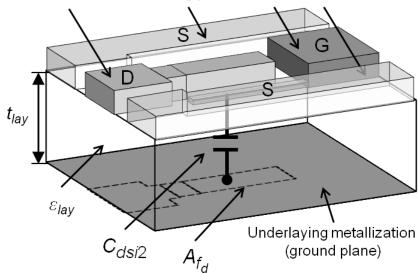

| Figure 4.8         | Illustration of the physical meaning of $C_{dsi2}$ .                                                           | .71  |

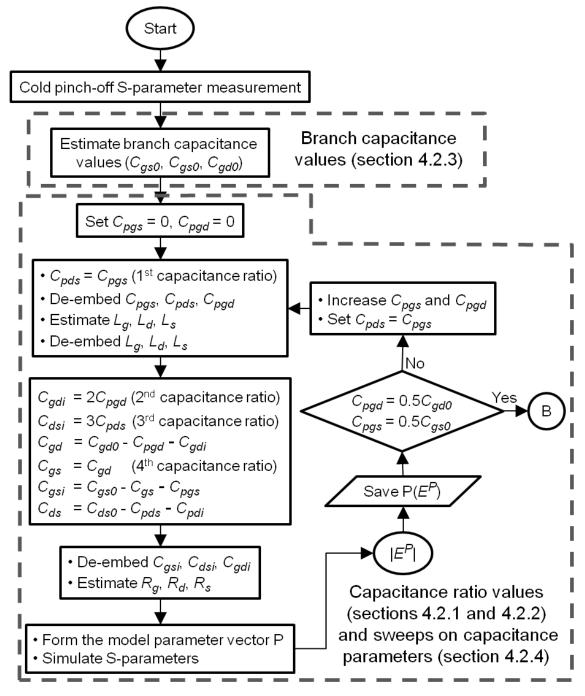

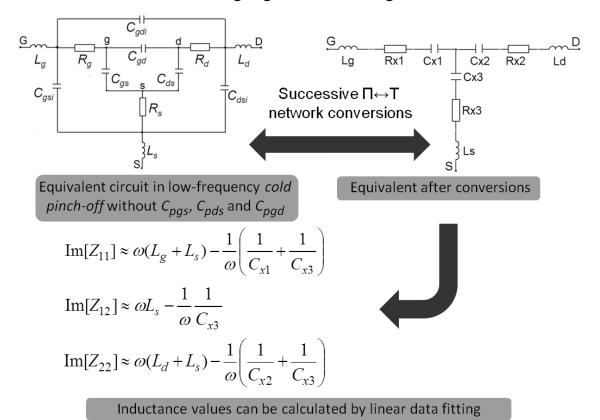

| Figure 4.9  | Flowchart of phase 1 of the TECR algorithm, redrawn from [74], indicating the sections of this thesis where each key aspect is treated |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|----|

|             | (continues)                                                                                                                            | 73 |

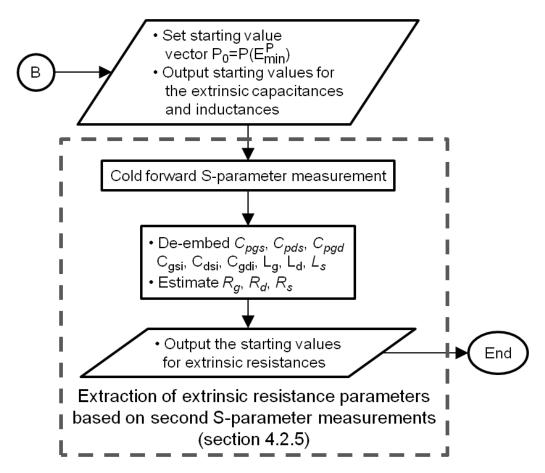

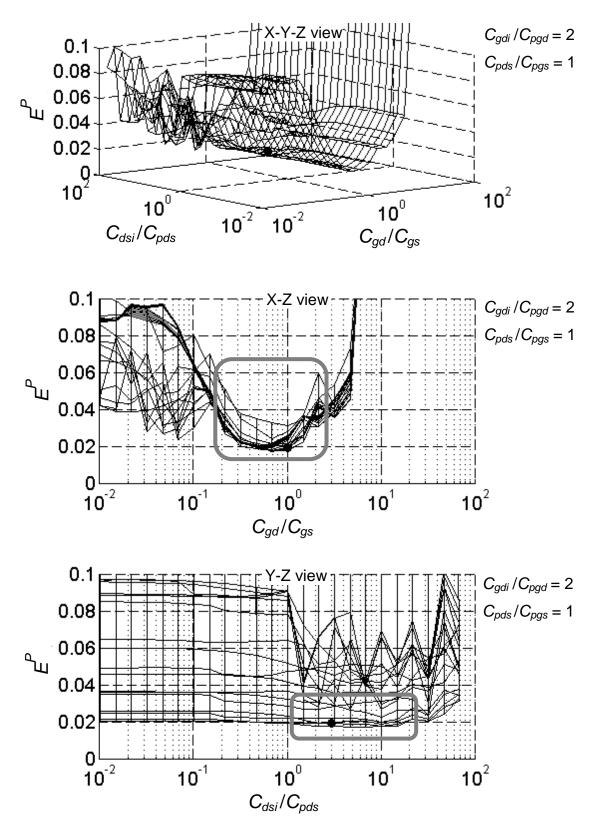

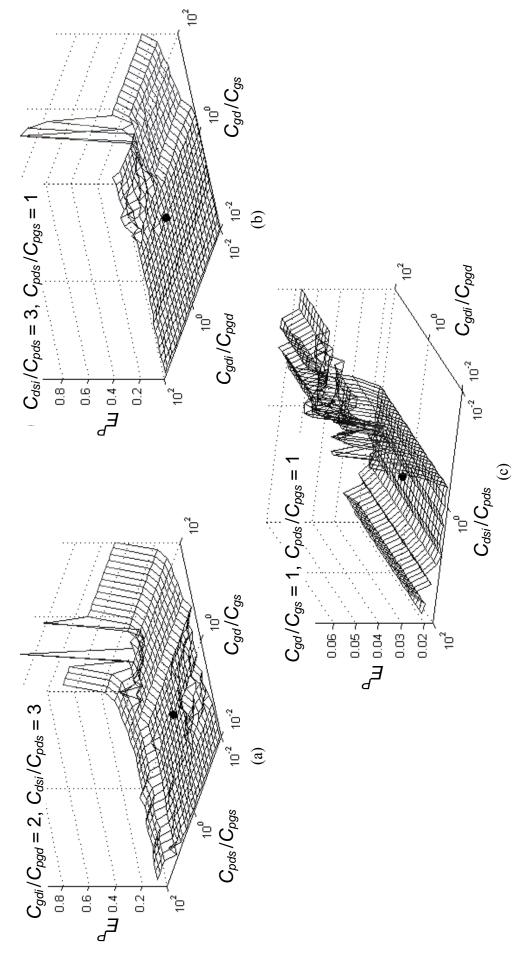

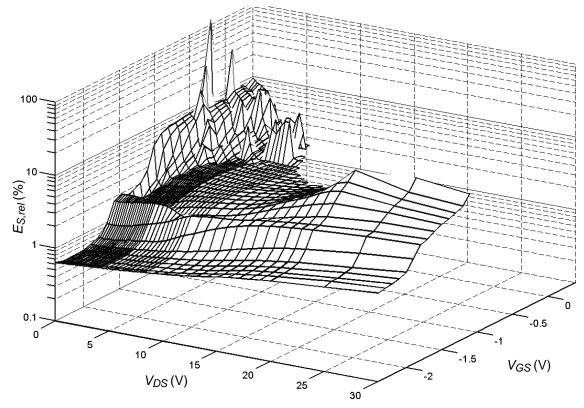

| Figure 4.10 | Scanning results of task 1 of the heuristical analysis made to                                                                         | 13 |

| 800 11-0    | capacitance ratio values of the TECR algorithm. $C_{gs}/C_{gd}$ and                                                                    |    |

|             | $C_{pds}/C_{pgs}$ are fixed in the values proposed in [74]. The scans on                                                               |    |

|             | $C_{gdi}/C_{pgd}$ and $C_{dsi}/C_{pds}$ are mapped as the X- and Y-axes and the Z-                                                     |    |

|             | axis corresponds to the $E^{P}$ values obtained of applying the TECR                                                                   |    |

|             | algorithm with the capacitance ratio values of each scan step. The                                                                     |    |

|             | highlighted black dots indicate the $C_{gdi}/C_{pgd}$ and $C_{dsi}/C_{pds}$ values                                                     |    |

|             | assumed in [74].                                                                                                                       | 77 |

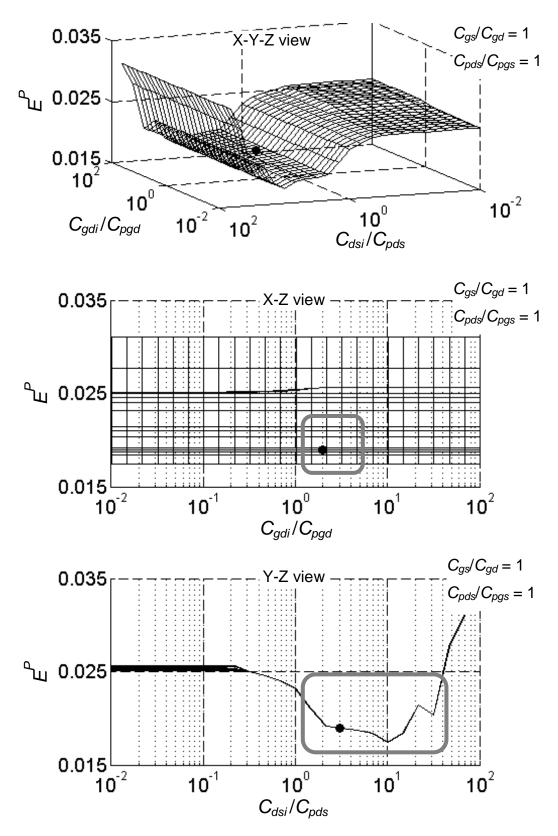

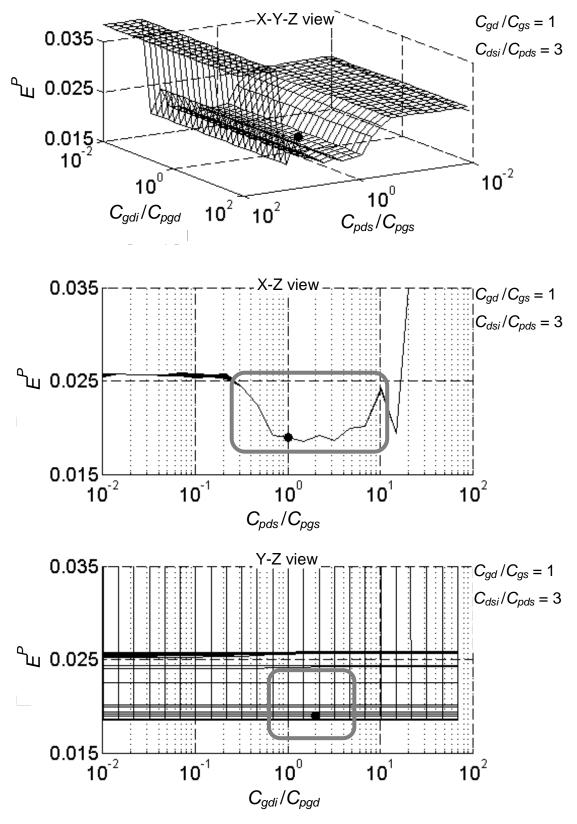

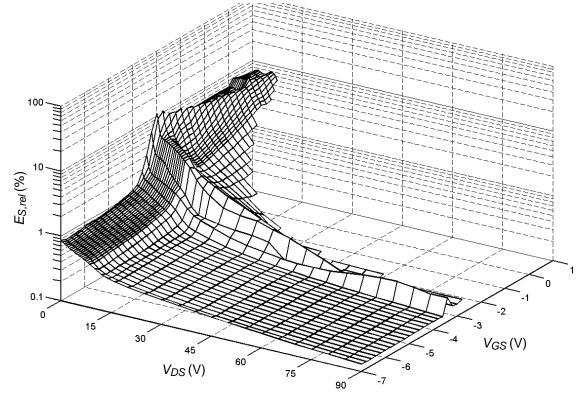

| Figure 4.11 | Scanning results of task 2 of the heuristical analysis made to                                                                         |    |

| C           | capacitance ratio values of the TECR algorithm. $C_{gs}/C_{gd}$ and                                                                    |    |

|             | $C_{gdi}/C_{pgd}$ are fixed in the values proposed in [74]. The scans on                                                               |    |

|             | $C_{pds}/C_{pgs}$ and $C_{dsi}/C_{pds}$ are mapped as the X- and Y-axes and the Z-                                                     |    |

|             | axis corresponds to the $E^{P}$ values obtained of applying the TECR                                                                   |    |

|             | algorithm with the capacitance ratio values of each scan step. The                                                                     |    |

|             | highlighted black dots indicate the $C_{pds}/C_{pgs}$ and $C_{dsi}/C_{pds}$ values                                                     |    |

|             | assumed in [74].                                                                                                                       | 78 |

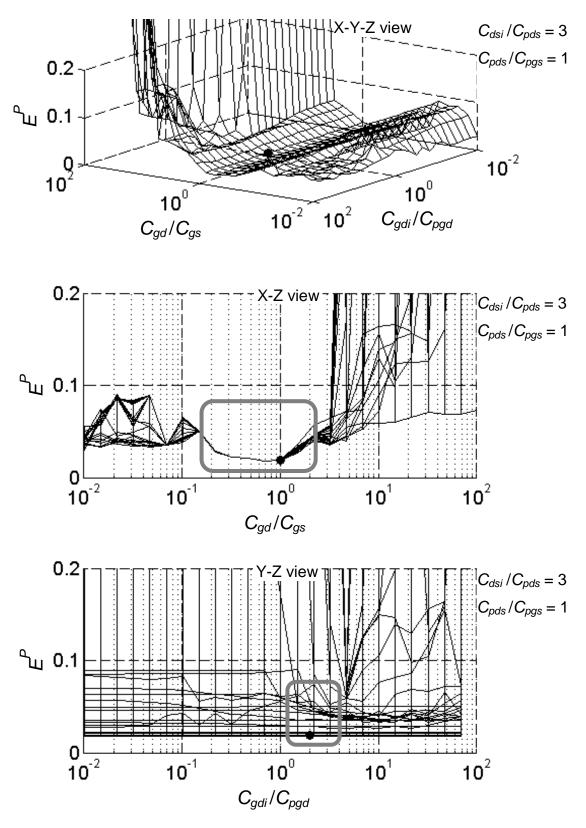

| Figure 4.12 | Scanning results of task 3 of the heuristical analysis made to                                                                         |    |

|             | capacitance ratio values of the TECR algorithm. $C_{gdi}/C_{pgd}$ and                                                                  |    |

|             | $C_{pds}/C_{pgs}$ are fixed in the values proposed in [74]. The scans on                                                               |    |

|             | $C_{gs}/C_{gd}$ and $C_{dsi}/C_{pds}$ are mapped as the X- and Y-axes and the Z-                                                       |    |

|             | axis corresponds to the $E^{P}$ values obtained of applying the TECR                                                                   |    |

|             | algorithm with the capacitance ratio values of each scan step. The                                                                     |    |

|             | highlighted black dots indicate the $C_{gdi}/C_{pgd}$ and $C_{pds}/C_{pgs}$ values                                                     | 70 |

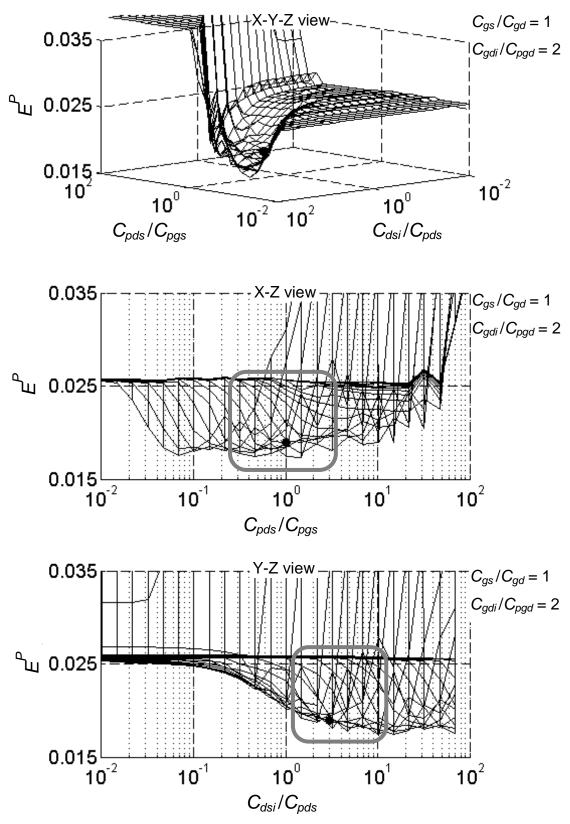

| Figure 4.12 | assumed in [74]                                                                                                                        | 19 |

| rigure 4.13 | capacitance ratio values of the TECR algorithm. $C_{gs}/C_{gd}$ and                                                                    |    |

|             | $C_{dsi}/C_{pds}$ are fixed in the values proposed in [74]. The scans on                                                               |    |

|             | $C_{pds}/C_{pgs}$ and $C_{gdi}/C_{pgd}$ are mapped as the X- and Y-axes and the Z-                                                     |    |

|             | axis corresponds to the $E^{P}$ values obtained of applying the TECR                                                                   |    |

|             | algorithm with the capacitance ratio values of each scan step. The                                                                     |    |

|             | highlighted black dots indicate the $C_{gs}/C_{gd}$ and $C_{dsi}/C_{pds}$ values                                                       |    |

|             | assumed in [74].                                                                                                                       | 80 |

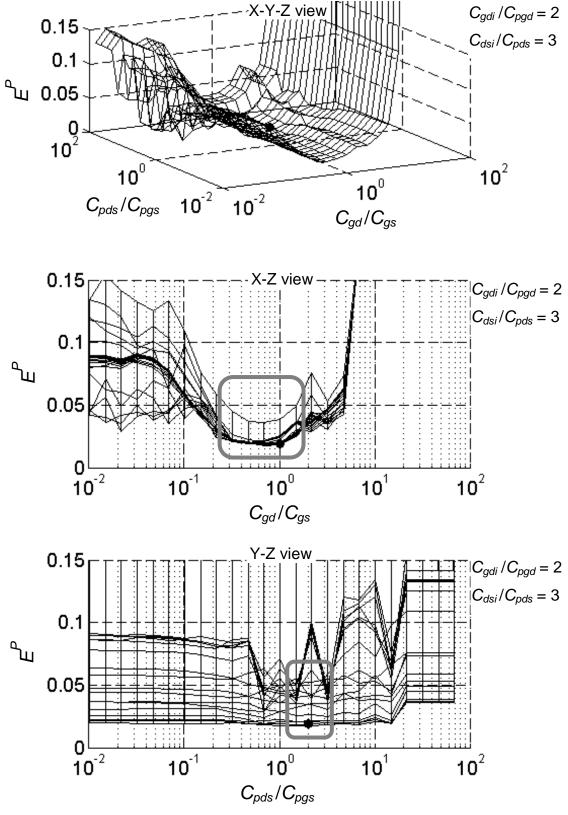

| Figure 4.14 | Scanning results of task 5 of the heuristical analysis made to                                                                         |    |

|             | capacitance ratio values of the TECR algorithm. $C_{dsi}/C_{pds}$ and                                                                  |    |

|             | $C_{pds}/C_{pgs}$ are fixed in the values proposed in [74]. The scans on                                                               |    |

|             | $C_{gs}/C_{gd}$ and $C_{gdi}/C_{pgd}$ are mapped as the X- and Y-axes and the Z-                                                       |    |

|             | axis corresponds to the $E^{P}$ values obtained of applying the TECR                                                                   |    |

|             | algorithm with the capacitance ratio values of each scan step. The                                                                     |    |

|             | highlighted black dots indicate the $C_{dsi}/C_{pds}$ and $C_{pds}/C_{pgs}$ values                                                     |    |

|             | assumed in [74].                                                                                                                       | 81 |

| Figure 4.15 | Scanning results of task 6 of the heuristical analysis made to                                                                         |    |

|             | capacitance ratio values of the TECR algorithm. $C_{gdi}/C_{pgd}$ and                                                                  |    |

|                    | $C_{dsi}/C_{pds}$ are fixed in the values proposed in [74]. The scans on                                        |      |

|--------------------|-----------------------------------------------------------------------------------------------------------------|------|

|                    | $C_{gs}/C_{gd}$ and $C_{pds}/C_{pgs}$ are mapped as the X- and Y-axes and the Z-                                |      |

|                    | axis corresponds to the $E^{P}$ values obtained of applying the TECR                                            |      |

|                    | algorithm with the capacitance ratio values of each scan step. The                                              |      |

|                    | highlighted black dots indicate the $C_{gdi}/C_{pgd}$ and $C_{dsi}/C_{pds}$ values                              |      |

|                    | assumed in [74].                                                                                                | . 82 |

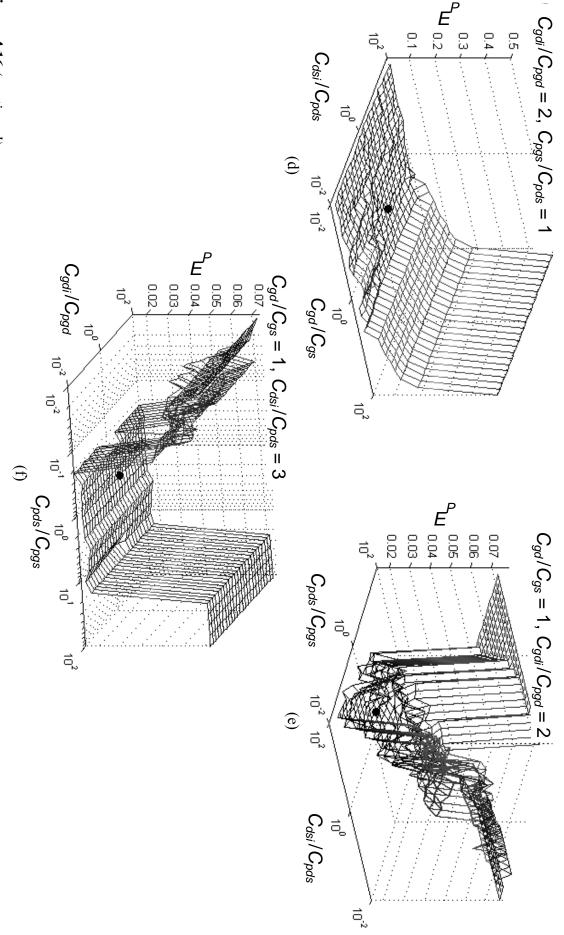

| Figure 4.16        | Sweeps of values on the capacitance ratios proposed by the TECR                                                 |      |

|                    | algorithm: (a) $C_{dsi}/C_{pds}$ and $C_{gdi}/C_{pgd}$ , (b) $C_{dsi}/C_{pds}$ and $C_{pds}/C_{pgs}$ , (c)      |      |

|                    | $C_{dsi}/C_{pds}$ and $C_{gs}/C_{gd}$ , (d) $C_{gdi}/C_{pgd}$ and $C_{pds}/C_{pgs}$ , (e) $C_{gdi}/C_{pgd}$ and |      |

|                    | $C_{gs}/C_{gd}$ , (f) $C_{gdi}/C_{pgd}$ and $C_{gs}/C_{gd}$ . Black dots mark values assumed in                 |      |

|                    | [74] (continues in the following page)                                                                          | . 87 |

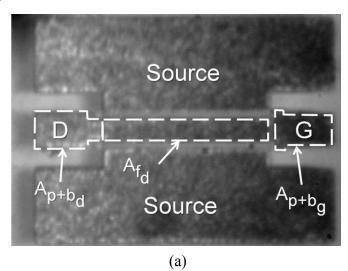

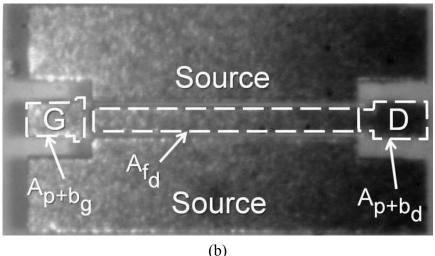

| Figure 4.17        | Example top-view photographs taken for this thesis useful to                                                    |      |

|                    | evaluate $A_{p+b_g}/A_{p+b_d}$ and $A_{p+b_d}/A_{f_d}$ , thus $C_{pgs}/C_{pds}$ and $C_{pds}/C_{dsi2}$ . They   |      |

|                    | are of IAF devices with two gate fingers and with gate peripheries                                              |      |

|                    | of (a) 0.5 mm and (b) 0.8 mm.                                                                                   | . 90 |

| Figure 4.18        | Example top-view images that can be found in datasheets of a                                                    |      |

|                    | commercial GaN HEMT, (a) photograph and (b) technical drawing,                                                  |      |

|                    | which would be useful to evaluate $C_{pgs}/C_{pds}$ and $C_{pds}/C_{dsi2}$ [62]                                 | . 91 |

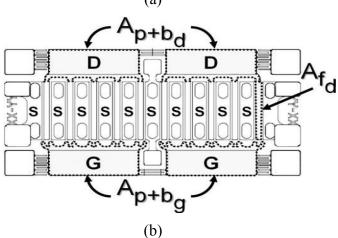

| Figure 4.19        | Example top-view photographs taken for this thesis, which are not                                               |      |

|                    | useful to evaluate $C_{pgs}/C_{pds}$ due to the source air bridges. They are of                                 |      |

|                    | (left) the 2-mm Nitronex® device and of (right) the 3.2-mm IAF                                                  |      |

|                    | device                                                                                                          | . 91 |

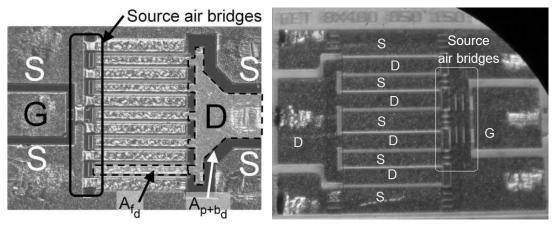

| Figure 4.20        | Example top-view photographs taken for this thesis using a                                                      |      |

|                    | commercial camera with zooming factor applied, which are useful                                                 |      |

|                    | to evaluate $C_{dsil}/C_{pgd}$ . They are of IAF devices with unit gate width                                   |      |

|                    | of 0.25 mm and: (a) 8 gate fingers, (b) 2 gate fingers                                                          | . 92 |

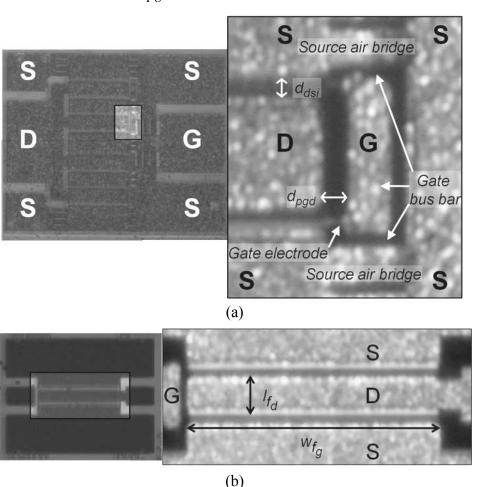

| Figure 4.21        | Top-view micrographs of two GaN HEMTs, (a) of a 3.2-mm IAF                                                      |      |

|                    | device, which is useful to evaluate $C_{gsi}/C_{gdi}$ , and (b) of a 2-mm                                       |      |

|                    | Nitronex® device, which shows a field plate and thus is not useful to                                           |      |

|                    | evaluate $C_{gsi}/C_{gdi}$ .                                                                                    | . 93 |

| <b>Figure 4.22</b> | (a) Small-signal model and (b) equivalent circuit in cold pinch-off                                             |      |

|                    | condition for the low-frequency range.                                                                          | . 95 |

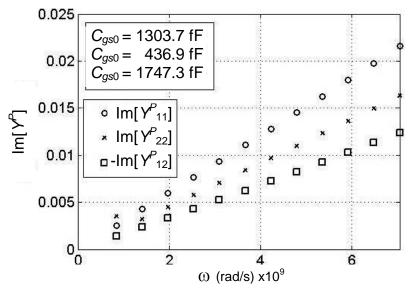

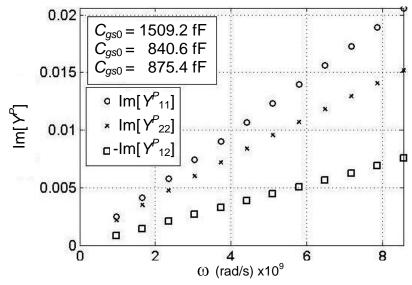

| <b>Figure 4.23</b> | Y-parameters from cold pinch-off measurements in the low-                                                       |      |

|                    | frequency range and the extracted values of branch capacitances for                                             |      |

|                    | the 2-mm device.                                                                                                | . 96 |

| Figure 4.24        | Y-parameters from cold pinch-off measurements in the low-                                                       |      |

|                    | frequency range and extracted values of branch capacitances for the                                             |      |

|                    | 3.2-mm device.                                                                                                  | . 96 |

| Figure 4.25        | Illustration of extrinsic inductance parameter extraction used in this                                          |      |

|                    | thesis work (drawn from the procedures described in the TECR                                                    |      |

|                    | algorithm [74-76])                                                                                              | . 97 |

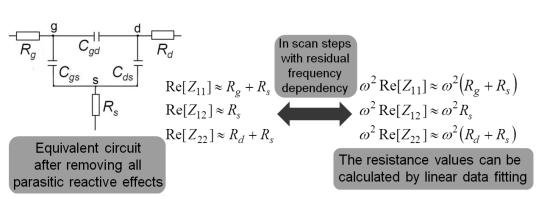

| Figure 4.26        | Illustration of extrinsic resistance parameter extraction used in this                                          |      |

|                    | thesis work (drawn from the procedures described in the TECR                                                    |      |

|                    | algorithm [74-76]).                                                                                             | . 98 |

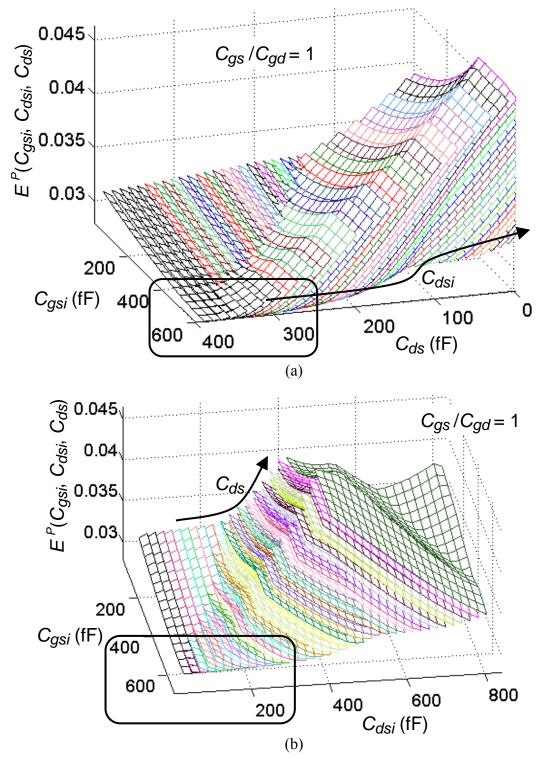

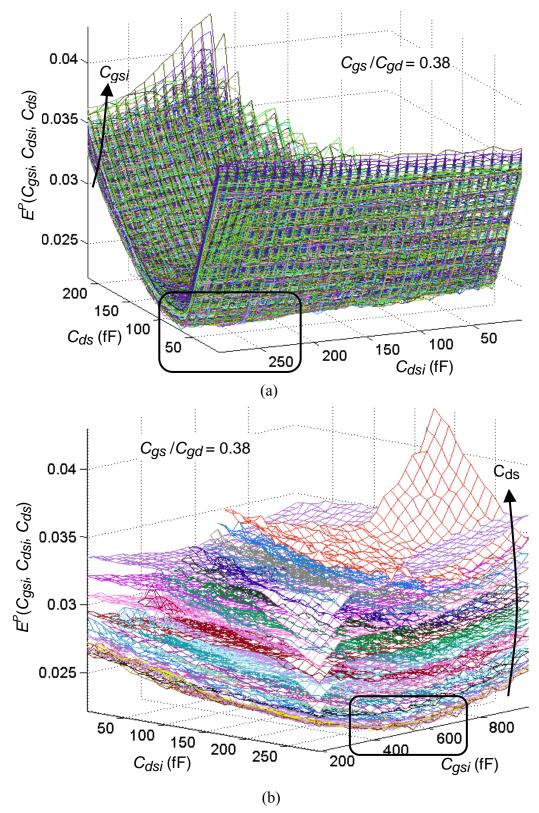

| Figure 4.27        | First set of graphs resulting from applying the sweeps of values on                                           |     |

|--------------------|---------------------------------------------------------------------------------------------------------------|-----|

|                    | four capacitance parameters using cold pinch-off S-parameters                                                 |     |

|                    | measurements of the 2-mm device: Sweep results of $E^{P}(C_{gsi}, C_{ds},$                                    |     |

|                    | $C_{dsi}$ ) values mapped on the planes of (a) $C_{gsi}$ versus $C_{ds}$ and (b) $C_{gsi}$                    |     |

|                    |                                                                                                               | 101 |

| Figure 4.28        | Second set of graphs resulting from applying the sweeps of values                                             |     |

| S                  | on four capacitance parameters using <i>cold pinch-off</i> S-parameters                                       |     |

|                    | measurements of the 2-mm device. (a) Sweep results of $E^P(C_{gsi}, C_{ds},$                                  |     |

|                    | $C_{dsi}$ ) values mapped on the plane of $C_{ds}$ versus $C_{dsi}$ , and (b)                                 |     |

|                    | $\min[E^P(C_{gsi}, C_{ds}, C_{dsi})]$ plotted with respect to $C_{gsi}/C_{gd}$                                | 102 |

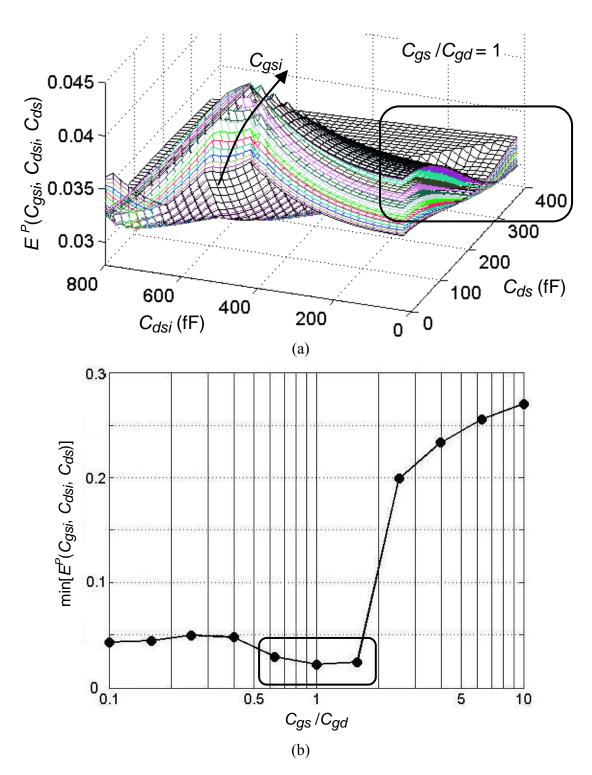

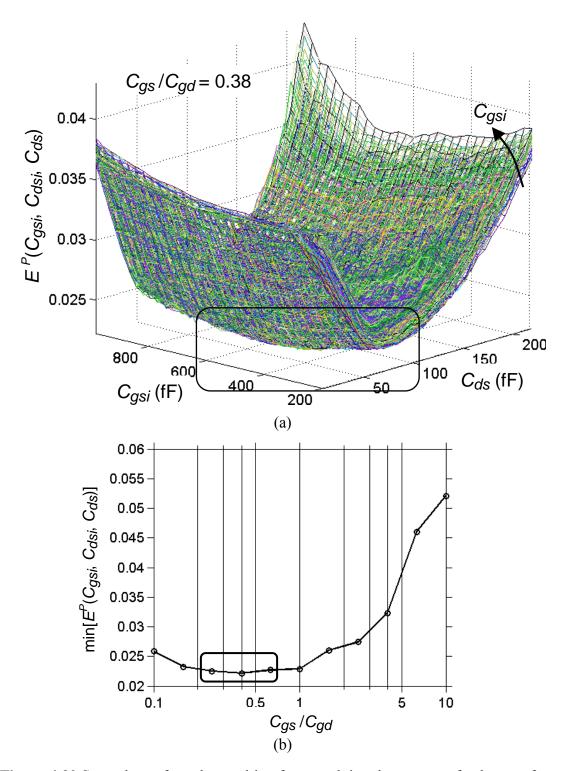

| Figure 4 29        | First set of graphs resulting from applying the sweeps of values on                                           | 102 |

| rigure 4.27        | four capacitance parameters using <i>cold pinch-off</i> S-parameters                                          |     |

|                    | measurements of the 3.2-mm device. Sweep results of $E^P(C_{gsi}, C_{ds},$                                    |     |

|                    |                                                                                                               |     |

|                    | $C_{dsi}$ ) values mapped on the planes of (a) $C_{dsi}$ versus $C_{ds}$ and (b) $C_{gsi}$ versus $C_{dsi}$ . | 105 |

| Figure 4.20        | 4.51                                                                                                          | 103 |

| rigure 4.50        | Second set of graphs resulting from applying the sweeps of values                                             |     |

|                    | on four capacitance parameters using <i>cold pinch-off</i> S-parameters                                       |     |

|                    | measurements of 3.2-mm device. (a) Sweep results of $E^{P}(C_{gsi}, C_{ds}, C_{ds})$                          |     |

|                    | $C_{dsi}$ ) values mapped on the plane of $C_{ds}$ versus $C_{gsi}$ , and (b)                                 | 106 |

|                    | $\min[E^P(C_{gsi}, C_{ds}, C_{dsi})]$ plotted with respect to $C_{gs}/C_{gd}$                                 | 106 |

| Figure 4.31        | Variation between GaN devices of different manufacturers of the                                               |     |

|                    | positive $V_{GS}$ value needed to produce dominant inductive behavior                                         |     |

|                    | of $S_{11}$ ( $V_{DS} = 0$ V). The related transistors have the same size (0.1                                |     |

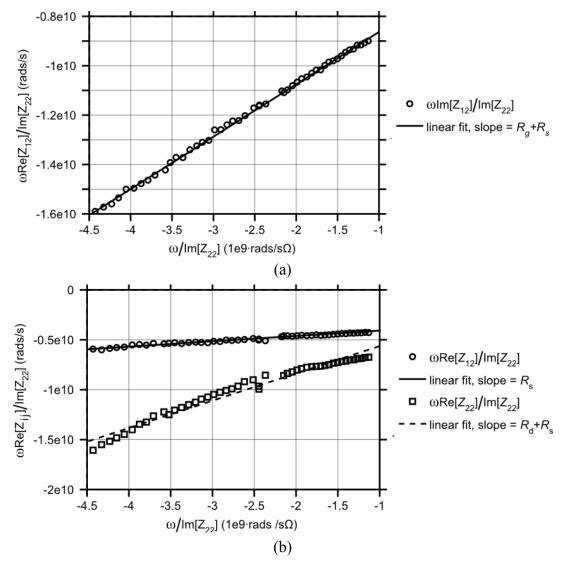

|                    | mm) but were fabricated by (a) FBH and (b) IEMN.                                                              | 108 |

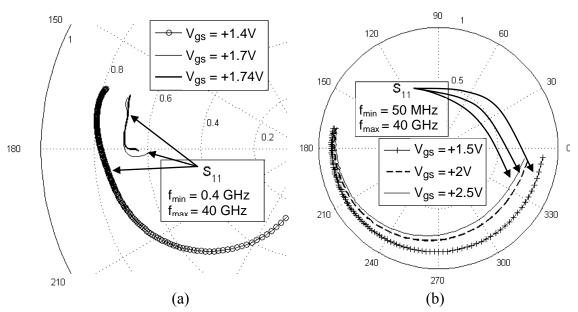

| Figure 4.32        | Illustration of the extraction of extrinsic resistance parameters from                                        |     |

|                    | cold reverse S-parameters measurements of the 3.2-mm device.                                                  |     |

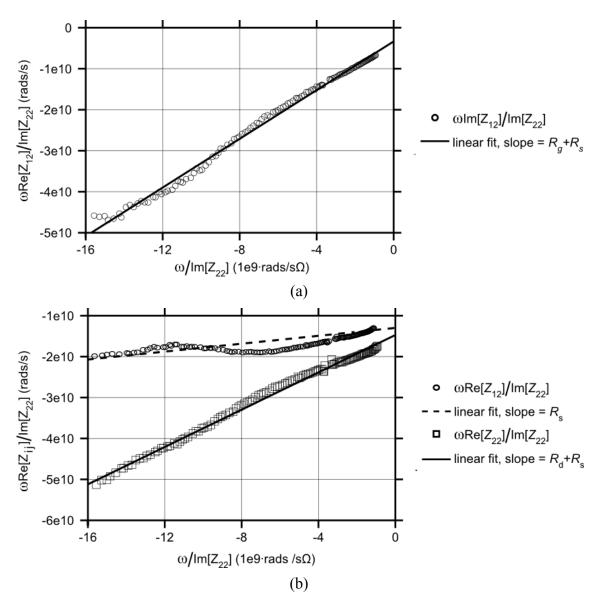

|                    | Extraction of (a) $R_g+R_s$ and of (b) $R_d+R_s$ and $R_s$ .                                                  | 112 |

| Figure 4.33        | Illustration of the extrinsic resistance extraction from <i>cold reverse</i>                                  |     |

|                    | S-parameters measurements applied to the 2-mm device. Extraction                                              |     |

|                    | of (a) $R_g + R_s$ and of (b) $R_d + R_s$ and $R_s$ .                                                         | 113 |

| Figure 4.34        | Intrinsic transistor equivalent circuit formulated with admittance                                            |     |

|                    | branches.                                                                                                     | 114 |

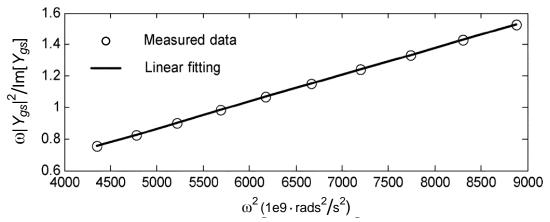

| <b>Figure 4.35</b> | Linear data fitting of the measured data for the defined variable $D$                                         |     |

|                    | $(V_{DS} = 20 \text{V}, V_{GS} = -2 \text{V})$ , taken from [74]. It supports the use of D to                 |     |

|                    | obtain $C_{gs}$ from the slope.                                                                               | 116 |

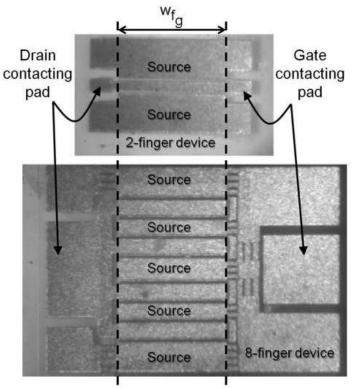

| <b>Figure 4.36</b> | Example of change of the finger layout due to the scaling of $n_{f_g}$ from                                   |     |

|                    | (top image) 2 fingers to (bottom image) 8 fingers. Both are IAF                                               |     |

|                    | devices with $w_{f_g} = 0.4$ mm from the same wafer fragment, i.e. same                                       |     |

|                    | fabrication process.                                                                                          | 120 |

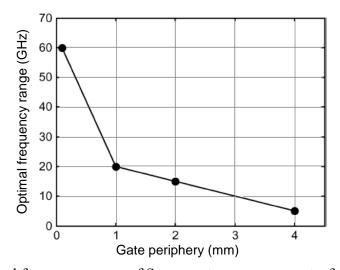

| Figure 5.1         |                                                                                                               | 120 |

| 1150110 5.1        | usage to extract extrinsic parameters of the adopted small-signal                                             |     |

|                    | model, in terms of the gate periphery of the modeled device, as                                               |     |

|                    | given in [76]                                                                                                 | 122 |

|                    | 51 VOII III   / U                                                                                             | 144 |

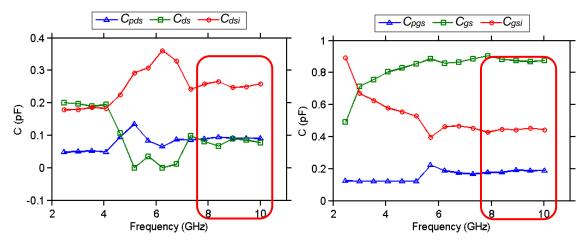

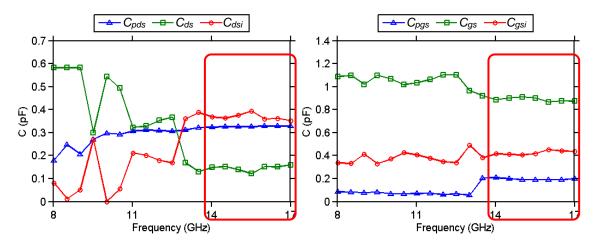

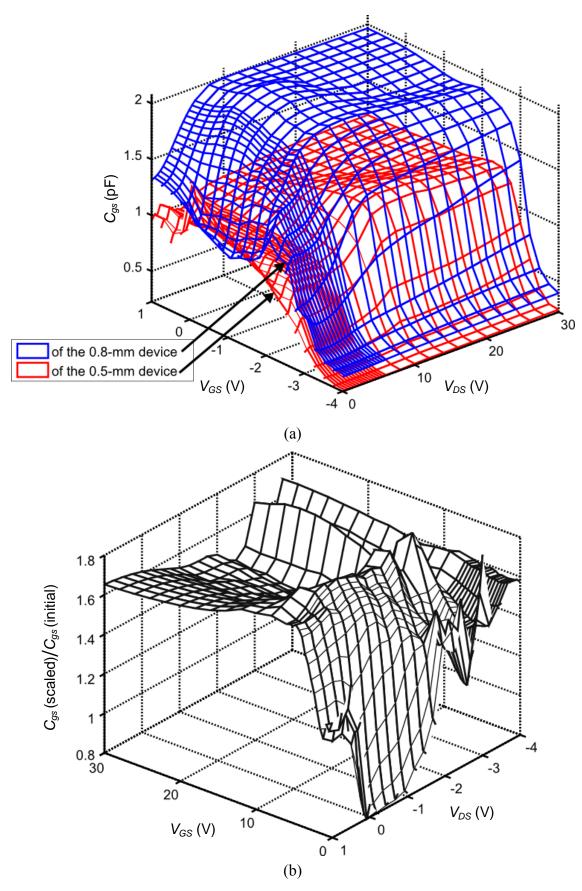

| Figure 5.2         | Values of drain-source (left) and gate-source (right) capacitance                      |       |

|--------------------|----------------------------------------------------------------------------------------|-------|

|                    | parameters extracted for the model of the 3.2-mm device with                           |       |

|                    | different frequency ranges of the S-parameters data. The optimal                       |       |

|                    | frequency range is highlighted                                                         | . 123 |

| Figure 5.3         | Values of drain-source (left) and gate-source (right) capacitance                      |       |

|                    | parameters extracted for the model of the 2-mm device with                             |       |

|                    | different frequency ranges of the S-parameters data. The optimal                       |       |

|                    | frequency range is highlighted.                                                        | . 123 |

| Figure 5.4         | 1 "                                                                                    |       |

|                    | (markers) compared with the simulations (lines) produced with the                      |       |

|                    | high-quality starting values of model parameters given in Table 5.1                    | . 125 |

| Figure 5.5         | S-parameters measured in <i>cold pinch-off</i> of the 2-mm device                      |       |

|                    | (markers) compared with the simulations (lines) produced with the                      |       |

|                    | high-quality starting values of model parameters given in Table 5.1                    | . 125 |

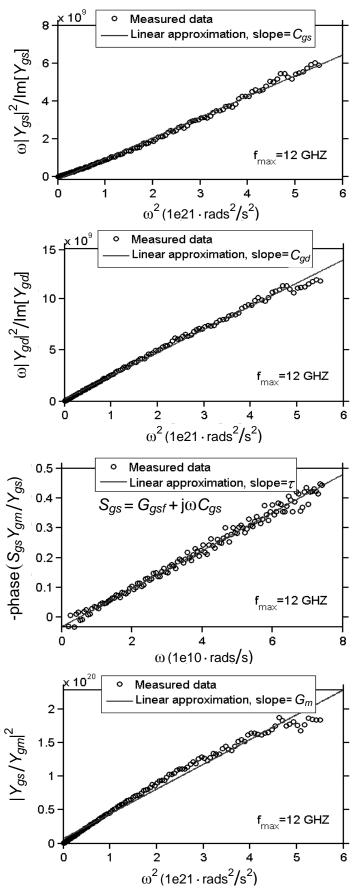

| Figure 5.6         | Plots of measured data related to the intrinsic transistor used to                     |       |

|                    | extract by linear approximation $C_{gs}$ , $C_{gd}$ , $\tau$ and $G_m$ , respectively, |       |

|                    | from S-parameter measurements of the 2-mm device on the active                         |       |

|                    | bias point $V_{GS} = -1.5$ V, $V_{DS} = 5$ V                                           | . 127 |

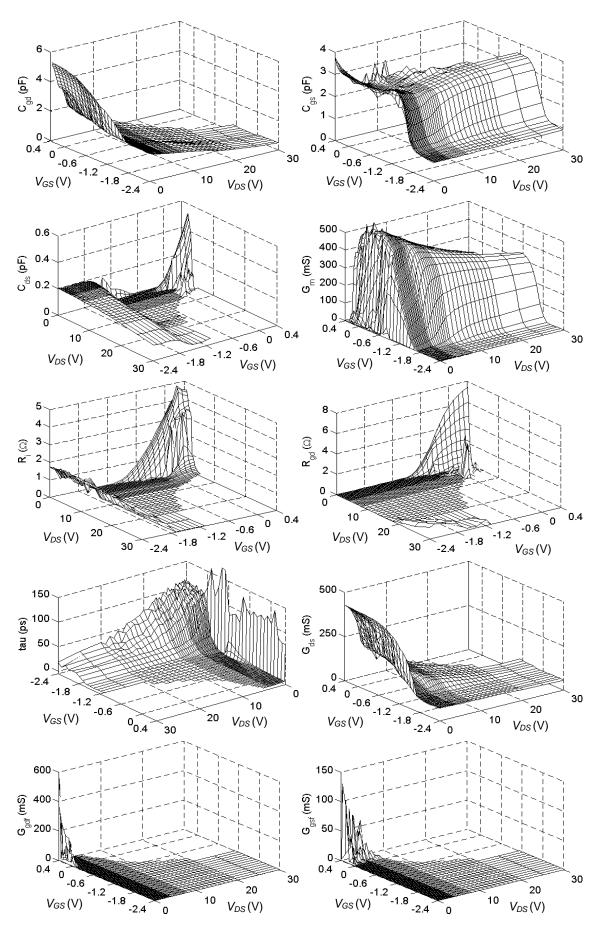

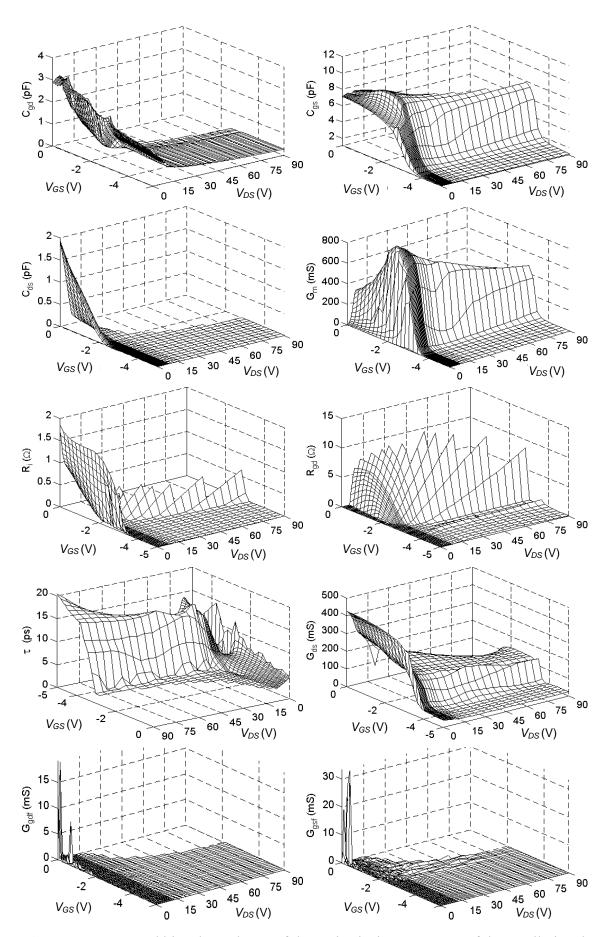

| Figure 5.7         | Extracted bias-dependency of the 10 intrinsic parameters of the                        |       |

|                    | small-signal model for the 2-mm.                                                       | . 129 |

| Figure 5.8         | Extracted bias-dependency of the 10 intrinsic parameters of the                        |       |

|                    | small-signal model for the 3.2-mm device.                                              | . 130 |

| Figure 5.9         | Bias dependency of the accuracy to predict S-parameters of the                         |       |

|                    | small-signal model developed for the 2-mm device.                                      | . 134 |

| Figure 5.10        | Bias dependency of the accuracy to predict S-parameters of the                         |       |

|                    | small-signal model developed for the 3.2-mm device.                                    | . 134 |

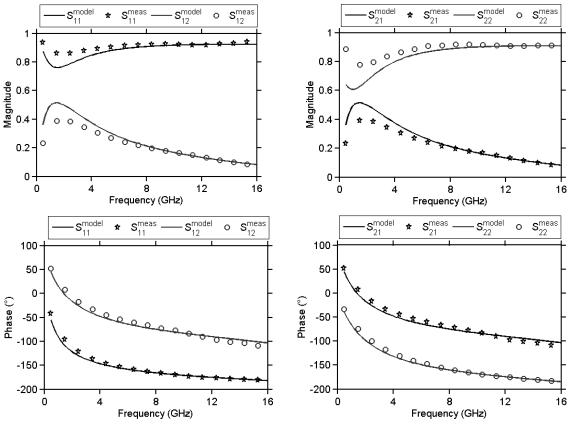

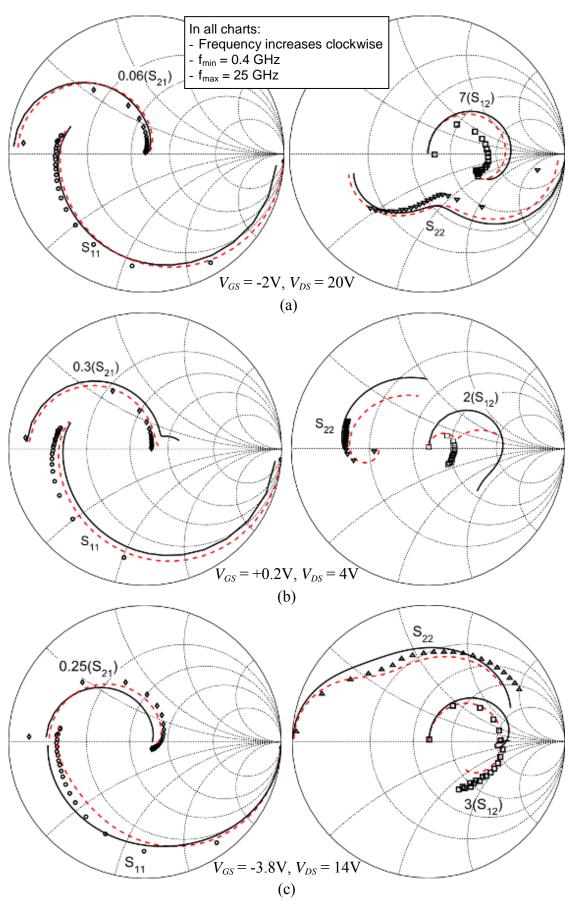

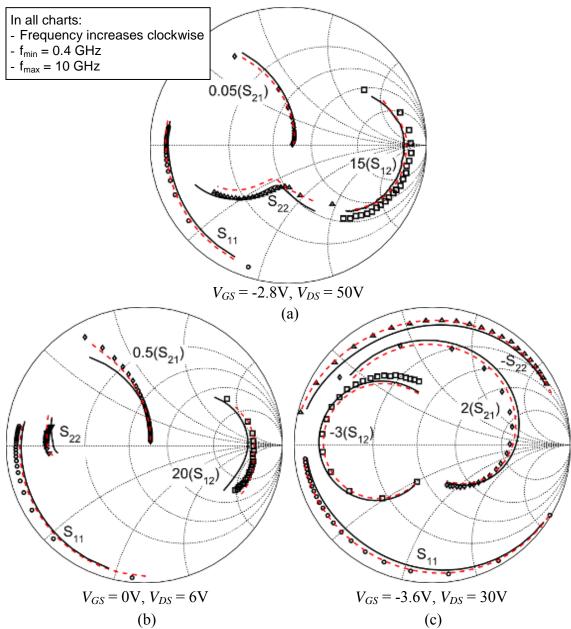

| Figure 5.11        | Comparison of measured S-parameters with predictions of the                            |       |

|                    | small-signal model developed for the 2-mm, on active bias points in                    |       |

|                    | the (a) saturation, (b) high- $V_{GS}$ low- $V_{DS}$ and (c) pinch-off regions         | . 135 |

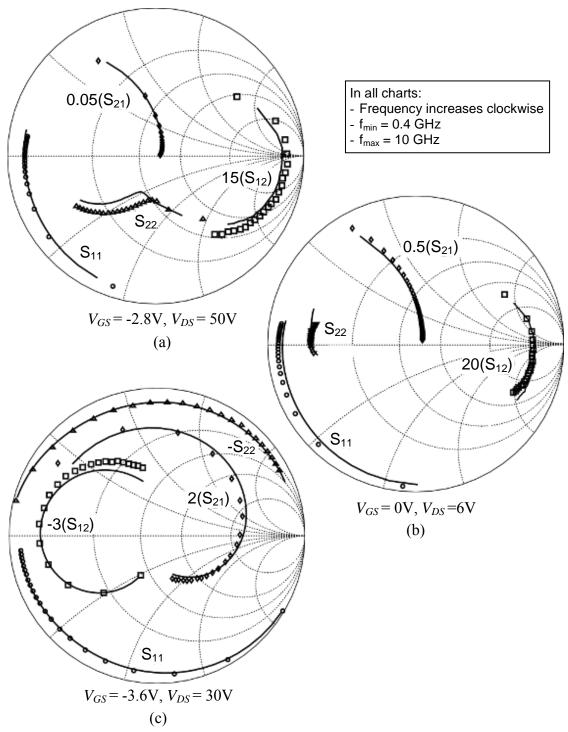

| Figure 5.12        | Comparison of measured S-parameters with predictions of the                            |       |

|                    | small-signal model developed for the 3.2-mm device, on active bias                     |       |

|                    | points in the (a) saturation, (b) high- $V_{GS}$ low- $V_{DS}$ and (c) pinch-off       | 100   |

| TI #40             | regions.                                                                               | . 136 |

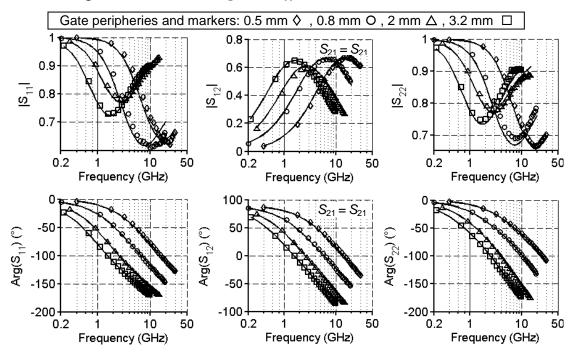

| Figure 5.13        | Comparison of measured <i>cold pinch-off</i> S-parameters (solid lines)                |       |

|                    | with predictions of the small-signal models (markers) developed for                    | 120   |

| E: 514             | the family of devices.                                                                 | . 139 |

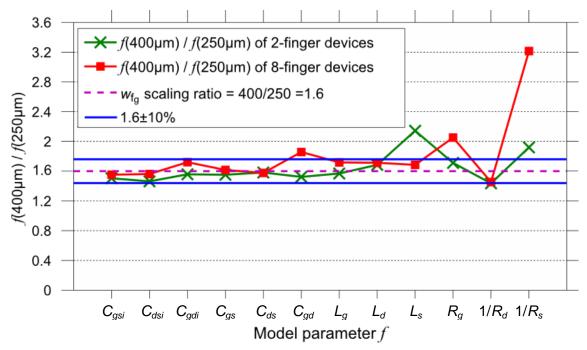

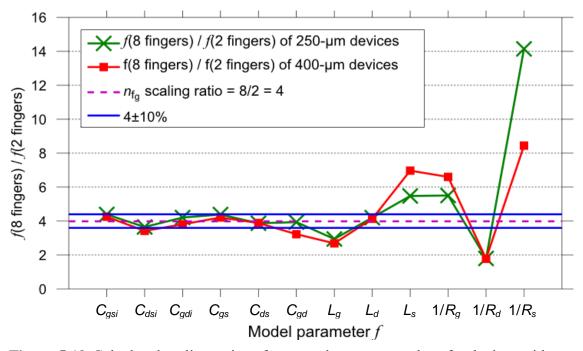

| Figure 5.14        | Calculated scaling ratios of extracted parameter values for devices                    | 1.40  |

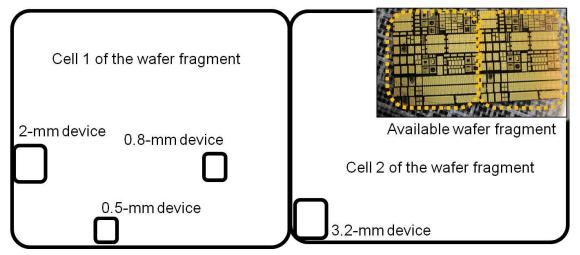

|                    | with $w_{f_g}$ scaled but same number of fingers.                                      | . 140 |

| Figure 5.15        | Location of the devices, whose model parameter scalability was                         |       |

|                    | analyzed, on the available wafer fragment                                              | . 142 |

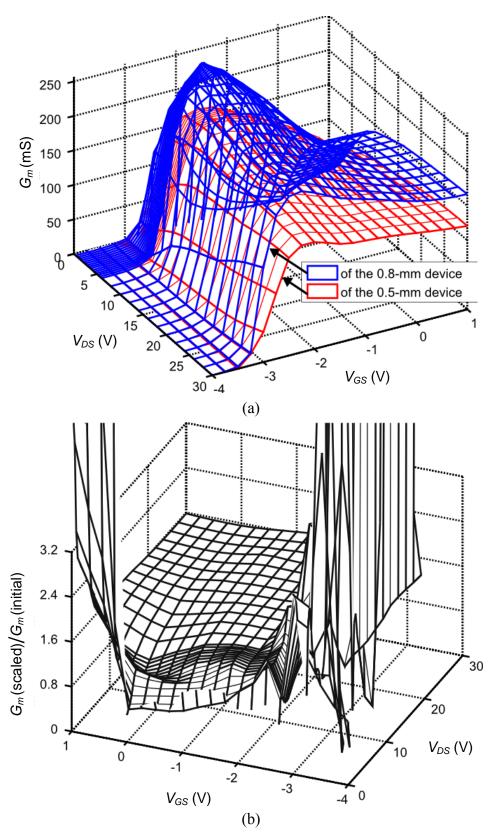

| <b>Figure 5.16</b> | (a) Bias-dependent extracted values of $G_m$ of 2-finger devices with                  |       |

|                    | scaling gate width from 250 µm (red line) to 400 µm (blue line), and                   |       |

|                    | (b) bias-dependent values calculated for f(scaled)/f(initial)                          | 143   |

| <b>Figure 5.17</b> | (a) Bias-dependent extracted values of $C_{gs}$ of 2-finger devices with       |       |

|--------------------|--------------------------------------------------------------------------------|-------|

|                    | scaling gate width from 250 $\mu m$ (red line) to 400 $\mu m$ (blue line), and |       |

|                    | (b) bias-dependent values calculated for f(scaled)/f(initial)                  | 144   |

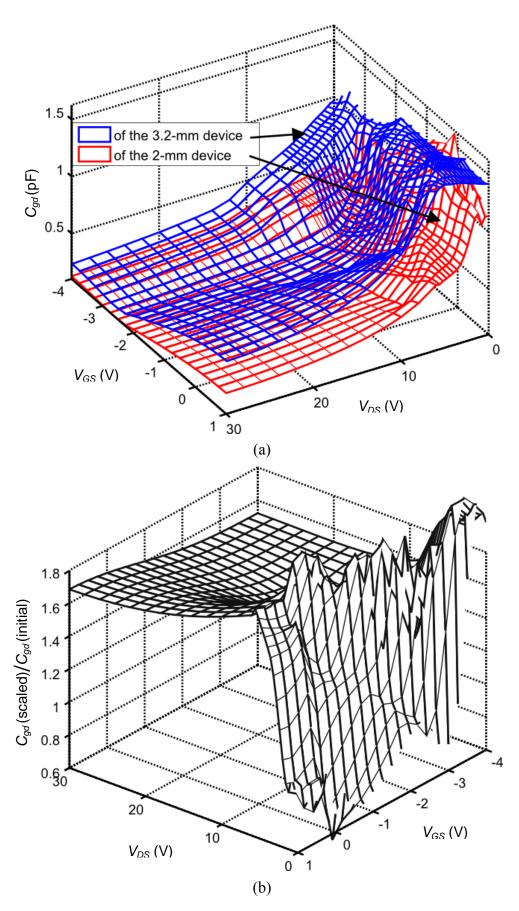

| <b>Figure 5.18</b> | (a) Bias-dependent extracted values of $C_{gd}$ of 8-finger devices with       |       |

|                    | scaling gate width from 250 $\mu m$ (red line) to 400 $\mu m$ (blue line), and |       |

|                    | (b) bias-dependent values calculated for f(scaled)/f(initial)                  | 145   |

| <b>Figure 5.19</b> | Calculated scaling ratios of extracted parameter values for devices            |       |

|                    | with $n_{f_g}$ scaled but same unit gate electrode width.                      | 146   |

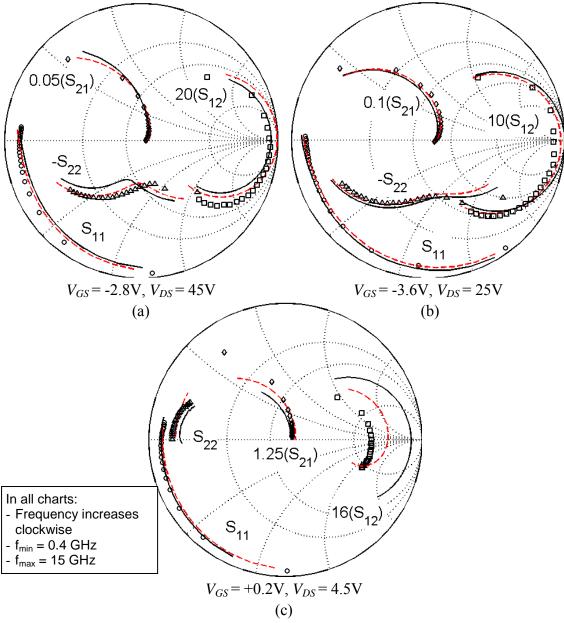

| Figure 5.20        | Measurements of the 0.8-mm device (markers) compared to S-                     |       |

|                    | parameters of the corresponding $w_f$ -scaled (solid lines) and initial        |       |

|                    | models (red dashed lines), on bias points in the (a) saturation, (b)           |       |

|                    | high- $V_{GS}$ low- $V_{DS}$ and (c) pinch-off regions                         | 150   |

| Figure 5.21        | Measurements of the 3.2-mm device (markers) compared to S-                     |       |

|                    | parameters of the corresponding $w_f$ -scaled (solid lines) and initial        |       |

|                    | models (red dashed lines), on bias points in the (a) saturation, (b)           |       |

|                    | high- $V_{GS}$ low- $V_{DS}$ and (c) pinch-off regions                         | 151   |

| Figure 5.22        | Measured S-parameters of the 2-mm device (markers) compared                    |       |

|                    | with predictions of the quasi-scaled model from the 0.5-mm device              |       |

|                    | model (solid lines) and with predictions of the initial model (red             |       |

|                    | dashed lines), on bias points in the (a) saturation, (b) pinch-off and         |       |

|                    | (c) high- $V_{GS}$ low- $V_{DS}$ regions.                                      | 152   |

| <b>Figure 5.23</b> | Measurements of the 3.2-mm device biased on $V_{GS} = -2.8$ V and $V_{DS}$     |       |

|                    | = 50V (circles) compared with S-parameters of the <i>two-step scaled</i>       |       |

|                    | $model$ (blue thin lines), of the $w_f$ -scaled $model$ (black thick lines)    |       |

|                    | and of the <i>initial model</i> (red dashed lines).                            | 153   |

| <b>Figure 5.24</b> | Measurements of the 3.2-mm device biased on $V_{GS} = 0$ V and $V_{DS} = 0$    |       |

|                    | 6V (markers) compared with S-parameters of the two-step scaled                 |       |

|                    | model (blue thin lines), of the $w_f$ -scaled model (black thick lines)        |       |

|                    | and of the <i>initial model</i> (red dashed lines)                             | 154   |

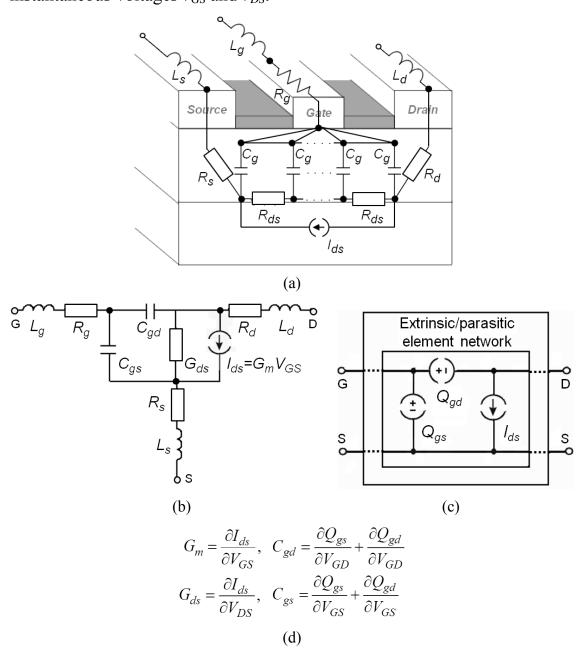

| Figure 6.1         | Typical formulation of the quasi-static charge model: (a) physical             |       |

|                    | origin, (b) small-signal (b) and large-signal equivalent circuits, (d)         |       |

|                    | voltage-dependent relationships between small-signal capacitance               |       |

|                    | and conductance parameters and large-signal current and charge                 |       |

|                    | sources.                                                                       | 157   |

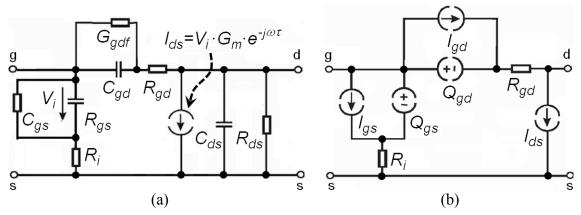

| Figure 6.2         | Non-quasi-static equivalent circuits adopted in this thesis work in            | 4 = 0 |

|                    | the (a) small-signal and (b) large-signal models                               | 158   |

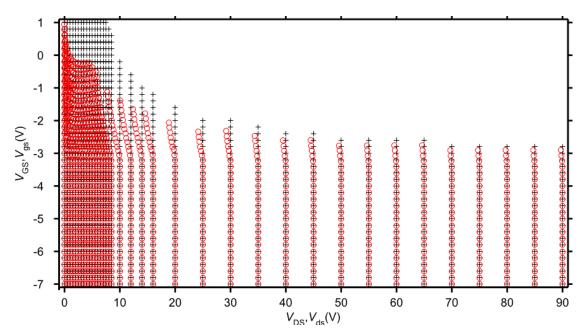

| Figure 6.3         | Results of voltage remapping for the 3.2-mm device showing the                 |       |

|                    | original orthogonal $V_{GS}$ - $V_{DS}$ grid (black crosses) overlapped with   | 1.00  |

| T                  | received non-orthogonal $V_{gs}$ - $V_{ds}$ grid (red circles).                | 160   |

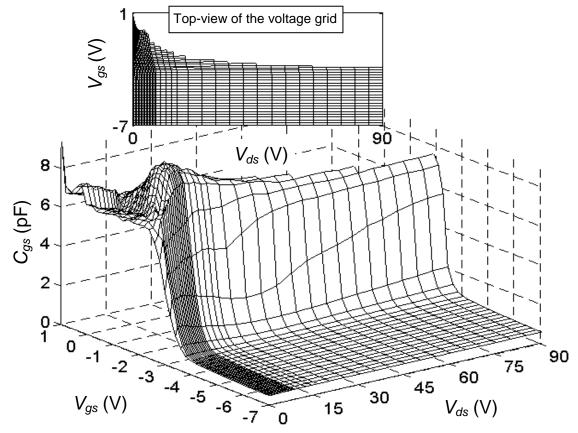

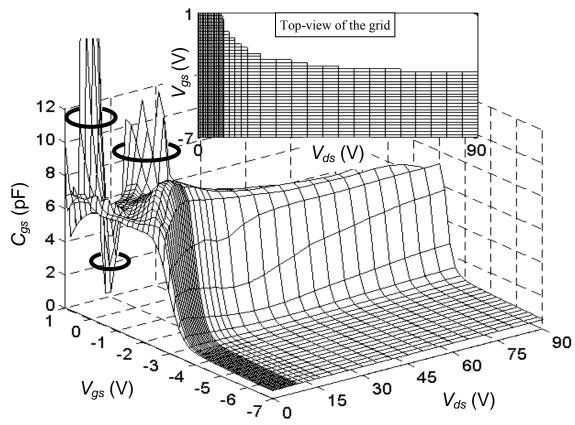

| Figure 6.4         | Extracted $C_{gs}$ values of the 3.2-mm device, with their dependency          |       |

|                    | on the applied DC voltages expressed on the received non-                      | 1.60  |

| TO!                | orthogonal $V_{gs}$ - $V_{ds}$ grid.                                           | 160   |

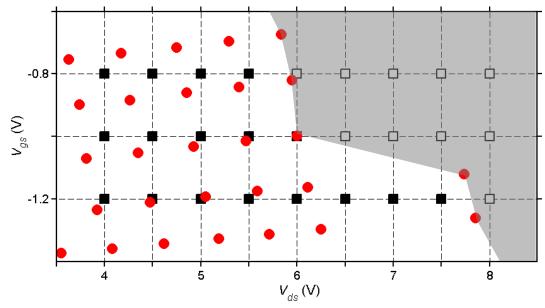

| Figure 6.5         | Illustration of the data before and after re-gridding: the circles are         |       |

|                    | the non-orthogonal available data points and the squares the desired           |       |

|                       | orthogonal data points. The filled squares require interpolation and the hollow extrapolation. The <i>off-range</i> region of the available data is shown shaded.                                                                                                                                                                                                                                                                                 | . 161 |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

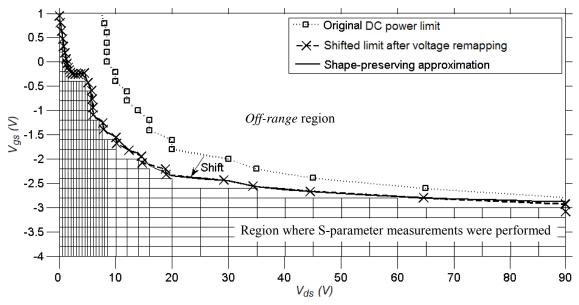

| Figure 6.6 Figure 6.7 | Re-gridded voltage-dependency of the Cgs values expressed on the $V_{gs}$ - $V_{ds}$ grid encircling unreliable values due to extrapolation. Inset: top-view of the orthogonal grid and with off-range region defined by the DC power limit (an array that contained the $V_{GS}$ - $V_{DS}$ grid was used to indicate the <i>off-range</i> region to the re-gridding routine). Shift of the DC power limit and the related approximated function | . 163 |

|                       | obtained.                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 164 |

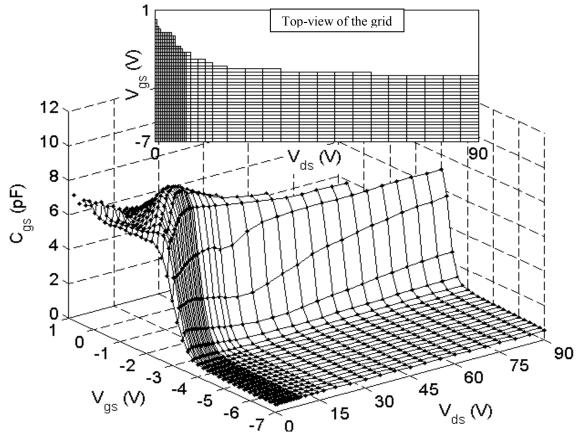

| Figure 6.8            | Improved re-gridded voltage-dependency of the $C_{gs}$ values expressed on the $V_{gs}$ - $V_{ds}$ grid. Inset: top-view of the grid showing orthogonality and the <i>off-range</i> region defined by the shifted limit (a Matlab <sup>®</sup> variable with a functional approximation of the shifted DC power limit to indicate the <i>off-range</i> region to the re-gridding routine).                                                        | . 164 |

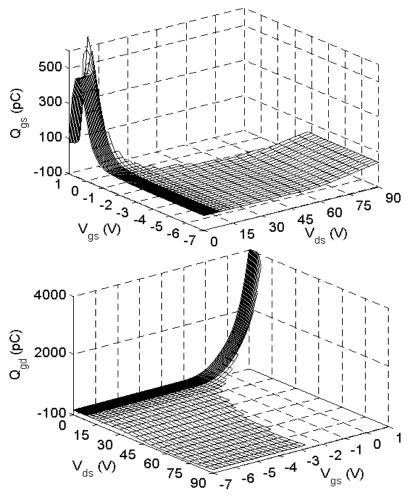

| Figure 6.9            | Voltage-dependencies of $Q_{gs}$ and $Q_{gd}$ calculated for the 3.2-mm device based on $C_{gs}$ , $C_{gd}$ and $C_{ds}$ re-gridded using the Matlab <sup>®</sup> variable containing the $V_{GS}$ - $V_{DS}$ grid in the call of the re-gridding routine to prevent extrapolation as done in [64, 111]                                                                                                                                           | . 165 |

| Figure 6.10           | Voltage-dependencies of $Q_{gs}$ and $Q_{gd}$ calculated for the 3.2-mm device based on $C_{gs}$ , $C_{gd}$ and $C_{ds}$ re-gridded using the newly created Matlab <sup>®</sup> variable for the shifted limit in the call of the re-gridding                                                                                                                                                                                                     |       |

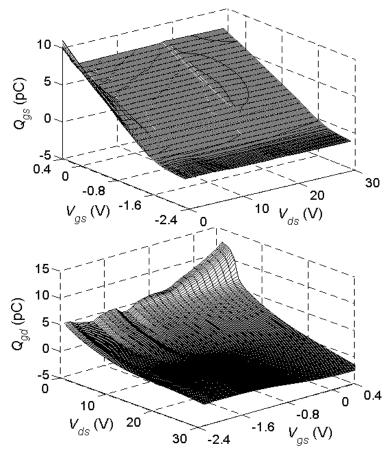

| Figure 6.11           | routine to prevent extrapolation.  Voltage-dependencies of $Q_{gs}$ and $Q_{gd}$ calculated for the 2-mm device interpolated to a denser equally-spaced grid and extrapolated to the <i>off-range</i> region, based on $C_{gs}$ , $C_{gd}$ and $C_{ds}$ re-gridded using the newly created Matlab <sup>®</sup> variable for the shifted limit in the call of the re-gridding routine.                                                             |       |

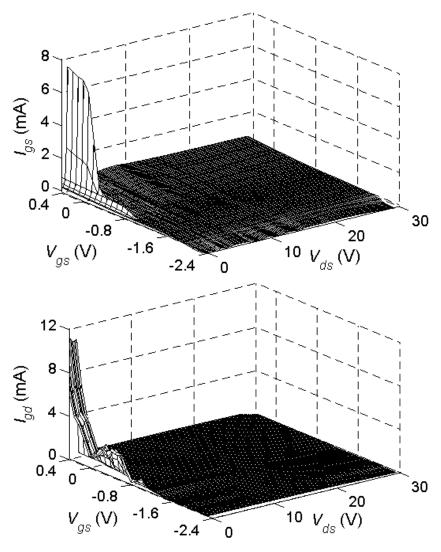

| Figure 6.12           | Voltage-dependencies of $I_{gs}$ and $I_{gd}$ calculated for the 2-mm device interpolated to a denser equally-spaced grid and extrapolated to the <i>off-range</i> region, based on $G_{gsf}$ and $G_{gdf}$ re-gridded using the newly created Matlab <sup>®</sup> variable for the shifted limit in the call of the regridding routine.                                                                                                          |       |

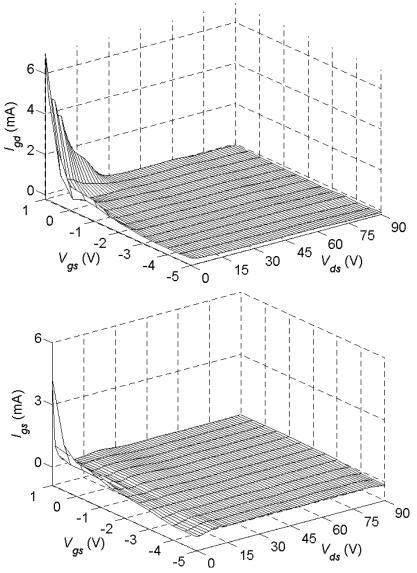

| Figure 6.13           | Voltage-dependencies of $I_{gs}$ and $I_{gd}$ calculated for the 3.2-mm device interpolated to a denser equally-spaced grid and extrapolated to the <i>off-range</i> region, based on $G_{gsf}$ and $G_{gdf}$ re-gridded using the newly created Matlab <sup>®</sup> variable for the shifted limit in the call of the regridding routine.                                                                                                        |       |

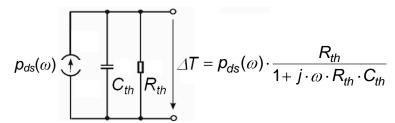

|                       | Electro-thermal sub-circuit used to represent frequency-dependent self-heating effects [79]                                                                                                                                                                                                                                                                                                                                                       |       |

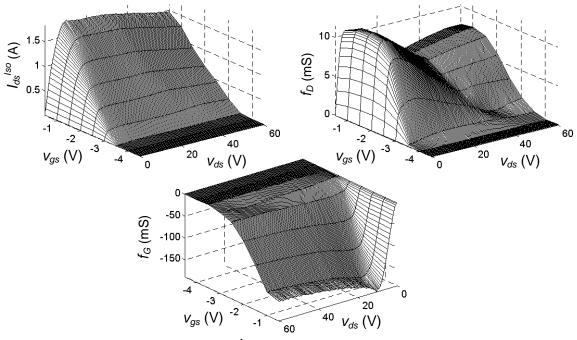

| Figure 6.15           | Calculated values of $I_{ds}^{Iso}(v_{gs}, v_{ds})$ , $f_G(v_{gs}, v_{ds})$ and $f_D(v_{gs}, v_{ds})$ for the 3.2-mm device.                                                                                                                                                                                                                                                                                                                      |       |

| Figure 6.16           | Calculated values of $I_{ds}^{Iso}(v_{gs}, v_{ds})$ , $f_G(v_{gs}, v_{ds})$ and $f_D(v_{gs}, v_{ds})$ for the                                                                                                                                                                                                                                                                                                                                     | 177   |

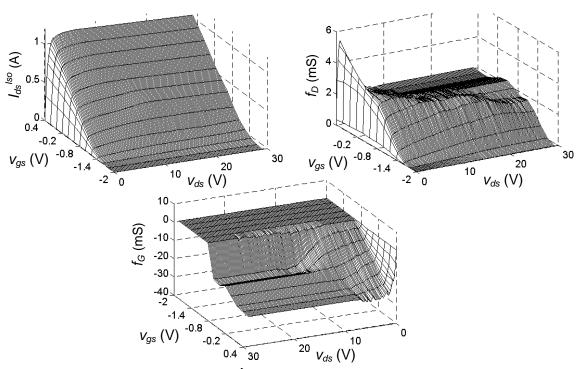

| Figure 6.17        | Validity regions for pulsed-DC IV verifications tests of models                                                                                              |     |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                    | developed for the 3.2-mm device: (a) Model validity region                                                                                                   |     |

|                    | considering only two active quiescent bias points for the calculation                                                                                        |     |

|                    | of $f_P$ and (b) expanded model validity region considering additional                                                                                       |     |

|                    | active <i>quiescent</i> bias points for the calculation of $f_P$                                                                                             | 179 |

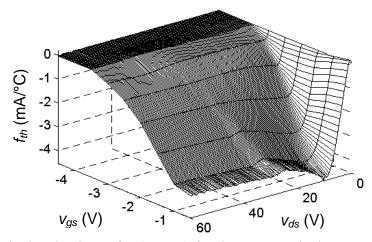

| Figure 6.18        | Calculated values of $f_{th}(v_{gs}, v_{ds})$ for the 3.2-mm device                                                                                          | 180 |

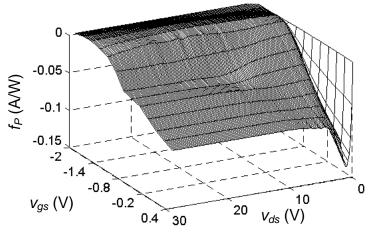

| Figure 6.19        | Calculated values of $f_P(v_{gs}, v_{ds})$ for the 2-mm device                                                                                               | 180 |

|                    | Illustration of the RC circuits used in [115] as high-pass filters, for                                                                                      |     |

|                    | the computation of $(v_{gs}-V_{GS})$ and $(v_{ds}-V_{DS})$ during simulations, and                                                                           |     |

|                    | employed in [65] to denote trapping time constants extracted from                                                                                            |     |

|                    | measured drain current transients.                                                                                                                           | 181 |

| Figure 6.21        | Illustration of initial (cross) and pulsed-to (X) quiescent bias points                                                                                      |     |

|                    | chosen for the transient measurements of the 3.2-mm device used to                                                                                           |     |

|                    | extract (a) $R_{DT} \cdot C_{DT}$ ( $V_{GS} = 0V$ , $V_{DS} = 0V$ , $P_{DS} = 0V$ and $V_{GS} = 0V$ ,                                                        |     |

|                    | $V_{DS} = 1.05 \text{V}, P_{DS} \approx 0.31 \text{W}) \text{ and (b) } R_{GT} \cdot C_{GT} (V_{GS} = -1.2 \text{V}, V_{DS} = -1.2 \text{V})$                |     |

|                    | 4.5V, $P_{DS} \approx 5$ W and $V_{GS} = -2$ V, $V_{DS} = 7.5$ V, $P_{DS} \approx 5$ W)                                                                      | 182 |

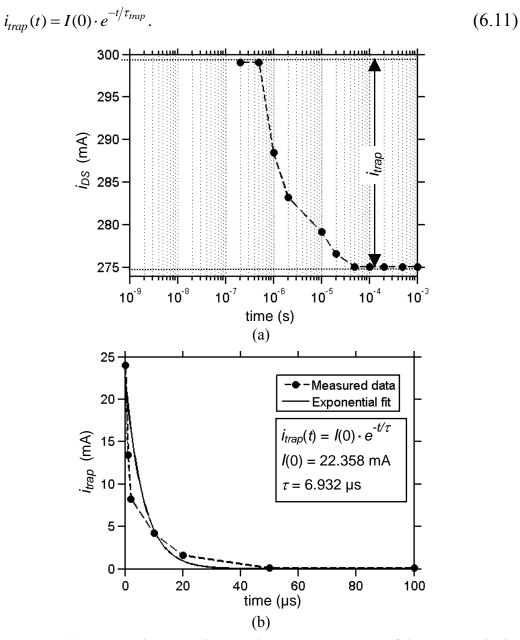

| Figure 6.22        | (a) Measured $i_{DS}$ transient used to extract $R_{DT} \cdot C_{DT}$ of the 3.2-mm                                                                          |     |

|                    | device, highlighting the $i_{trap}$ component related to the dominant                                                                                        |     |

|                    | trapping effect. (b) Separated $i_{trap}$ (dashed dot-marked lines) and the                                                                                  |     |

|                    | employed exponential fit (solid line). The initial and pulsed-to                                                                                             |     |

|                    | quiescent bias points were illustrated in Figure 6.21(a)                                                                                                     | 183 |

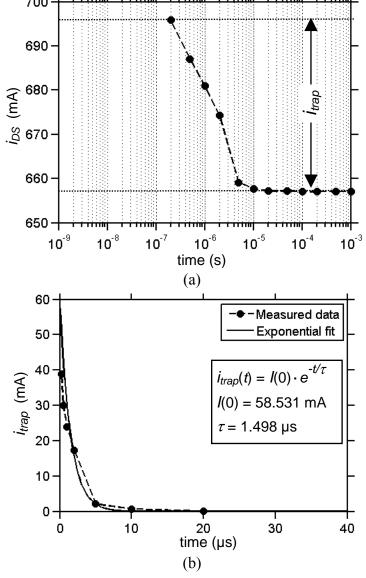

| <b>Figure 6.23</b> | (a) Measured $i_{DS}$ transient used to extract $R_{GT} \cdot C_{GT}$ of the 3.2-mm                                                                          |     |

|                    | device, highlighting the $i_{trap}$ component related to the dominant                                                                                        |     |

|                    | trapping effect. (b) Separated $i_{trap}$ (dashed dot-marked lines) and the                                                                                  |     |

|                    | employed exponential fit (solid line). The initial and <i>pulsed-to</i>                                                                                      |     |

|                    | quiescent bias points were illustrated in Figure 6.21(b).                                                                                                    | 185 |

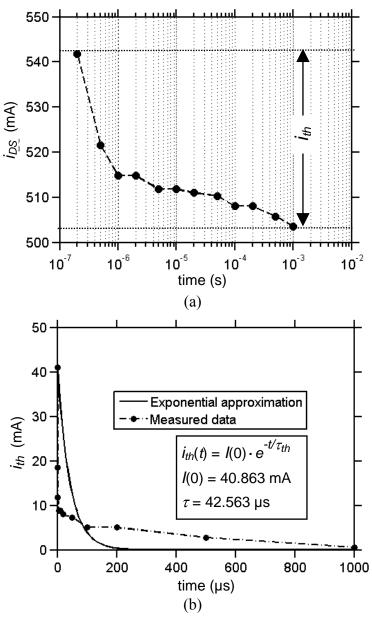

| Figure 6.24        | (a) Measured $i_{DS}$ transient used to extract $\tau_{th}$ of the 2-mm Nitonex <sup>®</sup>                                                                 |     |

|                    | device, highlighting the $i_{th}$ component related to the self-heating                                                                                      |     |

|                    | effect. (b) Separated $i_{th}$ (dashed dot-marked lines) and the                                                                                             |     |

|                    | exponential fit applied (solid line).                                                                                                                        | 186 |

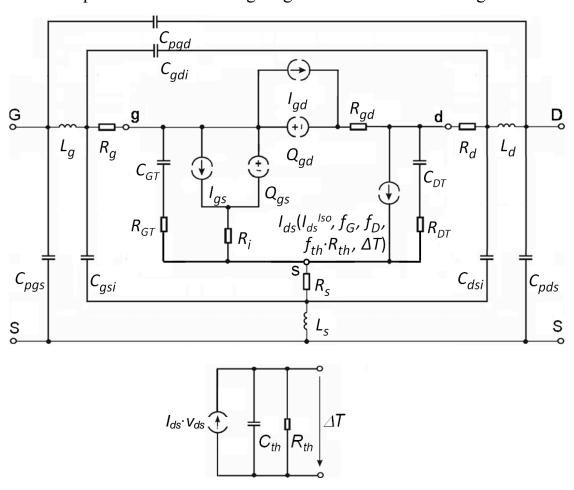

| Figure 7.1         | Complete circuit representation of the large-signal model proposed                                                                                           |     |

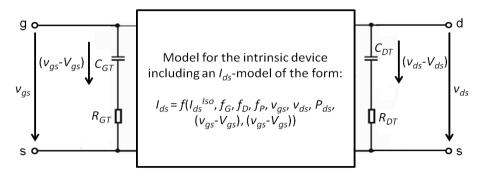

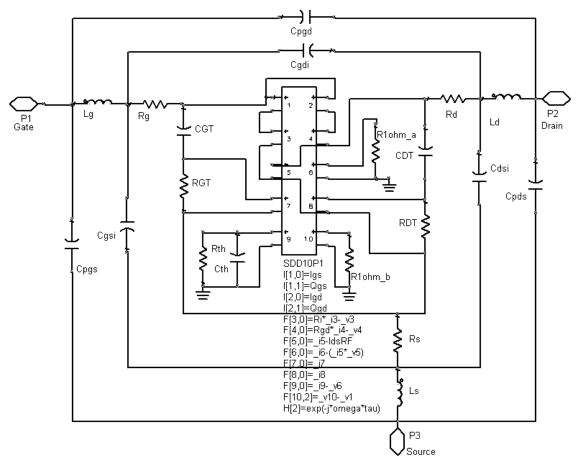

|                    | in this thesis work.                                                                                                                                         | 188 |

| Figure 7.2         | Implementation of the intrinsic part of the large-signal model with a                                                                                        |     |

|                    | 12-port SDD in the ADS <sup>®</sup> schematic                                                                                                                | 189 |

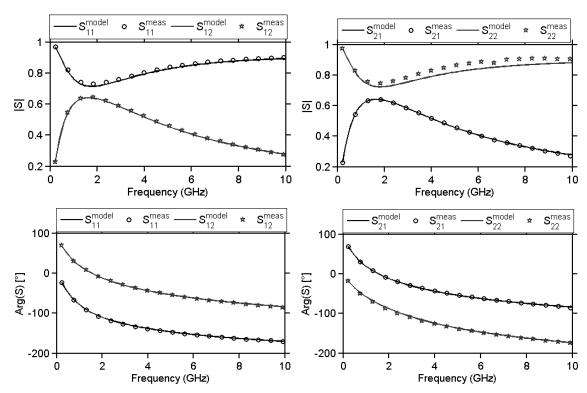

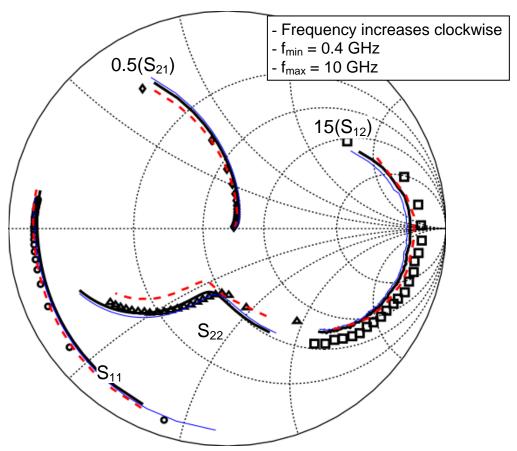

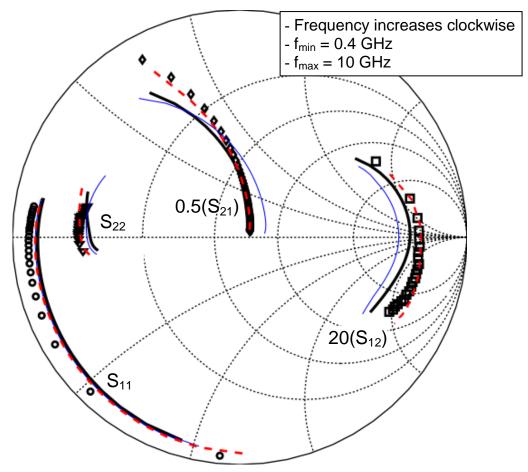

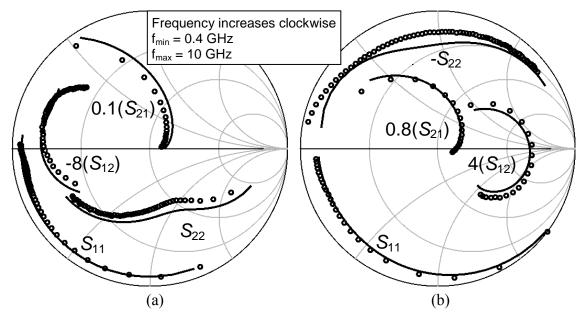

| Figure 7.3         | •                                                                                                                                                            |     |

|                    | simulations obtained with the large-signal model (lines) for bias                                                                                            |     |

|                    | points (a) in the saturation region, $V_{GS} = -3.2V$ , $V_{DS} = 30V$ , and (b)                                                                             | 101 |

| T-1                | near the pinch-off region, $V_{GS} = -3.6$ V, $V_{DS} = 55$ V                                                                                                | 191 |

| Figure 7.4         | S-parameter measurements of the 2-mm device (circles) and                                                                                                    |     |

|                    | simulations obtained with the large-signal model (lines) for bias                                                                                            |     |

|                    | points (a) in the ohmic region, $V_{GS} = -1.1V$ , $V_{DS} = 5V$ , and (b) in the                                                                            | 101 |

| Figure 7.5         | high- $V_{GS}$ low- $V_{DS}$ region, $V_{GS} = +0.2$ V, $V_{DS} = 4$ V.                                                                                      | 191 |

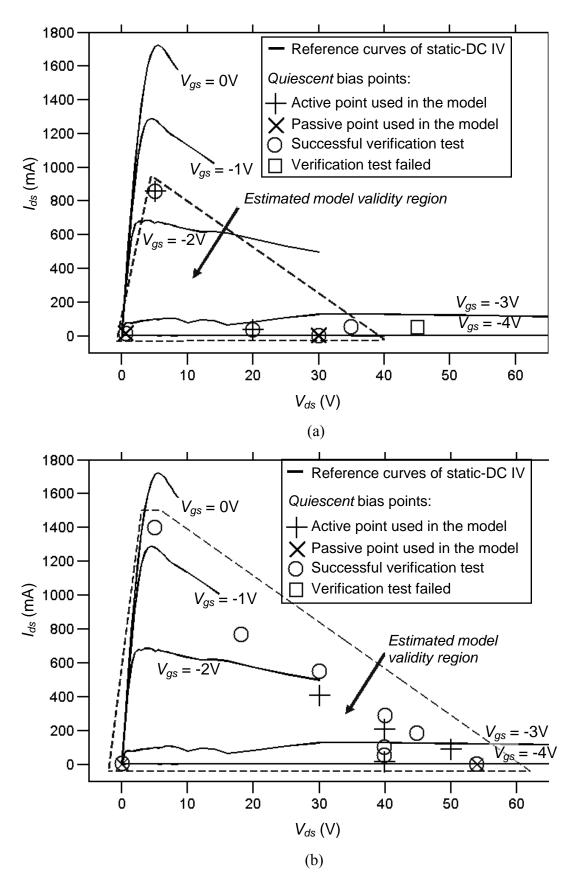

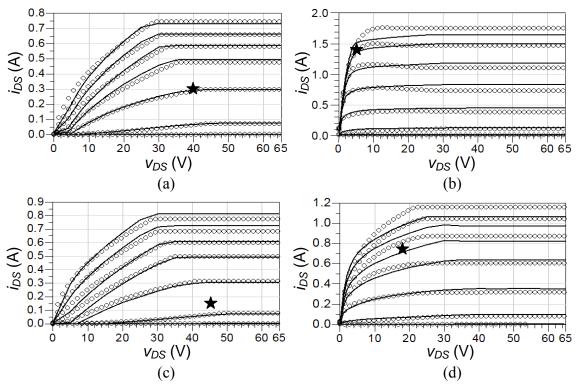

| rigure /.5         | Pulsed-DC IV measurements (circles) and simulations (lines) of the                                                                                           |     |

|                    | 3.2-mm device on the <i>quiescent</i> bias points (stars): (a) $V_{GS} = -2.7V$ ,                                                                            |     |

|                    | $V_{DS} = 40 \text{V}$ , $I_{DS} = 0.3 \text{A}$ , (b) $V_{GS} = -1 \text{V}$ , $V_{DS} = 5 \text{V}$ , $I_{DS} = 1.4 \text{A}$ , (c) $V_{GS} = -1 \text{V}$ |     |

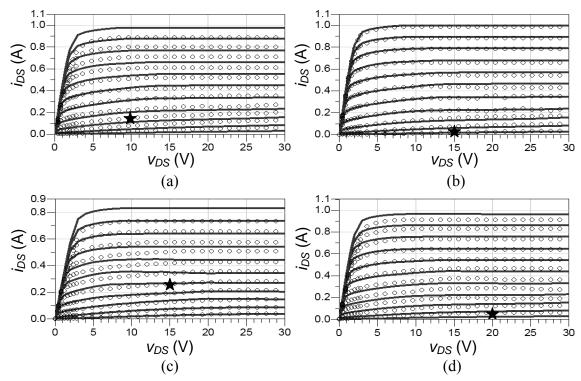

| = -3.1V, $V_{DS}$ = 45V, $I_{DS}$ = 0.15A and (d) $V_{GS}$ = -1.7V, $V_{DS}$ = 18V, $I_{DS}$                                  |                                                            |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

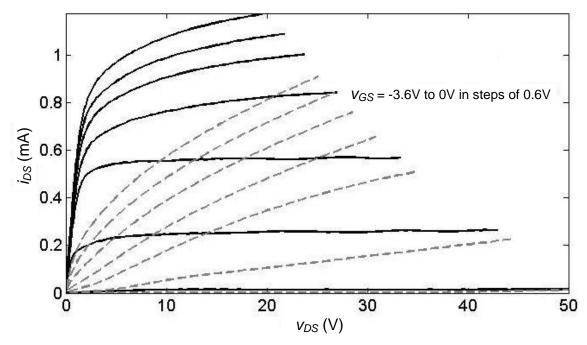

| = 0.76A. $v_{GS}$ curves from -3.6V to 0V in steps of 0.6V                                                                    | . 193                                                      |

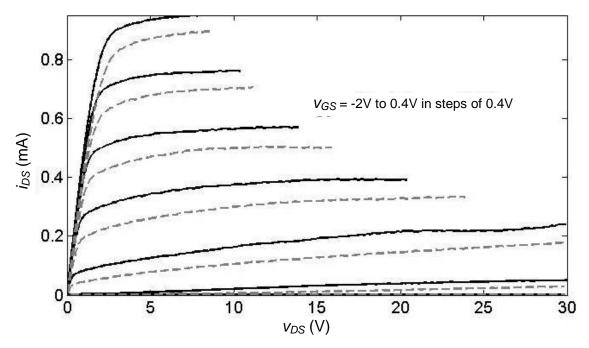

| Pulsed-DC IV measurements (circles) and simulations (lines) of the                                                            |                                                            |

| 2-mm device on the <i>quiescent</i> bias points (a) $V_{GS} = -1.2V$ , $V_{DS} =$                                             |                                                            |

| 10V, $I_{DS} = 0.12$ A, (b) $V_{GS} = -1.5$ V, $V_{DS} = 15$ V, $I_{DS} = 0.036$ A, (c) $V_{GS}$                              |                                                            |

| = -0.9V, $V_{DS}$ = 15V, $I_{DS}$ = 0.23A and (d) $V_{GS}$ = -1.5V, $V_{DS}$ = 20V, $I_{DS}$                                  |                                                            |