An Enhanced Quasi-Monolithic Integration Technology for Microwave and Millimeterwave Applications

Mojtaba Joodaki

Die vorliegende Arbeit wurde vom Fachbereich Elektrotechnik - der Universität Kassel als Dissertation zur Erlangung des akademischen Grades eines Doktor-Ingenieurs (Dr.-Ing.) angenommen.

Erster Gutachter: Prof. Dr.-Ing. G. Kompa Zweiter Gutachter: Prof. Dr. H. Hillmer

Tag der mündlichen Prüfung

28. April 2003

Bibliografische Information Der Deutschen Bibliothek Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.ddb.de abrufbar

Zugl.: Kassel, Univ., Diss. 2003 ISBN 3-89958-010-9

© 2003, kassel university press GmbH, Kassel www.upress.uni-kassel.de

Umschlaggestaltung: 5 Büro für Gestaltung, Kassel Druck und Verarbeitung: Unidruckerei der Universität Kassel Printed in Germany To my Parents

for their love and kindness

## **Acknowledgement:**

There are many people who contributed to this work. Foremost among them is my supervisor, Prof. Dr.-Ing. Günter Kompa, who provided a careful balance of guidance, support, and the resources and encouragement during this dissertation. None of this work would have been possible without his diligent support. Thanks to my colleagues and members of the department of High Frequency Engineering for their friendship and all of their helps over the past three years.

I would specially like to thank Prof. Dr. Hartmut Hillmer for his permanent and valuable considerations and support. Most of the practical parts of this work have been done using the facilities at department of Technological Electronics and with assistances of the department's members in a friendly atmosphere, which I really appreciate.

Many thanks are directed to Prof. Dr. Rainer Kassing and members of the department of Technological Physics for their unsparing support throughout this project. I want to express my gratitude to Dr. Ivo Rangelow and members of the Institute of Microsystems Technology at Wroclaw University of Technology for their excellent cooperation and performing the sophisticated thermal imaging. I thank Dr. Wenzel Scholz who provided me with technological advices and many helps during the fabrication processes.

My thanks go to Prof. Dr. Klaus Röll and Dr. Klaus Thoma who provided me with sputtering facilities at the department of Experimental Physics IV.

This work has been done within a project of Material and Components of Microsystems Technology, which was supported by German Research Community (DFG). I would like to express my appreciation to DFG for granting me a scholarship to pursue my studies at department of High Frequency Engineering at University of Kassel.

Finally, I wish to thank the SPIE for awarding me the F-Made scholarship of 2002 and for their financial supports to visit some conferences, the GaAs Application Symposium Association (GAAS) for granting me the GAAS Graduate Fellowship of 2001 and 2002, IEEE and Motorola Inc. for the student paper award during ECTC 2001.

Mojtaba Joodaki

# Contents

|   | ABSTRACT                                                               | IX   |

|---|------------------------------------------------------------------------|------|

|   | ZUSAMMENFASSUNG                                                        | XIII |

|   | LIST OF FIGURES                                                        | XVII |

|   | LIST OF TABLES                                                         | XX   |

|   | FREQUENTLY USED NOMENCLATURES                                          | XXI  |

| 1 | INTRODUCTION                                                           | 1    |

|   | 1.1 RF and microwave packaging and position of the enhanced QMIT       | 3    |

|   | 1.1.1 Single-chip packaging.                                           |      |

|   | 1.1.2 Multi chip module                                                |      |

|   | 1.1.3 The first assembly technologies                                  |      |

|   | 1.2 The earlier concept of QMIT                                        |      |

|   | 1.2.1 General                                                          |      |

|   | 1.2.2 The fabrication process and other possible structures            | 8    |

|   | 1.2.3 The attained state of the art and further requirements           |      |

|   | 1.3 Research objectives                                                |      |

|   | 1.3.1 Overview of the dissertation chapters                            | 13   |

| 2 | TECHNOLOGICAL ISSUES AND MATERIAL PROPERTIES                           | 15   |

|   | 2.1 Introduction.                                                      | 15   |

|   | 2.2 Available substrates for MCM technology for microwave applications | 16   |

|   | 2.2.1 Alumina and glass alumina                                        | 16   |

|   | 2.2.2 Beyllium oxide                                                   | 16   |

|   | 2.2.3 Aluminum nitride                                                 | 17   |

|   | 2.2.4 Soft substrate                                                   | 17   |

|   | 2.2.5 GaAs                                                             | 17   |

|   | 2.2.6 Silicon                                                          | 17   |

|   | 2.3 Copper on low dielectric interlayer interconnect technology        | 18   |

|   | 2.4 Fundamentals of semiconductor technology used                      | 20   |

|   | 2.4.1 Micromachining                                                   | 20   |

|   | 2.4.2 Thin-film technology                                             | 23   |

|   | 2.4.3 Photolithography                                                 | 25   |

|   | 2.4.4 Gold electroplating                                              | 29   |

|   | 2.5 Materials involved properties                                      | 29   |

| 3 | THE ENHANCED QUASI-MONOLITHIC INTEGRATION TECHNOLO                     | GY31 |

|   | 3.1 Introduction                                                       | 31   |

|   | 3.2 The novel fabrication processes                                    | 31   |

| 3.2.1 Fabrication process for the coplanar circuit realization          | 32      |

|-------------------------------------------------------------------------|---------|

| 3.2.2 Fabrication process for microstrip circuit realization            |         |

| 3.3 Electrical characteristics of an embedded p-HEMT in the enhanced Q  | )MIT 35 |

| 3.4 Advantages of the enhanced QMIT                                     | 38      |

| 3.5 Summary                                                             | 39      |

| 4 STATIC THERMAL ANALYSIS AND MANAGEMENT                                | 41      |

| 4.1 Introduction                                                        | 41      |

| 4.2 Influence of temperature on reliability                             | 43      |

| 4.3 Influence of temperature on electronic properties of active devices | 43      |

| 4.3.1 Influence of temperature on material factors of GaAs              | 43      |

| 4.3.2 Influence of temperature on the electron drift velocity and mobil | ity 44  |

| 4.4.3 Influence of temperature on threshold voltage                     | 45      |

| 4.4.4 Influence of temperature on noise figure                          | 45      |

| 4.4 A survey of finite element method                                   | 46      |

| 4.5 Basics of heat transfer analysis                                    | 48      |

| 4.6 Static heat transfer analysis in the earlier QMIT structures        | 50      |

| 4.6.1 Simulation result for the power GaAs-MESFET used                  | 50      |

| 4.6.2 Simulation results for different structures                       | 51      |

| 4.6.4 Effect of epoxy                                                   | 53      |

| 4.6.5 Effect of heat spreader                                           | 54      |

| 4.6.6 Comparison of the optimum structure with standard GaAs-MMI        | Cs 55   |

| 4.7 Static heat transfer analysis in the enhanced QMIT structure        | 56      |

| 4.7.1 Comparison of the hottest points in the earlier and enhanced QM   | IT 57   |

| 4.8 Thermal imaging of microwave power GaAs-FET                         | 58      |

| 4.8.1 Experimental and calculated results                               | 60      |

| 4.8 Summary                                                             | 64      |

| 5 THERMO-MECHANICAL STRESS ANALYSIS AND MEASUREME                       | NT 65   |

| 5.1 Introduction                                                        | 65      |

| 5.2 Effect of mechanical stress on packaging reliability and lifetime   |         |

| 5.2.1 Reliability overview                                              |         |

| 5.2.2 Mechanical fracture                                               |         |

| 5.2.3 Fatigue                                                           | 75      |

| 5.3 Stress (strain) effects on electronic properties of semiconductors  |         |

| 5.3.1 Stress effects on the energy band-gaps                            |         |

| 5.3.2 Stress effects on the carrier densities                           |         |

| 5.3.3 Stress effects on the carrier mobility                            |         |

| 5.4 Thermo-mechanical stress in the earlier concept of QMIT             |         |

| 5.4.1 Principle of the applied approach                                 |         |

| 5.4.2 Modeling of the standard structure of earlier concept of QMIT      | 80     |

|--------------------------------------------------------------------------|--------|

| 5.4.3 Thermo-mechanical stress analysis in the standard structure        | 80     |

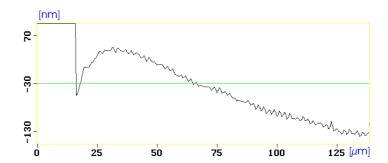

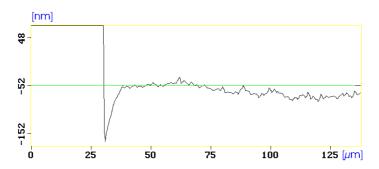

| 5.4.4 The measured displacement distributions in the standard structure  | 83     |

| 5.4.5 Comparison of the calculated and measured induced displacement     | 87     |

| 5.5 Thermo-mechanical stress in the enhanced QMIT                        | 88     |

| 5.5.1 Thermo-mechanical stress analysis                                  | 88     |

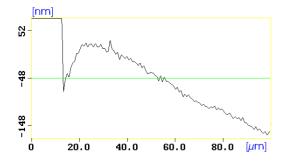

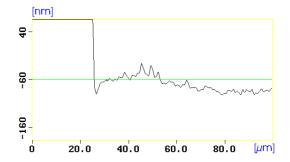

| 5.5.2 The measured displacement distributions                            | 90     |

| 5.5.3 Comparison of the calculated and measured induced displacement     |        |

| 5.6 Comparison of maximum thermo-mechanical stress in the QMIT structure |        |

| 5.7 Summary                                                              | 94     |

| 6 A RELIABLE NEURAL MODEL FOR P-HEMT IN THE ENHANCED QN                  | 1IT 95 |

| 6.1 Introduction                                                         | 95     |

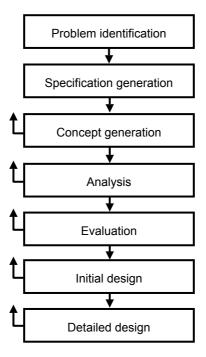

| 6.2 RF and microwave designs and position of the neural modeling         | 96     |

| 6.2.1 Modeling of RF and microwave circuits and devices                  |        |

| 6.2.2 Role of neural modeling                                            | 98     |

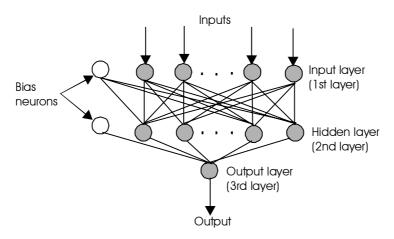

| 6.3 Fundamental of multilayer perceptrons type neural networks           | 99     |

| 6.4 Principle of the approach                                            | 102    |

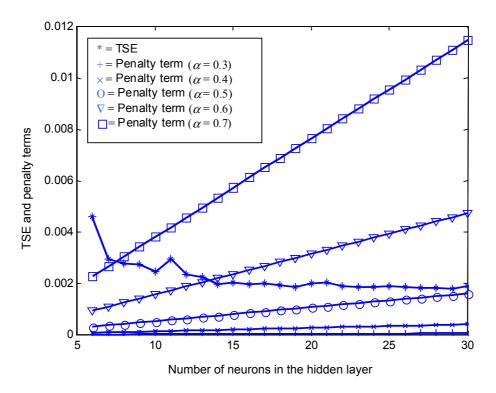

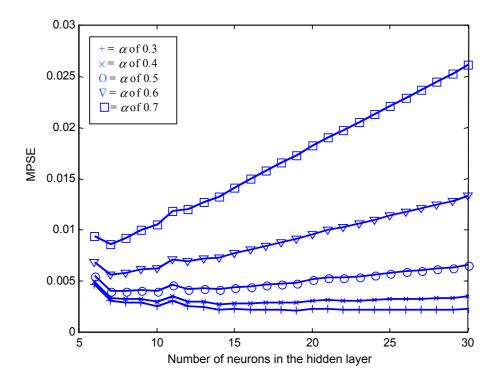

| 6.5 Method for training and evaluation of the neural model               | 103    |

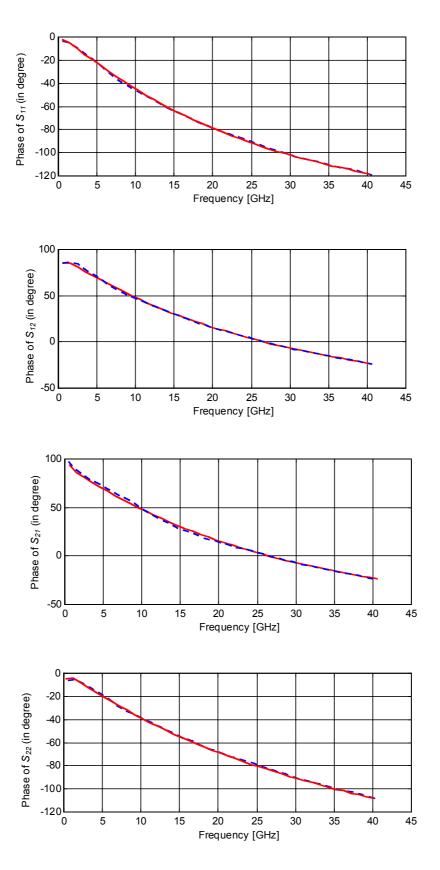

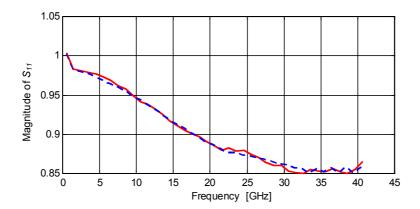

| 6.6 Model development and results for p-HEMT on a standard test-fixture  | 105    |

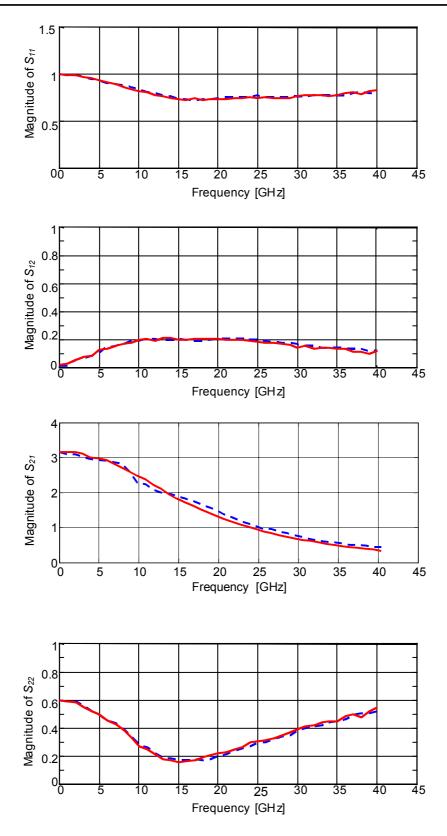

| 6.7 Model development and results for p-HEMT in the enhanced QMIT        | 106    |

| 6.8 Summary                                                              | 109    |

| 7 CONCLUSION AND FUTURE PROSPECTS                                        | 111    |

| 7.1 Conclusion                                                           | 111    |

| 7.2 Future prospects                                                     | 113    |

| References:                                                              | 115    |

| PUBLICATIONS:                                                            | 127    |

| Curriculum vitae.                                                        | 131    |

#### **Abstract**

RF/Microwave technology is shifting from large centralized and long range systems (with a large RF transmit power) to smaller distributed and shorter range systems (with relatively modest RF power) and also many new smaller systems must be mobile or hand-held. Trend in RF design is to shift from premium devices to more affordable and integrable technology, which gives a greater degree of RF functionality per unit volume.

In this way RF, microwave and millimeterwave packaging is becoming more and more important considering the significant growth of commercial and military applications in wireless communication and sensing. Huge changes are underway in wireless communications and consumer electronics. Excellent representations of these are handheld devices that have real-time Internet access, video, voice and sensing capability.

Packaging strongly affects performance, cost, reliability and lifetime and it is a determining factor in the growth of these applications. Generally, wireless subsystems consist of different components such as high frequency transceivers, digital processors and may include microelectromechanical systems (MEMS). Microwave transceivers are composed of both integrated circuits (ICs) and passive devices including filters and power combiners that are not integrated on the semiconductor substrate. These components are based on different materials and technologies.

On the other hand, in the past decades, there have been tremendous improvements in fabrication and characteristics of electronic devices and MEMS, and many new components have been invented. The development of III-V compound semiconductors such as GaAs, InP, and related ternary compounds has permitted microwave and millimeterwave devices with excellent noise and power performance to be developed. The progress has been rapid due to advances in both fabrication technology and materials. Today, RF performance of field-effect transistors extends well into the millimeterwave region, and frequency response greater than 300 GHz has been reported for the InP-based compound semiconductor HEMT. RF micromachining and MEMS have been identified as a technology that has the potential to make a major impact on existing RF architectures in sensors (radar) and communications by reducing weight, cost, size and power dissipation.

Thus, the necessary technologies are now mature and available, opening a wide field of deployment areas. These have provided us with many high performance components, which should be integrated and packaged without hindering their performance. All of these advanced features confirm required shifts in microwave packaging to address integration of a system-on-a-package (SOP).

The multilayer organic multi chip module (MCM) is a potential candidate for integration an SOP at microwave and millimeterwave frequencies. This technology has been utilized to package high-speed memory ICs and transceivers for communications, and packaging of MEMS devices in this technology has been recently demonstrated.

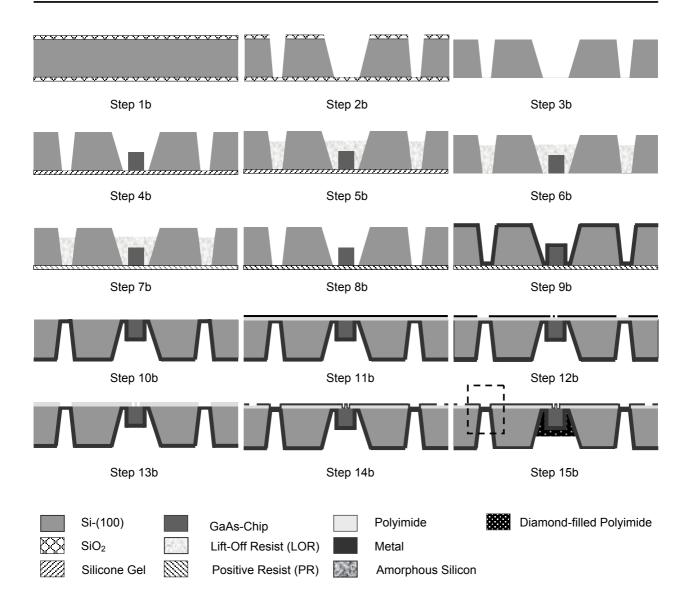

In this dissertation two different structures for earlier concept of quasi-monolithic integration technology (QMIT) have been introduced and along with the standard structure of QMIT, proposed by Wasige [122], have been investigated in details and further required developments have been addressed. To fulfill these requirements and reach a flexible technology owning several advantages, two new fabrication processes for QMIT named the enhanced QMIT for the coplanar and microstrip circuit realizations have been introduced. The enhanced QMIT can be considered as an organic deposited MCM, which uses common thin-film interconnection for the first level of packaging (device-to-package) for RF, microwave and millimeterwave applications.

In the enhanced QMIT large-area high-Q passive elements can be fabricated on a low cost silicon substrate covered by organic multiplayer dielectrics. Beside many other advantages such as small size and weight, good lifetime and reliability, capability of MCM integration, using active devices based on different materials, good control of parasitic elements, compatibility with coplanar waveguides without using thin devices and broad-band performance, the extremely low thermal resistance and direct electrical interconnects to the embedded active devices giving minimum parasitic effects, are unique advantages of this technology.

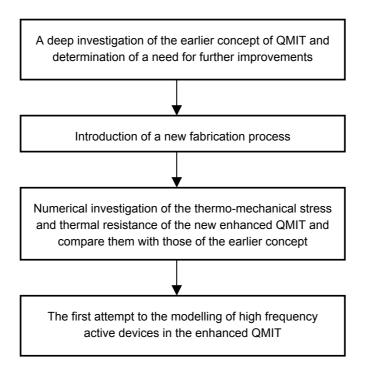

The body of this dissertation contains six chapters followed by a chapter of conclusion. In the first chapter after introduction to RF and microwave packaging and determining the position of the enhanced QMIT, the earlier concept of QMIT and its shortcomings are described. In the chapter 2, technological issues and material properties are discussed.

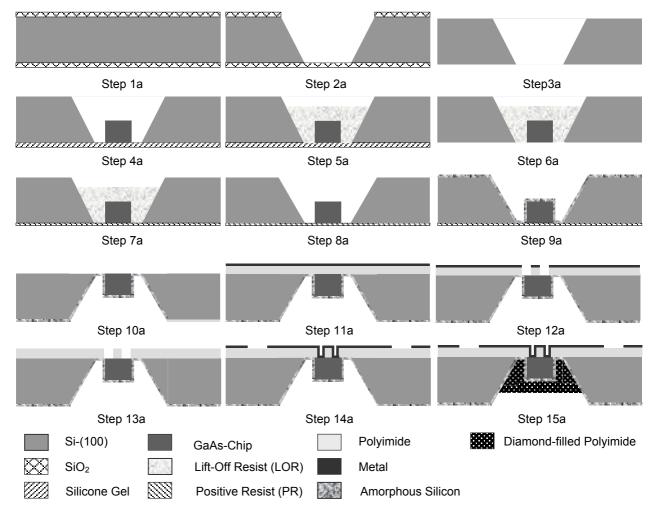

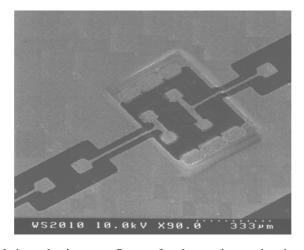

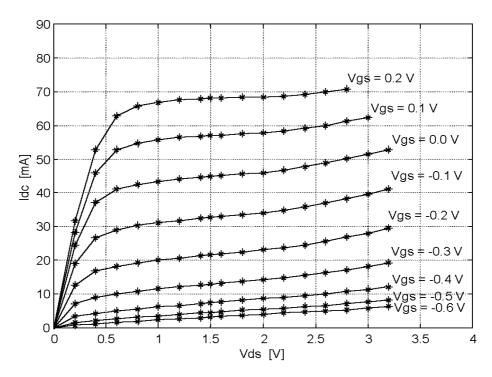

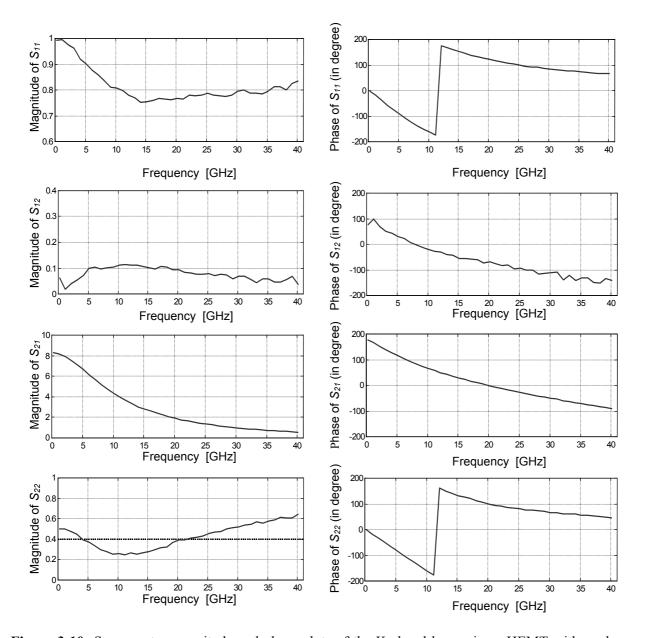

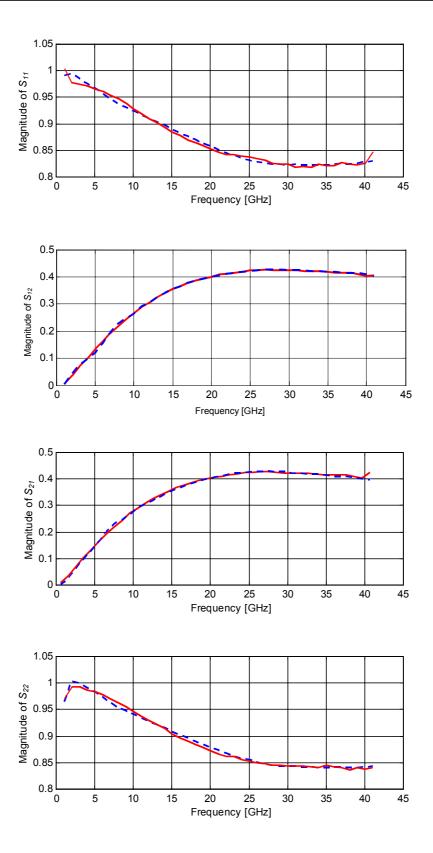

Chapter 3 covers the novel fabrication process, electrical characteristics of the embedded active devices in this technology and advantages of the new technology. The new technology not only fulfils the requirements for high frequency design, but also is cost effective, reliable and reproducible. Two fabrication processes for coplanar and microstrip realizations are introduced. To confirm the fabrication processes, a low noise Ka-band GaAs-based AFP02N3 p-HEMT and a power GaAs-based AFM08P2 MESFET from Alpha Industries were successfully integrated into a silicon substrate and the microwave characteristics of the low noise p-HEMT measured up to 40 GHz using an HP 8510B network analyzer.

To optimize the new structure and material properties, investigate the reliability and lifetime of the packaging and achieve an accurate model for the active devices in this technology, the thermal and thermo-mechanical stress simulations and measurements in

the earlier concept and enhanced QMIT and neural modeling of microwave active devices in the enhanced QMIT were performed in detail in chapters 4, 5 and 6, respectively.

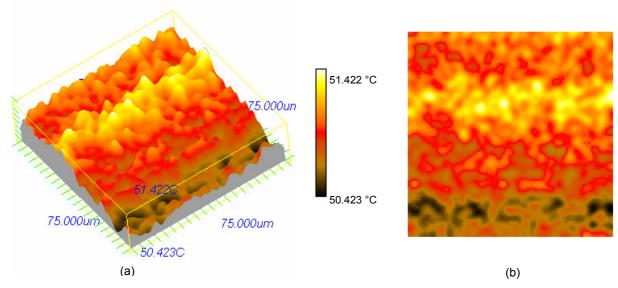

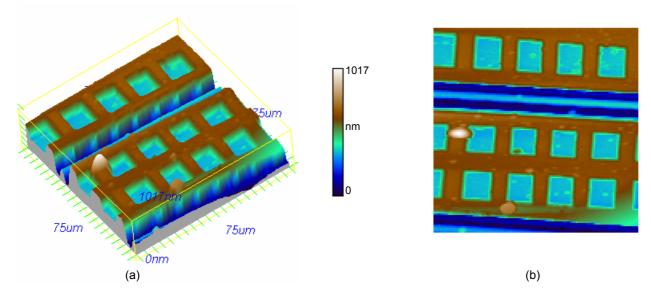

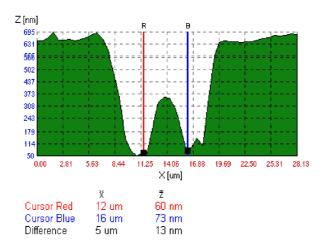

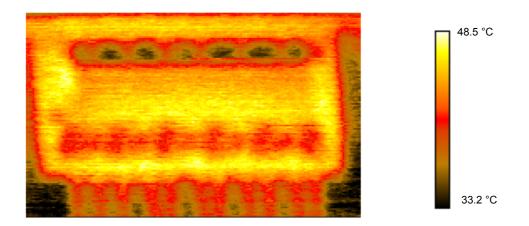

To confirm the thermal simulation results and the transistor model used in chapter 4, the first successful application of a thermal nano-probe integrated into a piezoresistive atomic force microscopy (AFM) cantilever for two-dimensional thermal imaging of microwave active devices has been presented. Near-field, infrared measurement and nonlinear three-dimensional simulation have been performed for a KT1305T power UHF-band GaAs-MESFET of from OKI Electronic Components. The simulation and measurements confirm the high capability of the thermal nano-probe for these applications.

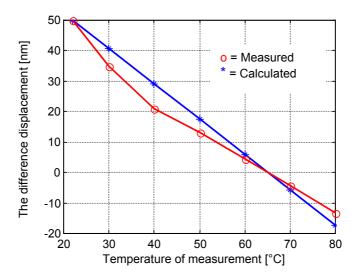

A novel method to achieve the thermo-mechanical stress distribution under different temperatures for the different QMIT structures has been discussed. A closed-loop temperature measurement system consisting of a Pt-100 temperature sensor, a Peltier-element and a digitally controlled current source implemented allowing temperature measurements with a resolution of better than 0.1 °C. The surface profiles on the silicon substrate around the active devices have been measured using scanning probe microscopy (SPM), DEKTAK or white-light interferometery. Great agreement between calculated and measured results was demonstrated. In comparison with the earlier concept, the simulation results confirm an excellent thermal resistance and a much lower induced thermo-mechanical stress for the enhanced QMIT.

Further, as a first attempt to the modeling of high frequency active devices in the QMIT environment, a systematic approach is presented to achieve a reliable neural model for microwave active devices with a different number of training data used for training the neural network. The method is implemented for a small-signal bias dependent modeling of p-HEMT (AFP02N3 from Alpha Industries) in two different environments: on a standard test-fixture and in the enhanced QMIT. The errors for different number of training data have been compared and show that by using this method a reliable model is achievable even though the number of training data is considerably small. The method aims at constructing a model, which can satisfy the criteria of minimum training error, maximum smoothness and simplest neural network structure.

## Zusammenfassung

Trends in der heutigen Mikrowellentechnik sind dadurch gekennzeichnet, daß große zentral gelegene und weitreichende Systeme (mit einer hohen Sendeleistung) durch kleinere verteilte Nahbereichssysteme (mit relativ geringen Hochfrequenzleistungen) ersetzt werden. Weiterhin müssen diese kleineren Einheiten vielfach mobil und handgerecht sein. Die Entwicklung erfordert im allgemeinen eine Steigerung der Leistungsfähigkeit der erforderlichen Bauelemente und eine Integrationstechnologie, die einen höheren Grad an Funktionalität pro Volumeneinheit ermöglicht.

In diesem Zusammenhang erlangt das Packaging von Mikrowellen- und Millimeterwellen-Bauelementen und Schaltkreisen wachsende Bedeutung für kommerzielle und militärische Anwendungen in Bereichen der Funkübertragung und Hochfrequenzsensorik. Große Fortschritte werden heutzutage in der drahtlosen Kommunikationstechnik und im Bereich der Konsumerelektronik sichtbar. Wichtige Beispiele hierfür sind Handgeräte, die einen Echtzeit-Internetzugang haben, Video- und Tonübertragung ermöglichen und sensorische Fähigkeiten aufweisen.

Das Packaging beeinflusst insbesondere Leistung, Kosten, Zuverlässigkeit und Lebensdauer, und ist somit ein entscheidender Faktor in der Entwicklung dieser Geräte. Normalerweise bestehen drahtlose Übertragungssysteme aus verschiedenen Elementen wie z.B. einer Sende-/Empfangseinheit, Digitalprozessoren und gegebenenfalls auch mikroelecktromechanishe Systems (MEMS). Mikrowellen-Sende-/Empfangseinheiten bestehen aus integrierten Schaltungen (ICs) und passiven Elementen (u.a. Filter und Leistungsteiler), die nicht auf dem Substrat integriert sind. Diese Komponenten bestehen aus verschiedenen Materialien und Technologien.

Weiterhin wurde in der letzten Dekade ein bedeutender Fortschritt in der Herstellung und Charakterisierung von elektronischen Bauelementen und MEMS erzielt, und viele neue Komponenten eingeführt. Durch die Entwicklung von III-V Halbleitern wie z.B. GaAs, InP und entsprechende ternäre Halbleitermaterialien wurden Mikrowellen- und Millimeterwellenbauelemente mit exzellenten Rausch- und Leistungseigenschaften entwickelt Diese raschen Forschritte basieren auf der Entwicklung neuer Herstellungstechniken und Materialien. Heute erzielen Feldeffekttransistoren beträchtliche Hochfrequenzleistungen im Millimeterwellenbereich; es konnte mit einem InP-basierten HEMT eine Frequenzantwort oberhalb von 300 GHz erzielt werden. Hochfrequenz-Mikromechanik (RF micromachining) und **MEMS** Technologien erachtet, die in sich das Potenzial tragen, einen maßgeblichen Einfluss auf bestehende Hochfrequenz-Architekturen im Bereich der Sensorik (Radar) Kommunikationstechnik durch Reduzierung von Gewicht, Kosten, Größe und Verlustleistung auszuüben.

Die notwendigen Technologien sind nun entwickelt und verfügbar, und öffnen somit ein weites Feld von Anwendungsgebieten. Sie haben uns zahlreiche leistungsfähige Komponenten zur Verfügung gestellt: Diese sollten dann ohne Einbuße hinsichtlich ihrer Leistungsdaten integriert und gehäust werden können. All diese fortschrittlichen Aspekte führen zu einer neuen Sichtweise des Mikrowellen-Packaging, nämlich der Realisierung eines Systems in einem Gehäuse (system-on-a-package (SOP)).

Die Technologie der organischen Mehrschicht-Multichip-Module (MCM) ist eine potentielle Möglichkeit, eine SOP-Komponente bei Mikrowellen- und Millimeterwellenfrequenzen herzustellen. Die Technologie wurde verwendet, um Hochgeschwindigkeitsspeicher-ICs und Transceiver für Kommunikationszwecke aufzubauen sowie MEMS zu integrieren.

In der vorliegenden Dissertation werden zwei verschiedene Strukturen nach dem herkömmlichen Konzept der quasi-monolithischen Integrationstechnologie (QMIT) vorgestellt und zusammen mit der QMIT-Standardstruktur von Wasige [122] im Detail untersucht und weitere erforderliche Verbesserungen durchgeführt. Um diese Erfordernisse zu erfüllen und eine flexible Technologie mit besonderen Vorteilen zu realisieren, wurden neue verbesserte QMIT-Herstellungstechniken für Schaltkreisrealiserungen in Koplanar- and Mikrostreifenleitungstechnik verfolgt. QMIT kann als organisches abgeschiedenes MCM angesehen werden, welches Dünnfilm-Verbindungen für das erste Niveau des Packaging verwendet.

Mit dem verbesserten QMIT-Prozeß können großflächige Elemente hoher Güte auf preisgünstigem Siliziumsubstrat hergestellt werden, die mit organischem Dielektrikum bedeckt werden. Neben anderen Vorteilen wie Größe, Gewicht, hohe Lebensdauer, Zuverlässigkeit, Fähigkeit der MCM-Integration, Verwendbarkeit aktiver Elemente aus verschiedenen Materialien, gute Kontrolle über die parasitären Elemente, Kompatibilität zu Koplanarleitungen ohne Verwendung von Dünnfilm-Bauelementen sowie ihre Breitbandeigenschaft, ihr extrem niedriger thermischer Widerstand und die direkten induktionsarmen elektrischen Verbindungen zu den eingebetteten aktiven Bauelementen, dies alles sind eindeutige Vorteile dieser Technologie.

Die Abhandlung dieser Dissertation enthält sechs Kapitel, gefolgt von einem zusammenfassenden Kapitel. Im ersten Kapitel werden nach einer Einführung des Packaging im Hochfrequenz- und Mikrowellenbereich die Begriffe des verbesserten und herkömmlichen QMIT-Konzepts erläutert und ihre Nachteile beschrieben.

Kapitel 3 befasst sich mit dem neuen Herstellungsprozess, den elektrischen Eigenschaften der eingebetteten aktiven Bausteine in dieser Technologie, sowie den Vorteilen der neuen Technologie. Die neue Technologie erfüllt nicht nur die Anforderungen für hochfrequenztaugliches Design, sondern ist auch kostengünstig,

zuverlässig und reproduzierbar. Zwei Herstellungsprozesse für Koplanar- und Mikrostreifenleitungstechnik werden vorgestellt. Um die Herstellungsprozesse zu verifizieren, wird ein rauscharmer Mikrowellentransistor für das Ka-Band (GaAs AFP02Ne p-HEMT) und ein GaAs-MESFET-Leistungstransistor vom Typ AFM08P2 von Alpha Industries in ein Siliziumsubstrat integriert und die Mikrowelleneigenschaften des rauscharmen p-HEMTs bis 40 GHz mit einem HP 8510B Netzwerkanalysator gemessen.

Um die neuen Strukturen und die Materialeigenschaften zu optimieren, wurde die Zuverlässigkeit und die Lebensdauer des Packaging untersucht und ein genaues Modell des aktiven Bauelements in dieser Technologie erstellt. Thermische und Thermospannungssimulationen und Messungen wurden für eingebettete Chips nach dem verbesserten und herkömmlichen QMIT-Konzept durchgeführt und ein neuronales Modell des aktiven Mikrowellenbausteins für die verbesserte QMIT-Umgebung erstellt, was in den Kapiteln 4,5 und 6 beschrieben wird.

Zur Bestätigung der thermischen Simulationsresultate und des Transistormodells in Kapitel 4, wurde erstmals eine thermische Nanosonde erfolgreich verwendet. Diese war in den piezoresistiven Cantilever eines Atomkraftmikroskops (AFM) integriert und ermöglichte eine zweidimensionale thermisches Abtastung von aktiven Mikrowellenbauelementen. Nahfeld- und Infrarotmessungen sowie eine nichtlineare dreidimensionale Simulation wurde für einen UHF GaAs Leistungs-MESFET vom Typ KT1305T von OKI Electronic Components durchgeführt. Die Simulationen und Messungen bestätigen die vielversprechende Leistungsfähigkeit solcher thermischen Nanoproben für diese Anwendungen.

Eine neue Methode, die thermomechanische Spannungsverteilung bei verschiedenen Temperaturen zu erhalten, wurde diskutiert. Ein geschlossenes Temperaturmesssystem, bestehend aus einem Pt-100 Temperatursensor, einem Peltier-Element und einer digital kontrollierten Stromquelle, erlaubt Temperaturmessungen mit einer Auflösung von besser als 0,1 °C. Die Oberflächenprofile auf dem Siliziumsubstrat in der Umgebung des aktiven Elements wurden mit Hilfe von Abtastmikroskopie (SPM), DEKTAK oder Weißlicht-Interferometrie gemessen. Es konnte eine grosse Übereinstimmung zwischen berechneten und gemessenen Resultaten erzielt werden. Im Vergleich mit dem herkömmlichen QMIT-Konzept bestätigen die Simulationsergebnisse einen exzellenten thermischen Widerstand und eine stark verringerte thermomechanische Spannung für das verbesserte QMIT-Konzept.

Weiterhin wird erstmalig ein Ansatz vorgestellt, einen Hochfrequenztransistor in einer QMIT-Umgebung zu modellieren. Der systematische Ansatz führt zu einem zuverlässigen neuronalen Modell für aktive Mikrowellenelemente unter Verwendung einer unterschiedlichen Anzahl von Trainingsdaten zum Training des neuronalen

Netwerks. Die Methode wird für die Herleitung eines arbeitspunktabhängigen Kleinsignalmodells eines p-HEMTs (AFP02N3 von Alpha Industries) in zwei unterschiedlichen Umgebungen verwendet: in einer Standard-Testfixture und in der verbesserten QMIT-Einbettungssituation. Die Fehler bei einer unterschiedlichen Anzahl von Trainingsdaten sind gering und zeigen, dass diese Methode ein verlässliches Modell liefert, sogar dann, wenn die Anzahl der Trainingsdaten vergleichsweise gering ist. Diese Methode zielt darauf ab, ein Modell zu generieren, welches Kriterien wie minimalen Trainingsfehler, optimales Fitting der Kurven und eine einfache neuronale Netzwerkstruktur erfüllt.

# List of figures

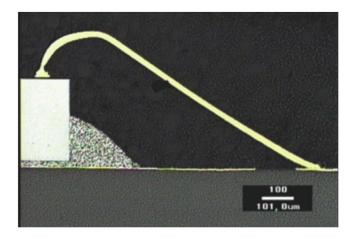

| Figure 1-1: Cross-section of wire bond between die and substrate.                                                   | 6               |

|---------------------------------------------------------------------------------------------------------------------|-----------------|

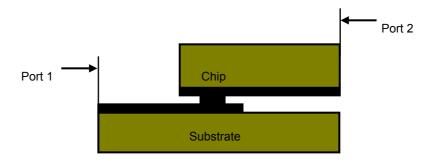

| Figure 1-2: Side-view of the bump configuration in flip-chip technology.                                            | 7               |

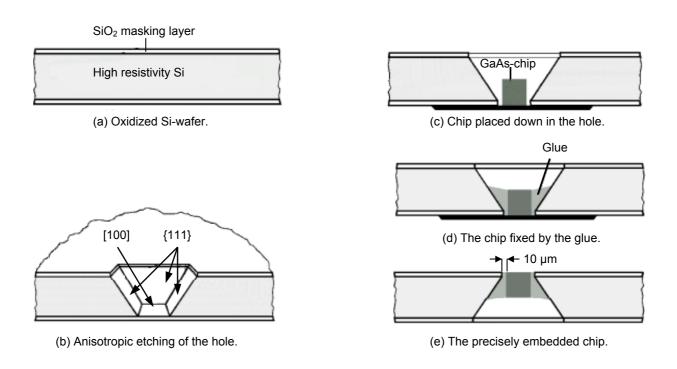

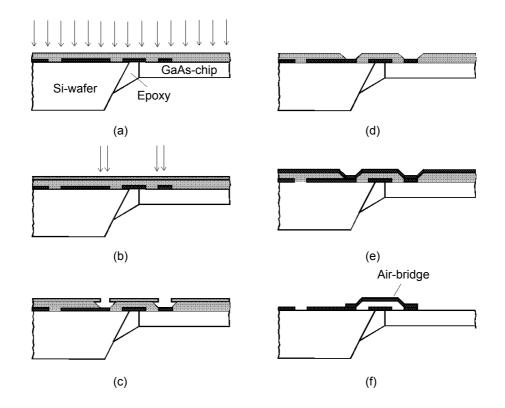

| Figure 1-3: Fabrication process for embedding the chips into the wet-etched holes in Si                             | -wafer9         |

| Figure 1-4: Fabrication process for the earlier concept of QMIT after embedding the ch                              | ips9            |

| Figure 1-5: Fabricated microtest-fixture with on-wafer probe compatible coplanar conta                              | acts10          |

| Figure 1-6: Three possible structures of the earlier concept of QMIT.                                               | 10              |

| Figure 1-7: The structure of the dissertation.                                                                      | 12              |

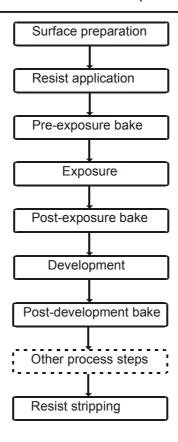

| Figure 2-1: Important steps in photoresist processing.                                                              | 26              |

| Figure 3-1: Process steps for the coplanar circuit realization in the enhanced QMIT                                 | 33              |

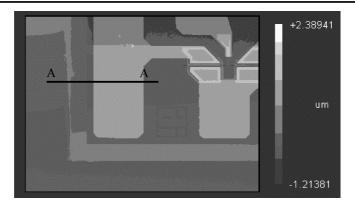

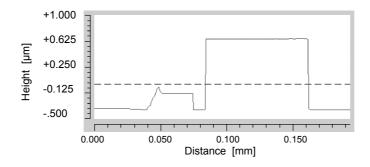

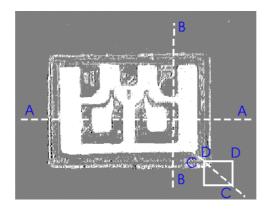

| Figure 3-2: White-light interferometery mapping a transistor fixed in the hole                                      | 34              |

| Figure 3-3: Profile measurement along the line A-A in Fig. 2-2.                                                     | 34              |

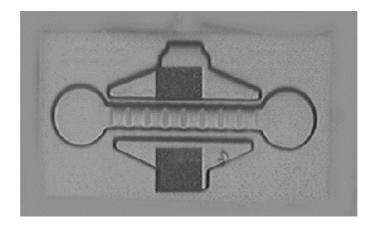

| Figure 3-4: SEM of the fabricated microtest-fixture for the coplanar circuit realization.                           | 34              |

| Figure 3-5: Process steps for the microstrip circuit realization in the enhanced QMIT                               | 36              |

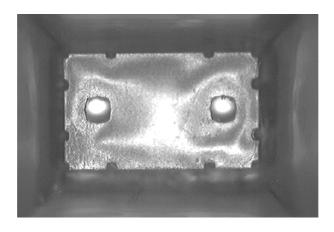

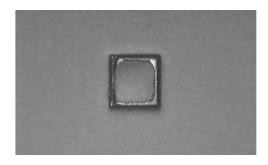

| Figure 3-6: Backside view of an embedded Ka-band power AFM08P2 GaAS-MESFET                                          | `36             |

| Figure 3-7: Front-side view of an embedded Ka-band power GaAs-MESFET after step                                     | 12b37           |

| Figure 3-8: Front-side view of the wafer on a via                                                                   | 37              |

| Figure 3-9: I-V curves of the Ka-band low noise p-HEMT in coplanar realization                                      | 37              |

| Figure 3-10: S-parameter magnitude and phase plots of p-HEMT in the new QMIT                                        | 38              |

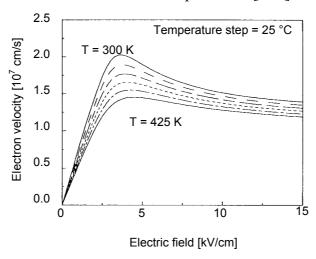

| Figure 4-1: Calculated velocity-field relationship for In <sub>0.15</sub> Ga <sub>0.85</sub> As against temperature | 45              |

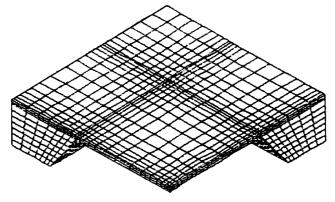

| Figure 4-2: Anisotropically etched membrane modeled with 3D solid elements in ANS                                   | YS47            |

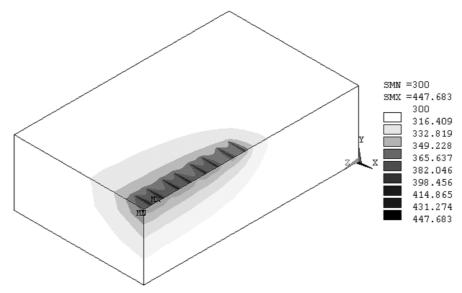

| Figure 4-3: Simulation result for a quarter of Ka-band GaAs-MESFET on a perfect hea                                 | t sink51        |

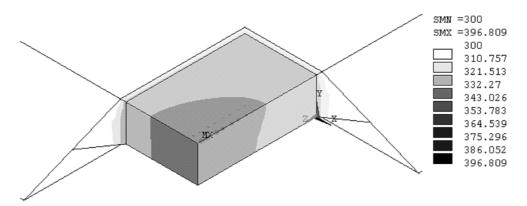

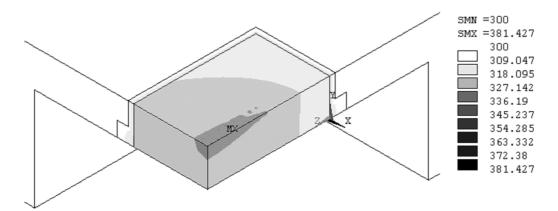

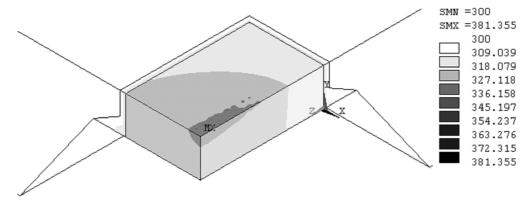

| Figure 4-4: Simulation result for a quarter of the standard structure of the earlier concept                        | ot52            |

| Figure 4-5: Simulation result for a quarter of the second structure of the earlier concept                          | 52              |

| Figure 4-6: Simulation result for a quarter of the third structure of the earlier concept.                          | 52              |

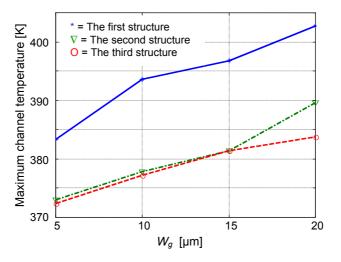

| Figure 4-7: Maximum channel temperature for all structures as a function of $W_g$                                   | 53              |

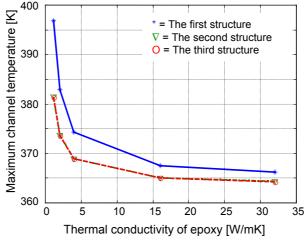

| <b>Figure 4-8:</b> Maximum channel temperature for all structures as a function of $k_{epoxy}$                      | 53              |

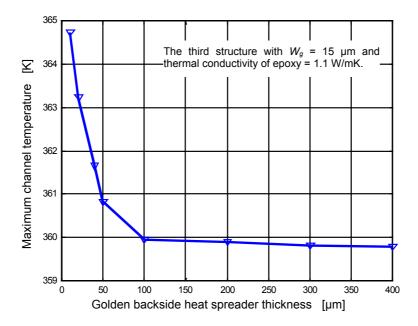

| Figure 4-9: Maximum channel temperature in the third structure as heat spreader thickr                              | iess54          |

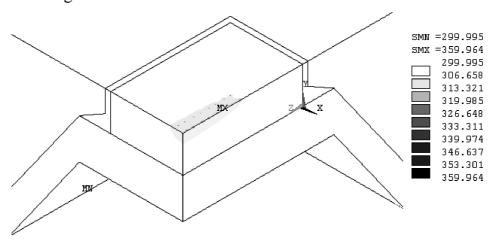

| Figure 4-10: Temperature distribution in the third structure of the earlier concept                                 | 55              |

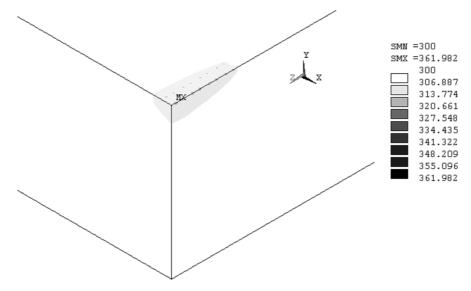

| Figure 4-11: Simulation result for the same transistor in a 375 μm thick GaAs-substrate                             | <del>;</del> 55 |

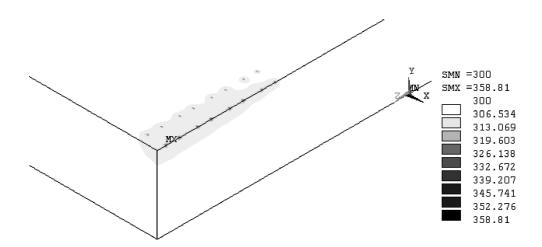

| <b>Figure 4-12:</b> Simulation result for the same transistor in a thinned 100 μm GaAs-substr                       | ate56           |

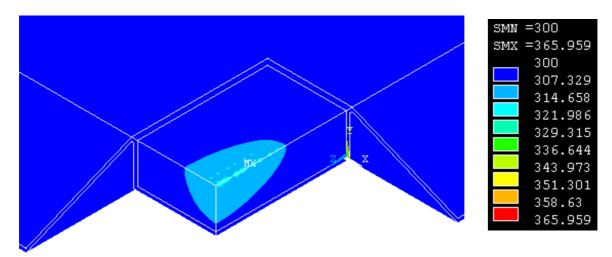

| Figure 4-13: Temperature variations for the power GaAs-MESFET in the enhanced QN                                    | ⁄IIT57          |

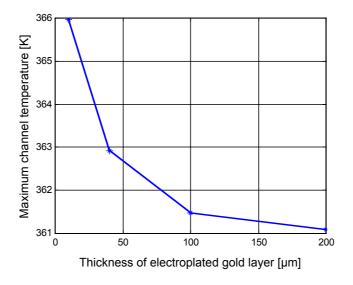

| Figure 4-14: Maximum temperature in the enhanced QMIT as gold layer thickness                                       | 57              |

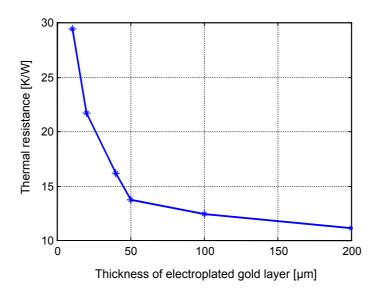

| Figure 4-15: Thermal resistance of the enhanced QMIT as gold layer thickness.                 | 58 |

|-----------------------------------------------------------------------------------------------|----|

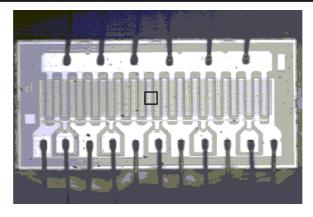

| Figure 4-16: Top view of the UHF-band power KGF1305T GaAs-MESFET from OKI                     | 61 |

| Figure 4-17: Thermal image of the 30 fingers UHF-band power GaAS-MESFET                       | 61 |

| Figure 4-18: Corresponding topographic images of the thermal imaging in Fig. 4-17             | 61 |

| <b>Figure 4-19:</b> Cross-section view of the 15 <sup>th</sup> gate region in Fig. 4-18(a)    | 62 |

| Figure 4-20: Infrared thermal imaging of the 30 fingers UHF-band power GaAS-MESFET            | 62 |

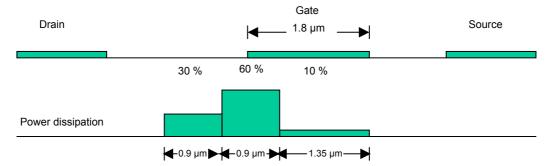

| Figure 4-21: Power dissipation percentages around the gate region.                            | 63 |

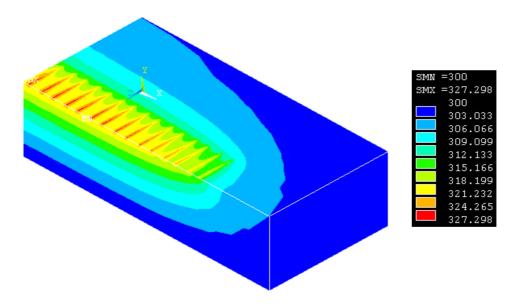

| Figure 4-22: Simulation result for the UHF-band GaAs-MESFET on a perfect heat sink            | 63 |

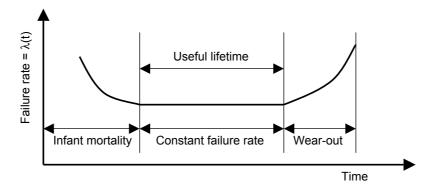

| Figure 5-1: The Bathtub curve                                                                 | 68 |

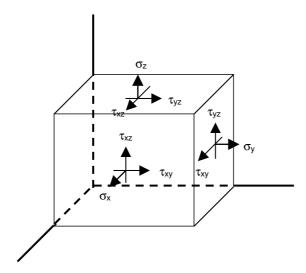

| Figure 5-2: Generalized stress states on a three-dimensional unit cube.                       | 71 |

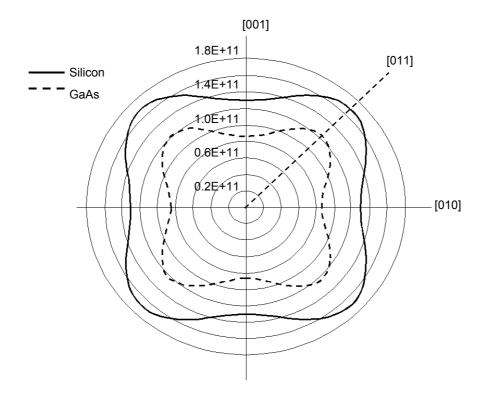

| Figure 5-3: Young's modulus as a function of crystalline orientation for Si and GaAs          | 72 |

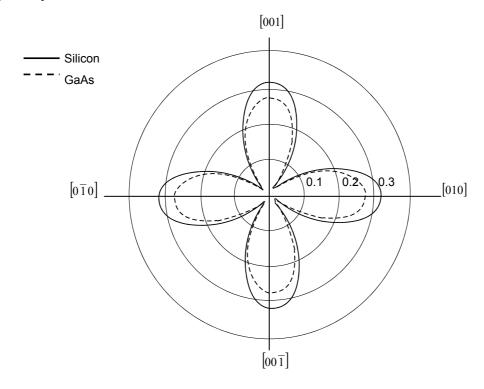

| Figure 5-4: Poisson's ratio as a function of angle in the (100) plane                         | 74 |

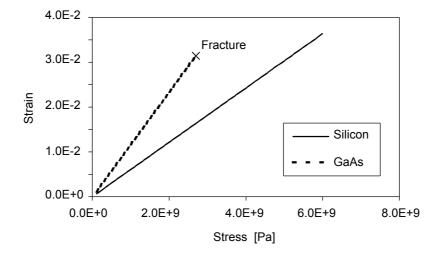

| Figure 5-5: Stress versus strain relationships for bulk Si and GaAs                           | 74 |

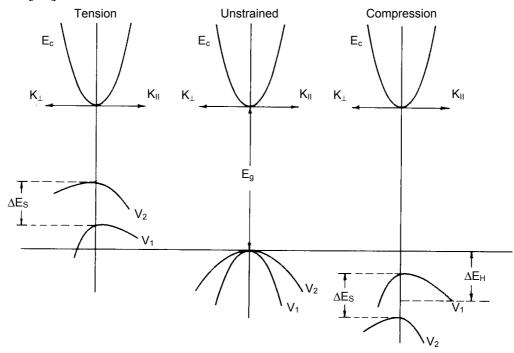

| Figure 5-6: The strain result in the modification of energy band structure in a semiconductor | 76 |

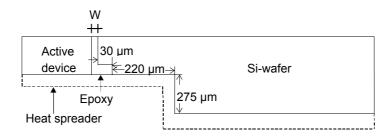

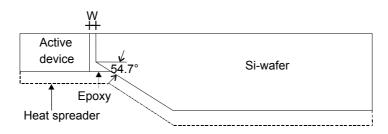

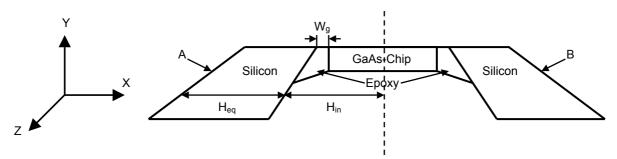

| Figure 5-7: Model of standard structure of the earlier concept of QMIT.                       | 80 |

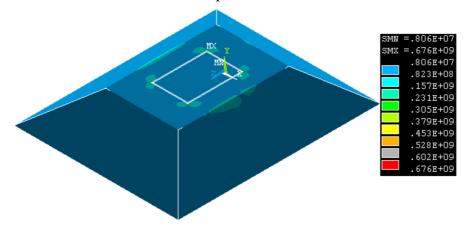

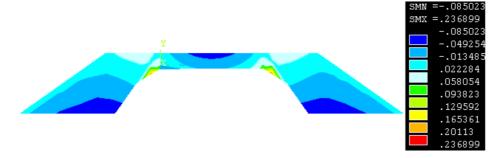

| Figure 5-8: Calculated thermo-mechanical stress in the standard structure                     | 81 |

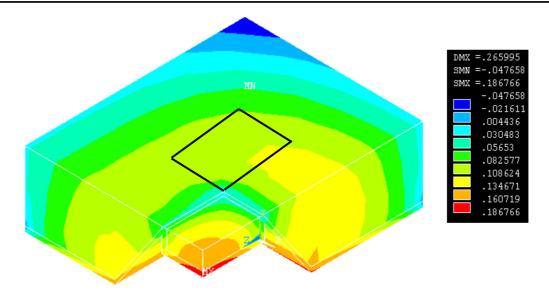

| Figure 5-9: Calculated Y component of displacement in the standard structure                  | 81 |

| Figure 5-10: Cross-section of the displacement simulation normal to Z-axis                    | 81 |

| Figure 5-11: Calculated displacement distribution in the plane normal to X-axis               | 81 |

| Figure 5-12: Calculated displacement distribution in the diagonal plane                       | 82 |

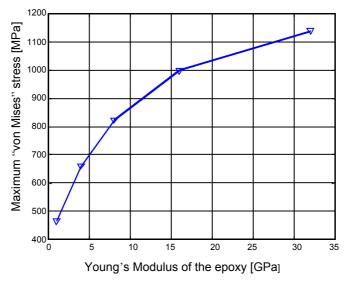

| Figure 5-13: Maximum "von Mises" stress as a function of the epoxy Young's modulus            | 82 |

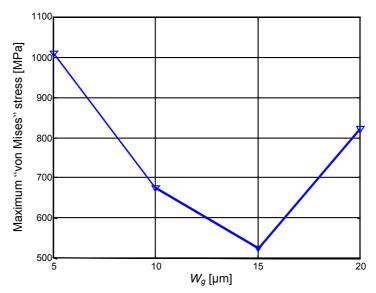

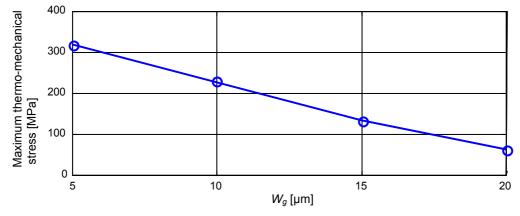

| <b>Figure 5-14:</b> Maximum "von Mises" stress as a function of $W_g$                         | 83 |

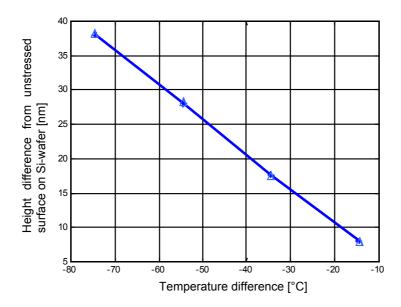

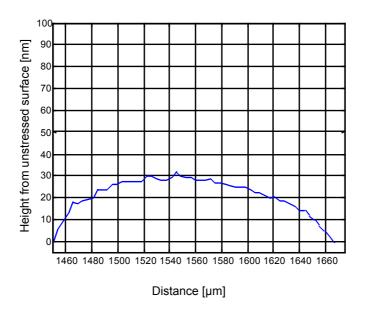

| Figure 5-15: Calculated maximum height difference from the unstressed in A-A direction        | 84 |

| Figure 5-16: Top-view of the microtest-fixture.                                               | 85 |

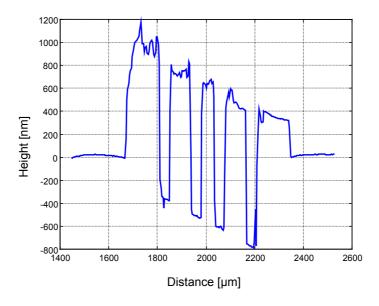

| Figure 5-17: Surface profile of the microtest-fixture along the A-A line using DEKTAK         | 85 |

| <b>Figure 5-18:</b> The left part of Fig. 5-17. $W_g = 10 \mu m$ and DT = -74.5 °C            | 85 |

| <b>Figure 5-19:</b> Surface mapping of the microtest-fixture with SPM. DT = 0 °C.             | 86 |

| <b>Figure 5-20:</b> Surface mapping of the microtest- fixture with SPM.DT = -74 °C.           | 86 |

| Figure 5-21: Cross-section of Fig. 5-19 along the C-C line.                                   | 86 |

| Figure 5-22: Cross-section of Fig. 5-20 along the C-C line.                                   | 86 |

| Figure 5-23: cross-section of Fig. 5-19 along the D-D line.                                   | 86 |

| Figure 5-24: Cross-section of Fig. 5-20 along the D-D line.                                   | 86 |

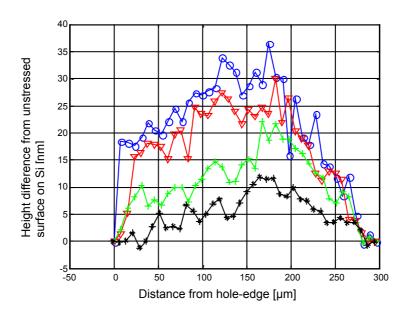

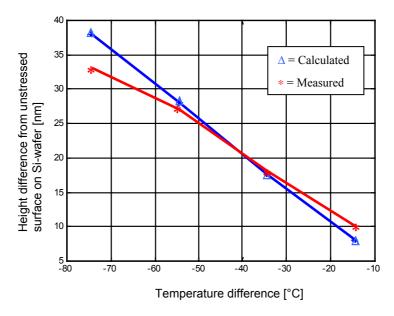

| Figure 5-25: Measured surface profile on the Si-wafer along A-A direction in Fig. 5-16        | 87 |

| Figure 5-26: Measured and calculated maximum height difference in A-A direction               | 87 |

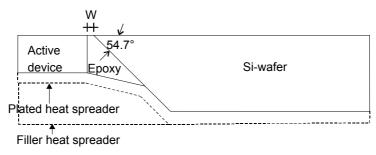

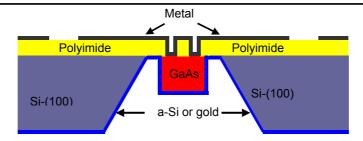

| Figure 5-27: Cross-section view of the fabricated microtest-fixture in the enhanced QMIT 89    |

|------------------------------------------------------------------------------------------------|

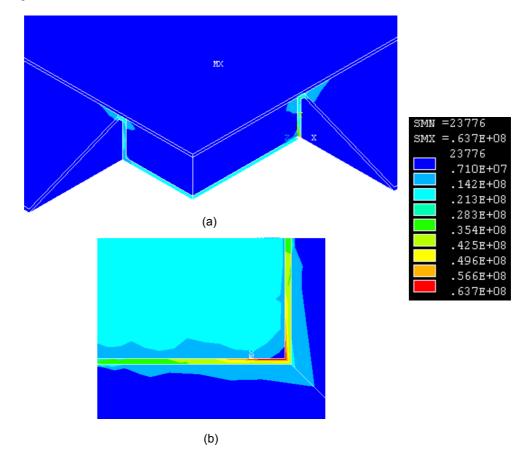

| Figure 5-28: (a) Thermo-mechanical stress distribution in the enhanced QMIT                    |

| Figure 5-29: Maximum "von Mises" thermo-mechanical stress in the enhanced QMIT89               |

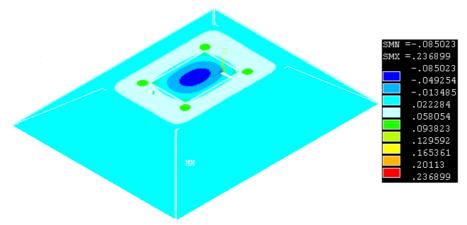

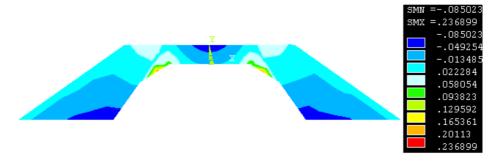

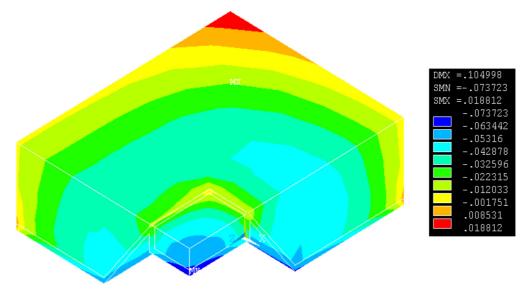

| <b>Figure 5-30:</b> Calculated Y component of the displacement at 22 °C                        |

| <b>Figure 5-31:</b> Calculated Y component of the displacement at 80 °C                        |

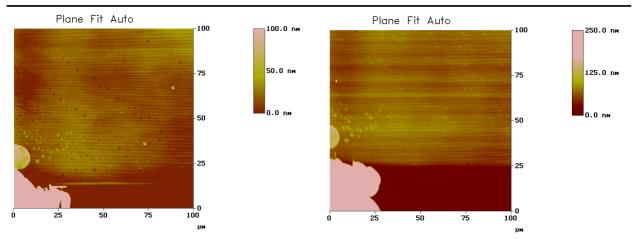

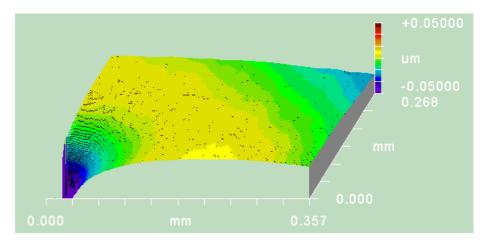

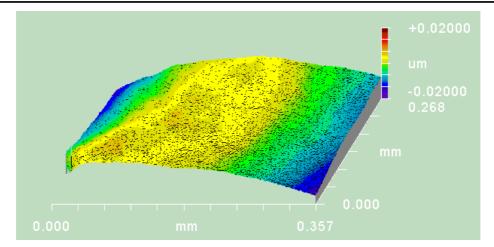

| <b>Figure 5-32:</b> White-light interferometery mapping of the silicon surface at 22 °C91      |

| <b>Figure 5-33:</b> White-light interferometery mapping of the silicon surface at 60 °C92      |

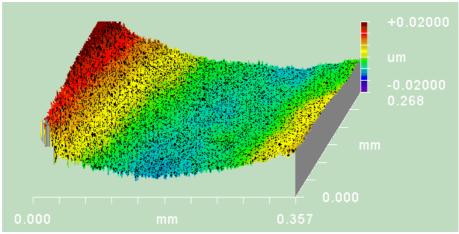

| <b>Figure 5-34:</b> White-light interferometery mapping of the silicon surface at at 80 °C92   |

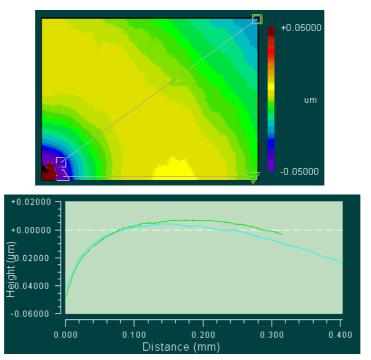

| <b>Figure 5-35:</b> Top view and cross-sections the measurement in Fig. 5-32.                  |

| <b>Figure 5-36:</b> The difference displacement versus the temperature of measurement93        |

| <b>Figure 6-1:</b> Sequence of stages in a typical design process                              |

| Figure 6-2: Structure of an multilayer perceptrons (MLP) type neural network (NN)              |

| Figure 6-3: TSE and penalty terms against number of neurons in the hidden layer                |

| Figure 6-4: MPSE as a function of number of neurons in the hidden layer and penalty factor.106 |

| <b>Figure 6-5:</b> P-HEM's S-parameters magnitudes by the neural model on a test-fixture       |

| <b>Figure 6-6:</b> P-HEMT's S-parameters phases by the neural model on a test-fixture          |

| <b>Figure 6-7:</b> Prediction of the magnitude of $S_{II}$ by neural model with 24 neurons     |

| Figure 6-8: P-HEMT's S-parameters magnitudes by the neural model the enhanced QMIT 110         |

# List of tables

| Table I: Properties of materials involved                                        | 30 |

|----------------------------------------------------------------------------------|----|

| Table II: Thermal conductivity and thermal expansion coefficients of Si and GaAs | 30 |

| Table III: Temperature dependent second order elastic constants of Si-(100)      | 30 |

| Table IV: Temperature dependent second order elastic constants of GaAs-(100)     | 30 |

# Frequently used nomenclatures

| Symbol                      | Meaning                                                                     | Unit                          |

|-----------------------------|-----------------------------------------------------------------------------|-------------------------------|

| α                           | Penalty factor                                                              | -                             |

| $oldsymbol{eta}_l$          | The smoothing factor in layer <i>l</i>                                      | -                             |

| $\Delta E_c$                | Conduction band discontinuity                                               | eV                            |

| $\Delta E_H$                | Band gap energy change related to hydrostatic strain                        | eV                            |

| $\Delta E_S$                | Band gap energy change related to shear strain                              | eV                            |

| $\Delta w_{pq,l}(n+1)$      | The change of weights between adjacent layers                               | -                             |

| $oldsymbol{\delta}_{q,l}$   | The error term of neuron $q$ between target and actual outputs of layer $l$ | -                             |

| $\mathcal{E}_{AlGaAs}$      | Dielectric constant of doped AlGaAs                                         | -                             |

| ${\cal E}$                  | Strain                                                                      | -                             |

| $\mathcal{E}_r$             | Dielectric constant                                                         | -                             |

| $\mathcal{E}_{rad}$         | Emissivity                                                                  | -                             |

| $\mathcal{E}_{radsolid}$    | Emissivity of solid                                                         | -                             |

| $\mathcal{E}_{r\sim GaAs}$  | Dielectric constant of GaAs                                                 | -                             |

| $\mathcal{E}_{r\sim GaAs0}$ | Dielectric constant of GaAs at 300 K                                        | -                             |

| $\pmb{\phi}_b$              | Schottky barrier energy                                                     | eV                            |

| $\Gamma$                    | Direct band in GaAs                                                         | -                             |

| $\Gamma_q$ or $\Gamma_T$    | Represent a surface                                                         | $m^2$                         |

| $\eta$                      | Learning rate                                                               | -                             |

| $oldsymbol{\eta}_l$         | The learning rate in layer <i>l</i>                                         | -                             |

| $\lambda(t)$                | Instantaneous failure rate                                                  | $s^{-1}$                      |

| ν                           | Poisson's ratio                                                             | -                             |

| θ, φ, ψ                     | Euler's angles                                                              | degree                        |

| $\rho$                      | Density                                                                     | kgm <sup>-3</sup>             |

| $ ho_c$                     | Conduction band density of states                                           | cm <sup>-3</sup>              |

| $\sigma$                    | Normal stress                                                               | MPa                           |

| $oldsymbol{\sigma}_0^2$     | Error variance                                                              | -                             |

| $\sigma_{\!F}$              | Fracture strength                                                           | MPa                           |

| $\sigma_{\!S\!B}$           | Stefan-Boltzmann's constant (5.669E-8)                                      | $\text{Wm}^{-2}\text{K}^{-4}$ |

| au                          | Shear stress                                                                | MPa                           |

| $	au_e$                     | Energy relaxation time                                                      | ns                            |

| $	au_m$                     | Momentum relaxation time                                                    | ns                            |

| $\overline{arOmega}$ | Represents a domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $m^3$   |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| A                    | Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $m^2$   |

| AFM                  | Atomic force microscopy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -       |

| Ag                   | Silver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -       |

| Al                   | Aluminum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -       |

| AlN                  | Aluminum nitride                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -       |

| ANN                  | Artificial neural network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -       |

| Au                   | Gold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -       |

| BCB                  | Benzocyclobutene                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -       |

| BeO                  | Beryllium oxide or beryllia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -       |

| BiCMOS               | Bipolar-complementary metal oxide semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -       |

| c                    | Specific heat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

| C                    | Compliance coefficient                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GPa     |

| CAD                  | Computer aided design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -       |

| $C_i$                | Correlation of the normalized drain and gate noise currents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -       |